# **UNIVERSIDADE FEDERAL DE SANTA CATARINA**

| HE   | EURÍSTI | CA DE PO | OWER-CAI | P EM SIST | TEMAS M | ULTICOF | RE DE |   |

|------|---------|----------|----------|-----------|---------|---------|-------|---|

| теме | O DEAL  | COMILIS  | O DE MOI | NITODAM   | ENTO DE | DEDEO!  |       | _ |

Leonardo Passig Horstmann

Florianópolis - SC

2018 / 2

# UNIVERSIDADE FEDERAL DE SANTA CATARINA DEPARTAMENTO DE INFORMÁTICA E ESTATÍSTICA CURSO DE CIÊNCIAS DA COMPUTAÇÃO

# HEURÍSTICA DE POWER-CAP EM SISTEMAS MULTICORE DE TEMPO-REAL COM USO DE MONITORAMENTO DE PERFORMANCE

#### Leonardo Passig Horstmann

Trabalho De Conclusão De Curso apresentado na Universidade Federal de Santa Catarina (UFSC) como parte dos requisitos para obtenção do grau de Bacharel em Ciências da Computação.

Florianópolis – SC

2018 / 2

Leonardo Passig Horstmann

HEURÍSTICA DE POWER-CAP EM SISTEMAS MULTICORE DE

TEMPO-REAL COM USO DE MONITORAMENTO DE PERFORMANCE

Trabalho De Conclusão De Curso apresentado na Universidade Federal de Santa

Catarina (UFSC) como parte dos requisitos para obtenção do grau de Bacharel em

Ciências da Computação.

Orientador: Prof. Dr. Antônio Augusto Fröhlich

INE / UFSC

Coorientador: Prof. Dr. Giovani Gracioli

ECE / UW

**Banca Examinadora**

Dr. Tiago Rogério Mück

ARM

Prof. Dr. Lucas Francisco Wanner

IDC / UniCamp

2

# SUMÁRIO

| LISTA DE FIGURAS                                     | 6        |

|------------------------------------------------------|----------|

| LISTA DE TABELAS                                     | 9        |

| LISTA DE REDUÇÕES                                    | 10       |

| RESUMO                                               | 11       |

| INTRODUÇÃO                                           | 12       |

| OBJETIVOS                                            | 14       |

| OBJETIVOS GERAIS                                     | 14       |

| OBJETIVOS ESPECÍFICOS                                | 14       |

| ORGANIZAÇÃO DO TEXTO                                 | 14       |

| FUNDAMENTAÇÃO TEÓRICA                                | 16       |

| EPOS                                                 | 16       |

| INTEL IA-32                                          | 16       |

| COMPUTAÇÃO MULTI-CORE                                | 17       |

| PMU                                                  | 18       |

| PMU NA ARQUITETURA SANDY BRIDGE                      | 19       |

| SISTEMAS DE TEMPO-REAL                               | 19       |

| TIPOS DE SISTEMAS DE TEMPO-REAL                      | 20       |

| ESCALONADORES DE TEMPO REAL                          | 21       |

| RM - RATE MONOTONIC                                  | 21       |

| EDF – EARLIEST DEADLINE FIRST                        | 22       |

| POWER-CAP POWER-CAPPING EM HARDWARE E INTERFACE RAPL | 22       |

| DVS E MODULAÇÃO DE CLOCK                             | 23<br>24 |

| MODULAÇÃO DE CLOCK POR DUTY CYCLE                    | 24<br>24 |

| NÃO INTRUSIVIDADE                                    | 26       |

| DATA MINING                                          | 27       |

| WEKA                                                 | 27       |

| MATERIAIS UTILIZADOS                                 | 28       |

| IMPLEMENTAÇÃO                                        | 29       |

| LEITURA DE TEMPERATURA                               | 29       |

| MODULAÇÃO DE CLOCK                                   | 30       |

| MEDIÇÃO DE CONSUMO DE ENERGIA DO PROCESSADOR         | 30       |

| SISTEMA NÃO INTRUSIVO DE CAPTURAS                    | 33       |

| ESTRUTURA DE ARMAZENAMENTO                           | 34       |

| NÃO INTRUSIVIDADE                                    | 36       |

| VERIFICAÇÃO DA NÃO INTRUSIVIDADE                     | 37       |

| ANEXOS                                                                                    | 105      |

|-------------------------------------------------------------------------------------------|----------|

| BIBLIOGRAFIA                                                                              | 100      |

| TRABALHOS FUTUROS                                                                         | 98       |

| CONCLUSÃO                                                                                 | 98       |

| DESEMPENHO COM HEURÍSTICA DESABILITADA DESEMPENHO COM HEURÌSTICA HABILITADA E COMPARATIVO | 80<br>85 |

| MÉTODO DE AFERIÇÃO ENERGÉTICA                                                             | 80       |

| TASK-SETS UTILIZADOS                                                                      | 79       |

| RESULTADOS                                                                                | 79       |

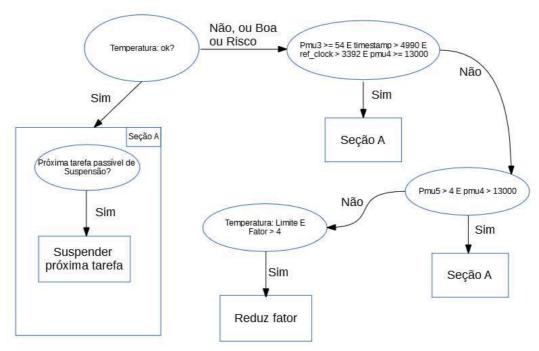

| IMPLEMENTAÇÃO BASEADA NA ÁRVORE DE DECISÃO                                                | 71       |

| LÓGICA DE DESVIO DE ESCALONAMENTO                                                         | 71       |

| LÓGICA DE REDUÇÃO DE FREQUÊNCIA DE OPERAÇÃO (DVS)                                         | 70       |

| SUSPENSÃO CONTROLADA DE TAREFAS                                                           | 69       |

| AÇÕES DE CONTROLE                                                                         | 69       |

| DESENVOLVIMENTO DA HEURÍSTICA                                                             | 69       |

| GERAÇÃO DE ÁRVORES                                                                        | 61       |

| PREPARAÇÃO E DEFINIÇÃO DE CLASSES                                                         | 60       |

| USO DE CLASSIFICADORES E ÁRVORES DE DECISÃO                                               | 60       |

| DEFINIÇÃO DO POWER-CAP                                                                    | 59       |

| LEVANTAMENTO DE CORRELAÇÕES                                                               | 56       |

| TRANSFORMAÇÃO DOS DADOS                                                                   | 55       |

| INTEGRAÇÃO DE DADOS                                                                       | 54       |

| LIMPEZA DE DADOS                                                                          | 53       |

| SELEÇÃO DE DADOS                                                                          | 53       |

| PREPARAÇÃO                                                                                | 53       |

| PERFIL TÉRMICO E TTV                                                                      | 50       |

| ESTIMATIVA DE CONSUMO<br>TDP                                                              | 48<br>50 |

| ANÁLISE                                                                                   | 47       |

| CAPTURA DE DADOS                                                                          | 46       |

| DEFINIÇÃO DOS TASK-SETS E DAS OPERAÇÕES EXECUTADAS                                        | 43       |

| CAPTURA E ANÁLISE DOS DADOS                                                               | 43       |

| SISTEMA INTERNO                                                                           | 41       |

| SISTEMA EXTERNO                                                                           | 41       |

| METADADOS DE ENVIO                                                                        | 40       |

| ENVIO PARA O BANCO                                                                        | 40       |

| CONFIGURAÇÃO DOS EVENTOS PMU                                                              | 39       |

| ESCALONADORES PARA MONITORAMENTO                                                          | 38       |

|                                                                                           |          |

| A1. TABELA DE EVENTOS INTEL SANDY BRIDGE NO EPOS      | 105 |

|-------------------------------------------------------|-----|

| A2. CÓDIGO DO SISTEMA DE MONITORAMENTO DE PERFORMANCE | 119 |

| A3. CÓDIGO DA HEURÍSTICA DESENVOLVIDA                 | 161 |

| A4. ARTIGO PADRÃO SBC                                 | 179 |

# LISTA DE FIGURAS

| Figura 2.1 - Exemplo de <i>Layout</i> de um MSR                                      | 18 |

|--------------------------------------------------------------------------------------|----|

| Figura 2.2 - Layout do registrador MSR_PKG_POWER_LIMIT                               | 23 |

| Figura 2.3 - Layout do MSR IA32_CLOCK_MODULATION                                     | 25 |

| Figura 2.4 - Descrição dos <i>Duty Cycles</i>                                        | 25 |

| Figura 3.1 - Divisão de componentes utilizada pela Interface RAPL                    | 30 |

| Figura 3.2 - Layout do registrador MSR_RAPL_POWER_UNIT                               | 31 |

| Figura 3.3 - Layout do MSR para leitura dos dados energéticos do Package             | 32 |

| Figura 3.4 - Layout dos MSRs de leitura dos componentes PP0 e PP1                    | 32 |

| Figura 3.5 - Estrutura de um Moment                                                  | 34 |

| Figura 3.6 - Estrutura de Armazenamento                                              | 35 |

| Figura 4.1 - Diagrama de montagem do circuito de medição - Fluke                     | 48 |

| Figura 4.2 a) - Perfil Térmico do Processador Intel® Core™ i7-2600                   | 51 |

| <b>Figura 4.2 b)</b> - Variação de Psi-CA para vários T <sub>AMBIENT</sub>           | 52 |

| Figura 4.3 - Aplicação do algoritmo CorrelationAttributeEval sobre dados capturados. | 56 |

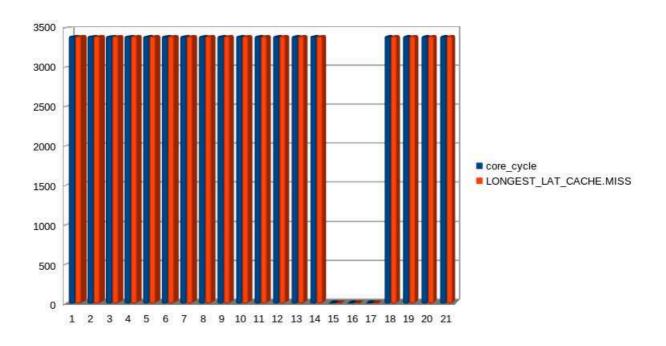

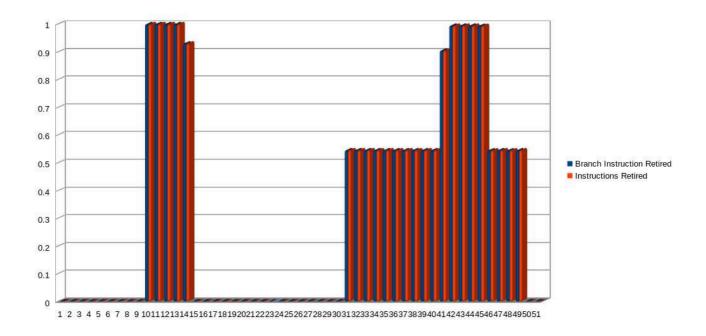

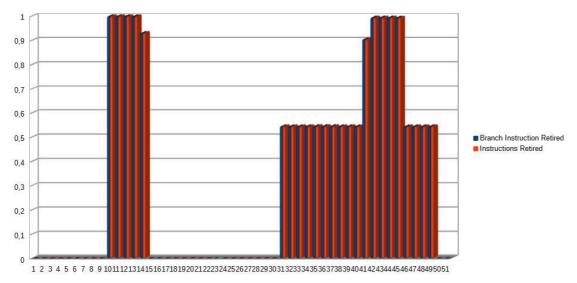

| Figura 4.4 a) - Exemplo de evento ignorado por semelhança ao UnHalted Cycles         | 58 |

| Figura 4.4 b) - Exemplo de evento ignorado por semelhança ao Instructions Retired    | 59 |

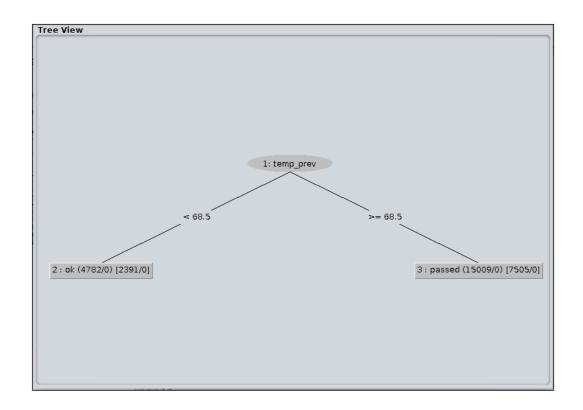

| Figura 4.5 a) - Árvore de decisão simples - Descrição Textual                        | 62 |

| Figura 4.5 b) - Árvore de decisão simples - Descrição Gráfica                        | 62 |

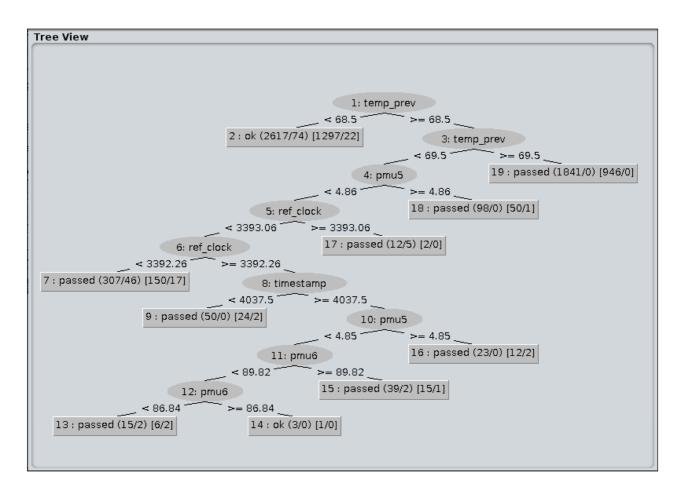

| Figura 4.6 a) - Árvore de decisão processo 2 - Representação Textual       | 63 |

|----------------------------------------------------------------------------|----|

| Figura 4.6 b) - Árvore de decisão processo 2 - Representação Gráfica       | 64 |

| Figura 4.7 - Árvore de decisão utilizada - Descrição Textual Completa      | 65 |

| Figura 4.8 - Árvore de decisão utilizada - Descrição Textual Sintetizada   | 67 |

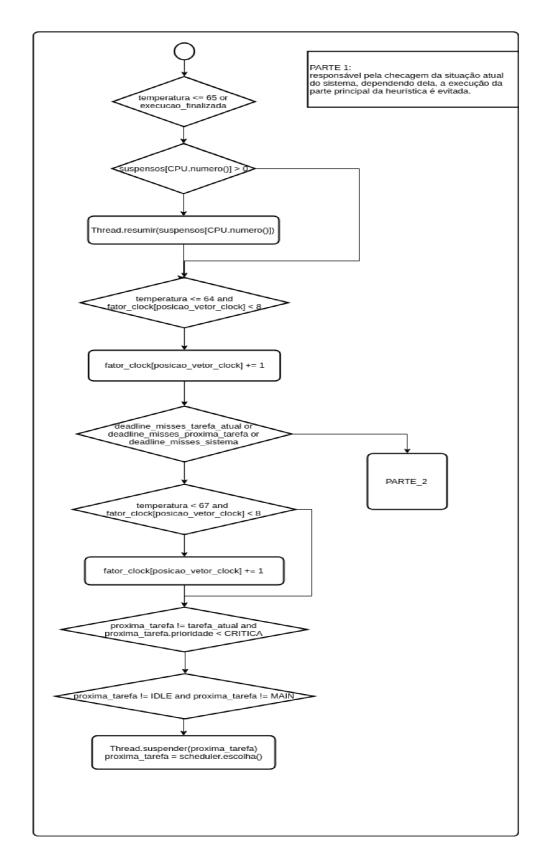

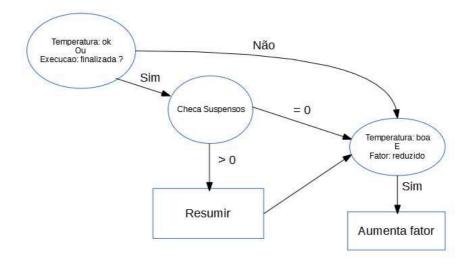

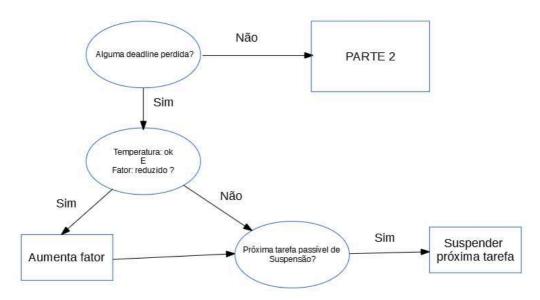

| Figura 5.1 a) - Pseudocódigo da heurística - parte dispatch                | 72 |

| Figura 5.1 b) - Diagrama de fluxo de execução - Parte 1                    | 75 |

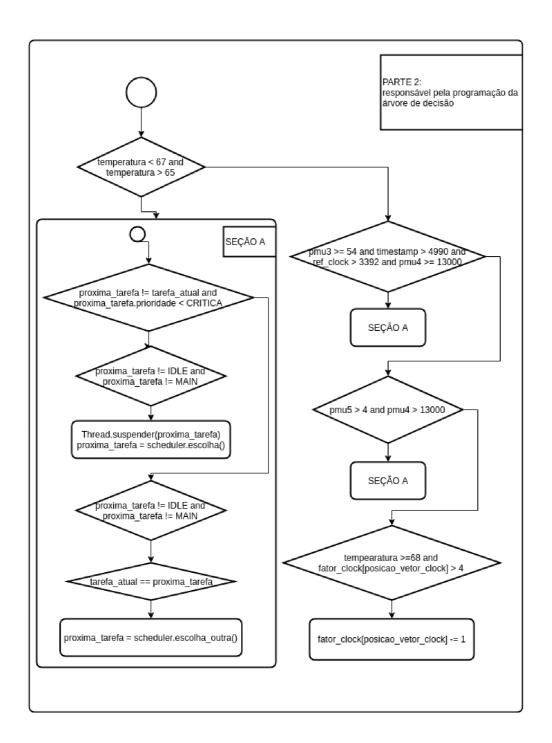

| Figura 5.1 c) - Diagrama de fluxo de execução - Parte 2                    | 76 |

| Figura 5.1 d) - Pseudocódigo da heurística - parte idle                    | 78 |

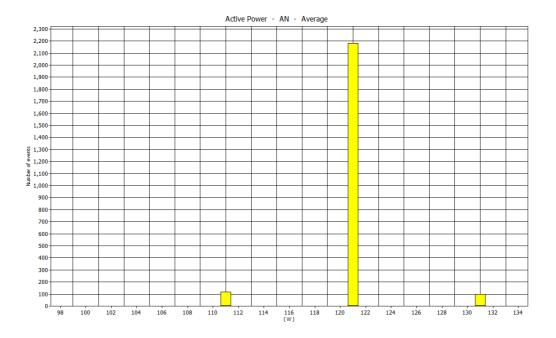

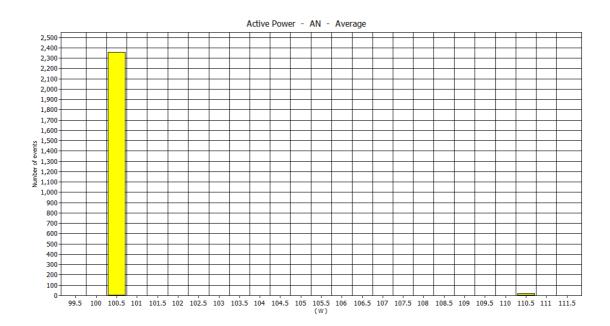

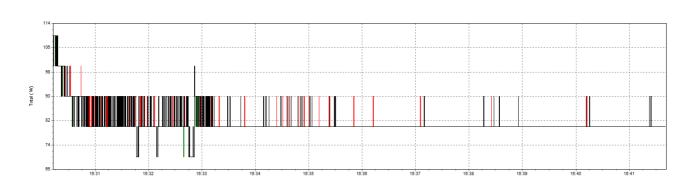

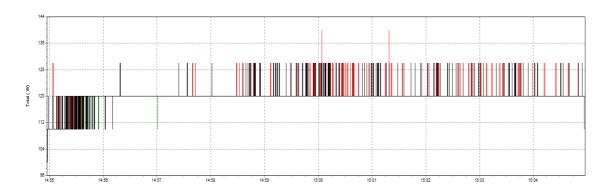

| Figura 6.1 - Histograma de consumo - Operações recursivas                  | 81 |

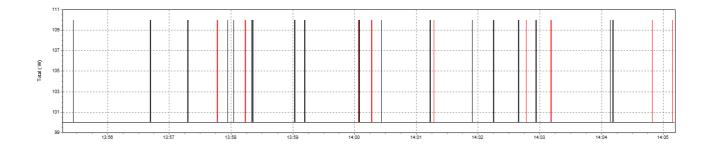

| Figura 6.2 - Frequências de consumo - Operações recursivas                 | 81 |

| Figura 6.3 – Sumário de consumo - Operações recursivas                     | 82 |

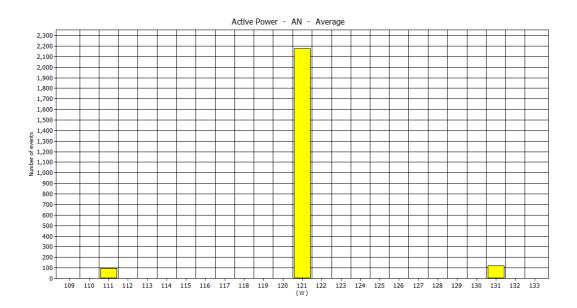

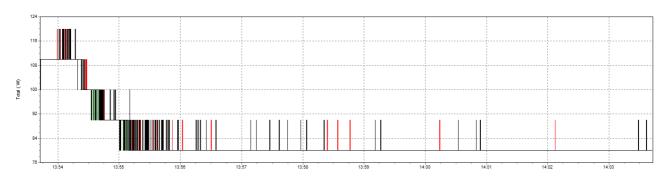

| Figura 6.4 - Histograma de consumo - Operações iterativas                  | 82 |

| Figura 6.5 - Frequências de consumo - Operações iterativas                 | 83 |

| Figura 6.6 – Sumário de consumo - Operações iterativas                     | 83 |

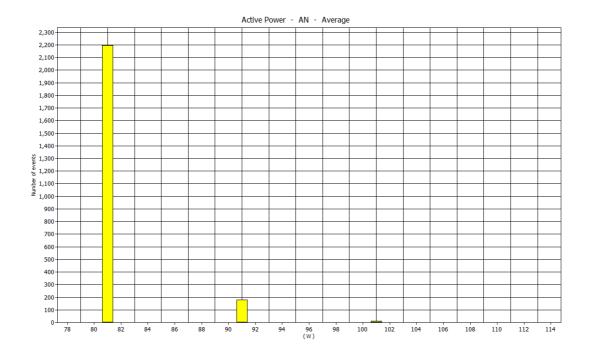

| Figura 6.7 - Histograma de consumo - Operações em memória                  | 84 |

| Figura 6.8 - Frequências de consumo - Operações em memória                 | 84 |

| Figura 6.9 - Sumário de consumo - Operações em memória                     | 85 |

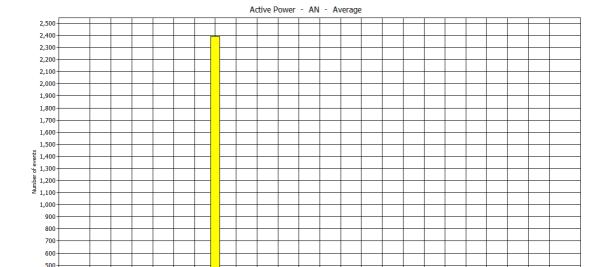

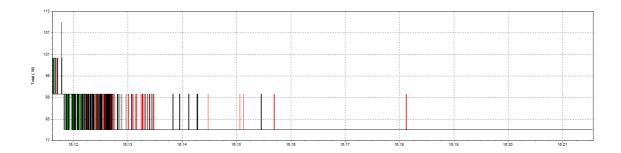

| Figura 6.10 - Histograma de consumo - operações recursivas com heurística  | 86 |

| Figura 6.11 - Frequências de consumo - operações recursivas com heurística | 86 |

| Figura 6.12 - Sumário de consumo - operações recursivas com heurística87     |

|------------------------------------------------------------------------------|

| Figura 6.13 - Histograma de consumo - operações em memória com heurística88  |

| Figura 6.14 - Frequências de consumo - operações em memória com heurística89 |

| Figura 6.15 - Sumário de consumo - operações em memória com heurística89     |

| Figura 6.16 - Histograma de consumo - operações em memória com heurística90  |

| Figura 6.17 - Frequências de consumo - operações em memória com heurística90 |

| Figura 6.18 - Sumário de consumo - operações em memória com heurística91     |

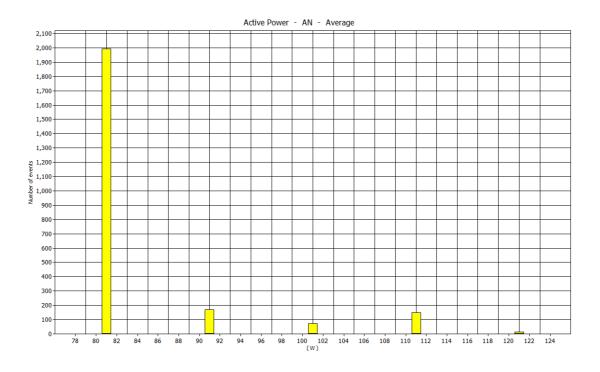

| Figura 6.19 - Histograma de consumo - operações iterativas com heurística92  |

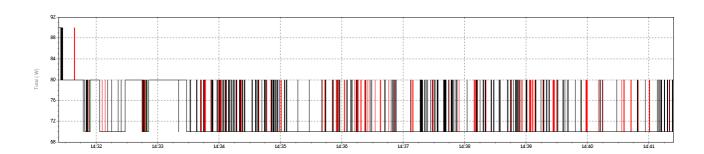

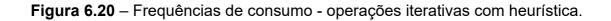

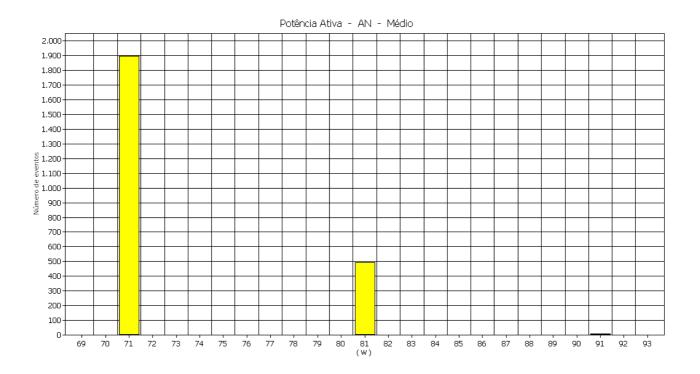

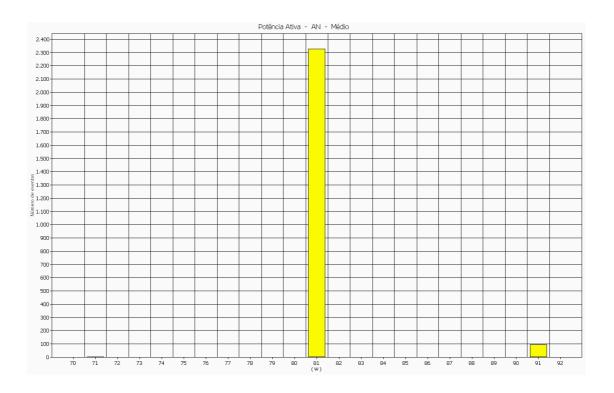

| Figura 6.20 - Frequências de consumo - operações iterativas com heurística93 |

| Figura 6.21 - Sumário de consumo - operações iterativas com heurística93     |

| Figura 6.22 - Histograma de consumo - operações recursivas com heurística94  |

| Figura 6.23 - Frequências de consumo - operações recursivas com heurística94 |

| Figura 6.24 - Sumário de consumo - operações recursivas com heurística95     |

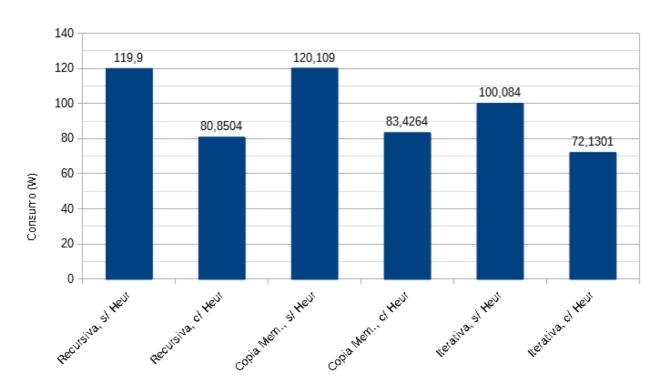

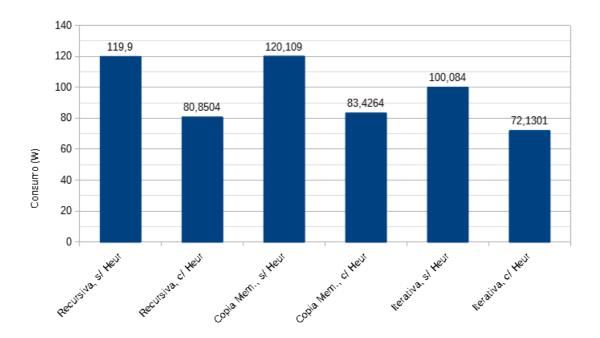

| Figura 6.25 - Consumos Médios Sob Conjunto de Tarefas 297                    |

# LISTA DE TABELAS

| Tabela 3.1 - Conjunto de Tarefas Utilizado para os testes de não intrusividade | 37 |

|--------------------------------------------------------------------------------|----|

| Tabela 4.1 - Conjunto de tarefas 1                                             | 43 |

| Tabela 4.2 - Conjunto de tarefas 2                                             | 44 |

| Tabela 4.3 - Conjunto de tarefas 3                                             | 45 |

| Tabela 4.4 - Uso de cada CPU nos Conjuntos de Tarefas 1, 2 e 3                 | 45 |

| Tabela 4.5 - Tabela de principais correlações                                  | 57 |

| Tabela 4.6 - Mapeamento de eventos                                             | 65 |

# LISTA DE REDUÇÕES

MSR Model Specific Register

PMU Performance Monitoring Unit

PMC Performance Monitoring Counter

EPOS Embedded Parallel Operating System

LISHA Laboratório de Integração de Software e Hardware

#### **RESUMO**

Com a crescente no uso de sistemas embarcados e dispositivos móveis alimentados a bateria e o aumento do poder computacional e das necessidades dos mesmos, têm-se feito cada vez mais necessário o estudo de técnicas para melhor utilização dos recursos energéticos de modo a maximizar o tempo de funcionamento de um sistema. Uma das alternativas para uma melhor exploração da fonte energética é a aplicação de Power-Cap, limitando o consumo energético de maneira a não extrapolar o nível desejado. O uso de Power-Cap em sistemas de Tempo-Real, no entanto, deve levar em conta a existência de tarefas críticas que não devem perder seus tempos limite para execução (deadlines). Para se obter dados que possam atestar a necessidade de tomada de ação para que o consumo não extrapole o limite estabelecido, uma das alternativas é a aplicação de monitoramento de performance, outra área que vem ganhando grande importância nos dias de hoje. Tendo em vista este cenário, o presente Trabalho de Conclusão de Curso implementou um sistema, não intrusivo, de monitoramento de performance e estudou eventos de Software e Hardware coletados, desenvolvendo uma heurística de Power-Cap para um sistema Multi-Core de Tempo-Real.

**Palavras chave:** Multicore, Energy-Aware, DVS, PMU, Monitoramento, Tempo-Real, Power-Cap.

# 1 INTRODUÇÃO

Nos dias de hoje, os dispositivos móveis e sistemas embarcados, que, em sua maioria, operam tendo como fonte de alimentação uma bateria, representam a maior parte dos sistemas computacionais desenvolvidos. Isto traz à tona, ainda mais, a importância da aplicação de Power-Cap (Tampa de Energia ou, em outras palavras, um limite máximo para consumo energético).

Existem basicamente duas maneiras de se aplicar Power-Capping, a primeira delas busca uma abordagem a nível de Software e a segunda delas a nível de Hardware. Segundo Zhang e Hoffmann (2016), as abordagens de Software apresentam flexibilidade, permitindo a coordenação de múltiplos recursos de hardware, porém apresentam lentidão para alcançar o objetivo, requerendo muito tempo para convergir para o Power-Cap. Abordagens de Hardware, por sua vez, tendem a convergir muito rapidamente, mas controlam apenas voltagem e frequência de operação, limitando assim a performance num todo.

Dentre as opções para Power-Capping a nível de Software, destacam-se o controle da frequência de clock (modulação de clock) através de DVS e o desenvolvimento de estratégias de escalonamento focadas no consumo energético (power-aware).

Seguindo a ideia de ZHANG, LANG, PAKIN e FU (2014), o desenvolvimento de escalonadores de tarefas paralelas focados em consumo energético tem sido reconhecido como uma demanda para a computação de alto desempenho (high performance computing - HPC).

Ainda neste cenário, o uso de técnicas de DVS tende a aumentar a duração e a vida útil de suas baterias, uma vez que, conforme frizado por Islam e Lin (2017), dentre os vários componentes num dispositivo computacional, o processador é um dos maiores consumidores de energia, sendo sua performance diretamente relacionada com sua dissipação energética, e consome aproximadamente de 18% a 30% de toda energia consumida pelo dispositivo.

Por outro lado, o monitoramento de performance tem tomado um importante papel no que se refere, principalmente, a predição de eventos, permitindo operar o mecanismo de DVS no melhor momento. Mück, Sarma e Dutt (2015), ao descreverem o modelo "Run-DMC: Runtime Dynamic Heterogeneous Multicore Performance and Power Estimation for Energy Efficiency", previam uma etapa de coleta de dados (por eles chamada de "sensing"), na qual eram realizadas leituras de contadores de performance de Hardware (HPCs - Hardware Performance Counter).

No modelo proposto, bem como no presente trabalho, as coletas de dados eram realizadas na ordem de trocas de contexto, de modo a ser possível manter as métricas de performance separadas por threads.

Tendo em mente o desenvolvimento já feito, o foco do presente trabalho é se utilizar de um sistema operacional embarcado de baixa interferência (EPOS) para coletar dados de execução provenientes da Unidade de Monitoramento de Performance da Intel (Performance Monitoring Unit - PMU), tornando possível o correlacionamento dos diferentes contadores de performance e a busca de novas variáveis de interesse para o desenvolvimento de Heurísticas de Power-Cap para sistemas Multi-Core de Tempo-Real.

#### 1.1. OBJETIVOS

Tendo em vista o foco determinado para o trabalho, foram estabelecidos os seguintes objetivos gerais e específicos

#### 1.1.1. OBJETIVOS GERAIS

Utilizando o sistema operacional EPOS, desenvolvido pelo LISHA, funcionando em uma arquitetura Intel IA-32 em um servidor fornecido pelo laboratório, em modo Bare Metal, coletar dados provindo de contadores de performance durante a execução do sistema, a fim de aplicar algoritmos de Data Mining para obtenção de correlações entre os dados que descrevam situações durante a execução e, a partir da análise feita, desenvolver uma heurística de Power-Cap para sistemas Multi-Core de Tempo-Real.

#### 1.1.2. OBJETIVOS ESPECÍFICOS

- Desenvolver, em conjunto com o discente José Luis Conradi Hoffmann, de matrícula 15100745, um sistema não intrusivo de captura de dados de monitoramento de performance em tempo de execução e um sistema de envio para o banco de dados inteligentes de IoT Lisha (iot.lisha.ufsc.br);

- Utilizar táticas de Data Mining para validar os dados capturados e encontrar uma correlação entre os mesmos;

- Desenvolver uma heurística de Power-Cap utilizando as variáveis correlacionadas.

# 1.2. ORGANIZAÇÃO DO TEXTO

As seções a seguir separam o conteúdo do presente trabalho em:

- Fundamentação Teórica: onde são apresentados os principais conceitos necessários para o entendimento do trabalho;

- Implementação: contém os detalhes do desenvolvimento do sistema de monitoramento de performance não intrusivo;

- Captura e Análise de Dados: descreve o processo de coleta, separação e análise dos dados, além das técnicas utilizadas;

- Desenvolvimento da Heurística: descreve os processos que levaram da análise realizada ao código da heurística;

- Resultados: Relata os aspectos referentes ao desempenho da heurística;

- Conclusão do Trabalho;

- Referências Bibliográficas.

# 2 FUNDAMENTAÇÃO TEÓRICA

A presente seção tem como objetivo descrever os conceitos e conhecimentos utilizados para o desenvolvimento deste trabalho, tais como o sistema EPOS, a arquitetura IA-32, o conceito de sistemas não intrusivos, alguns aspectos importantes da computação de Tempo-Real, os conceitos de Power-Cap e DVS e uma introdução a PMU.

#### 2.1. **EPOS**

EPOS [1], ou Sistema Operacional Paralelo Embarcado (*Embedded Parallel Operating System*), é um sistema operacional desenvolvido no Laboratório de Integração Software/Hardware - LISHA [2].

O EPOS conta com o Método de Design de Sistemas Embarcados Dirigido à Aplicação (ADESD), proposto pelo professor Antônio Augusto Fröhlich, para guiar o desenvolvimento de componentes de software e hardware, que podem ser adaptados automaticamente para atender aos requisitos de aplicações específicas [3].

O sistema operacional EPOS pode ser configurado para executar tanto em um processador Intel, quanto em um processador ARM. Neste trabalho estaremos focados em sua versão para Intel IA-32, executando os testes em modo bare-metal, a qual presta suporte aos recursos, aqui necessários.

#### 2.2. INTEL IA-32

A arquitetura Intel IA-32, também conhecida como i386, é a versão 32 bits do conjunto de instruções x86 (x86 instruction-set architecture), implementada pela primeira

vez nos microprocessadores Intel 80386 em 1985, sendo a primeira implementação de x86 a suportar 32-bits.

Nesta arquitetura, eram disponibilizados modo de operação protegido, modelo de memória segmentada, paginação, suporte para estágios paralelos e um barramento com suporte para 4-Gbytes de memória física.

A Intel, por questões de compatibilidade, manteve intacto o conjunto de instruções, sendo assim, os novos processadores continuam tendo suporte para as instruções utilizadas, apesar do ganho de desempenho.

# 2.3. COMPUTAÇÃO MULTI-CORE

Existem duas abordagens, básicas, de computação Multi-Core, a primeira é o paralelismo físico, também conhecido como chip multi-processador (CPM) onde o paralelismo é explorado em hardware, no caso, se tem mais de um Core físico dentro de uma mesma unidade de processamento (CPU). Neste tipo de paralelização, cada Core é um processador completo, e as diferenças quanto a um processador single Core são vistas, por exemplo, no caso das abordagens quanto a Cache.

A segunda opção é o paralelismo explorado logicamente, esta abordagem leva o nome de hyperthreading, introduzido pela Intel no processador Pentium 4, que, de uma maneira simples, permite que a CPU manter o estado de duas diferentes threads e fazer switchs entre elas na escala de nano-segundos. Num exemplo, se um dos processos precisa fazer uma leitura de uma palavra da memória [13], uma CPU com multithread pode fazer a troca pela outra thread para ganhar em paralelismo.

Um aspecto importante é que o hyperthreading não traz um paralelismo real, uma vez que apenas uma thread está executando num instante de tempo. Por outro lado, para o sistema operacional, cada thread aparece como uma diferente CPU.

#### 2.4. PMU

O monitoramento de performance foi introduzido pela Intel nos processadores Pentium, com um conjunto de contadores de monitoramento de performance específicos (model-specific performance-monitoring counter – MSRs). Estes contadores permitiam a seleção de parâmetros de performance dos processadores para serem monitorados e medidos [4].

Figura 2.1 – Exemplo de *Layout* de um MSR.

Fonte: Intel® 64 and IA-32 Architectures Software Developer's Manual (2018)

As novas gerações de processadores da Intel suportam uma gama maior de eventos de performance arquiteturais e não-arquiteturais.

Eventos de performance arquiteturais: esta classe suporta amostragem de eventos por contagem e interrupção (dado um valor, cada vez que o contador alcança este, uma interrupção é disparada). O comportamento visível desta classe de eventos é consistente entre as diferentes implementações de processadores;

Eventos de performance não-arquiteturais: também suporta amostragem de eventos por contagem e interrupção, porém, os eventos desta classe variam de um modelo de processador para outro. São específicos da microarquitetura.

#### 2.4.1. PMU NA ARQUITETURA SANDY BRIDGE

A versão arquitetural da PMU utilizada durante o desenvolvimento e os testes (vide tópico 2.10) é a Sandy Bridge (suportada, também, pelo EPOS). Nesta versão, são suportados 3 canais fixos (*Instructions Retired, CPU Clock Unhalted e CPU Clock Unhalted Ref-TSC* [4]) 8 configuráveis por core (4 por thread), possuindo os eventos típicos da versão arquitetural 3, somados aos eventos não-arquiteturais disponíveis apenas para a versão Sandy Bridge.

Além das configurações básicas, a PMU em sua versão Sandy Bridge conta com os recursos PEBS, PDIR, PMI e contagem Any-Thread. Estes recursos não serão explorados no presente trabalho.

A descrição da versão arquitetural 3 da PMU pode ser encontrada na seção 18.2.3 do manual de desenvolvedores da Intel [4] e a descrição dos eventos não-arquiteturais da microarquitetura Sandy Bridge é acessível na seção 19.6 do mesmo manual.

#### 2.5. SISTEMAS DE TEMPO-REAL

Sistemas de Tempo-Real são sistemas utilizados em sistemas de controle críticos, que dependem de resposta em tempo hábil e dos resultados computados para funcionar

corretamente. Estes sistemas diferem dos demais pelo fato de reagirem a eventos do mundo físico dentro de um certo período de tempo [9].

Em um sistema de Tempo-Real, as tarefas (tasks) possuem algumas propriedades que ajudam a sua compreensão e execução [10]:

- Tempo de Liberação (Release Time): Tempo requerido para que qualquer thread esteja pronta;

- Deadline: Tempo no qual cada tarefa deve ser completada depois da sua liberação;

- WCET (Worst Case Execution Time): Maior tempo necessário para concluir uma tarefa com sucesso sob parâmetros críticos e injustos do sistema;

- Tempo de execução (Run Time): Tempo necessário, sem interrupções, para completar uma tarefa depois de sua liberação.

#### 2.5.1. TIPOS DE SISTEMAS DE TEMPO-REAL

A perda de uma deadline não é desejável em um sistema de Tempo-Real. Mas existem diferentes tipos de sistemas de Tempo-Real e, em cada um deles as perdas de deadlines tem diferentes consequências:

Sistema de Tempo-Real Crítico (Hard Real-Time System): Neste sistema, as

deadlines (limites temporais) são estáticas e não mudam em nenhuma

circunstância. A saída deste sistema é zero se a execução não for

completada com sucesso dentro do tempo limite [10] e o atraso não é aceito.

Muitas vezes este tipo de sistema lida com a vida humana e atrasos podem

acarretar em catástrofes;

Sistema de Tempo-Real Não-Crítico (Soft Real-Time System): Sistema no qual as deadlines são dinâmicas e podem ser flexíveis, assim as tarefas podem ser completadas com sucesso [10].

#### 2.5.2. ESCALONADORES DE TEMPO REAL

Para sistemas de Tempo-Real simples, a resposta é rápida o suficiente. Contudo, para muitos sistemas de Tempo-Real, mais complexos, é necessário uma coordenação sofisticada, e obter respostas rápidas o bastante torna-se um desafio [9].

Existem dois tipos básicos de escalonadores de Tempo-Real, os escalonadores de Prioridade Estática, nos quais as prioridades das tarefas variam durante a execução do sistema, e os de Prioridade Dinâmica, cujas prioridades são constantes.

# 2.5.2.1 RM - RATE MONOTONIC

Escalonador de prioridade fixa. Segue a filosofia de que as prioridades mais altas são atribuídas as tarefas de maior frequência. O escalonador sempre escolhe para execução a tarefa de maior prioridade. Conforme cresce o número de tarefas a escalonar, a escalabilidade deste algoritmo tende a 69% [9], isto é, a maior porcentagem de uso sem perda deadline é de 69% a partir de um determinado número de tarefas.

Um teste possível para a escalabilidade deste algoritmo é checar a sentença lógica Un < Wn, onde:

Un é a utilização e pode ser calculado como o somatório das taxas de uso de cada tarefa. Imaginando que cada tarefa i tenha período Ti e WCET Ci, Un = Somatório (i = 1.. n) { Ci / Ti };  Wn é a escalabilidade máxima para o número n de tarefas, podendo ser calculado por: n\*(2<sup>1/n</sup> – 1).

#### 2.5.2.2 EDF - EARLIEST DEADLINE FIRST

Escalonador de prioridade dinâmica. Usa a abordagem de que as tarefas com a deadline mais próxima devem receber maior prioridade. Esta abordagem tende a zerar o tempo de idle do processador, podendo alcançar 100% de uso. Contudo, o EDF apresenta uma limitação pela não-possibilidade de se prever a tarefa que falhará durante um overload momentâneo [9].

Um teste simples de escalabilidade é:

Somatório de (Ci / Ti) ≤ 1, tomando Ci como o WCET de uma tarefa i e Ti como o período desta tarefa.

#### 2.6. POWER-CAP

Power-Cap ou tampa de energia consiste em determinar um limite máximo de consumo de energia para a execução de um sistema [21]. As opções para aplicação de Power-Cap (power-capping) usam abordagens de Software e Hardware.

As abordagens de Software apresentam flexibilidade, permitindo a coordenação de múltiplos recursos de hardware, porém apresentam lentidão para alcançar o objetivo, requerendo muito tempo para convergir para o Power-Cap. Abordagens de Hardware, por sua vez, tendem a convergir muito rapidamente, mas controlam apenas voltagem e frequência de operação, limitando assim a performance num todo [22].

#### 2.6.1. POWER-CAPPING EM HARDWARE E INTERFACE RAPL

Conforme já citado, um dos caminhos para aplicação Power-Cap é em nível de Hardware. Esta configuração pode ser realizada, na arquitetura Intel IA32, através da interface RAPL.

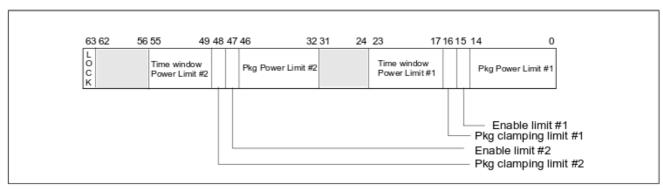

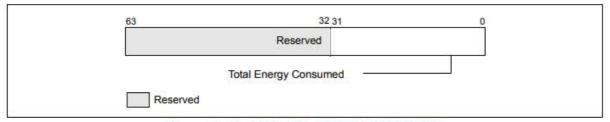

Segundo o "Manual de Desenvolvedores de Software das Arquiteturas IA32 e Intel® 64" [4], fornecido pela Intel, em seu tópico 14.9.3 "Package RAPL Domain" (página 3189), a interface RAPL fornece o registrador MSR\_PKG\_POWER\_LIMIT, que permite, ao software, definir uma limitação de consumo para o domínio do "pacote" ("package" é a região de Hardware onde estão agrupados componentes como o processador, a cache e a placa de vídeo integrada).

Ainda seguindo a definição presente no manual, este limite é dado na forma de consumo médio em Watts sobre uma janela de tempo definida no mesmo registrador. O recurso permite a configuração de dois limites a serem aplicados em duas janelas de tempo diferentes, conforme apresentado na Figura 2.2.

**Figura 2.2** – *Layout* do registrador *MSR\_PKG\_POWER\_LIMIT*,

Figure 14-36. MSR\_PKG\_POWER\_LIMIT Register

Fonte: Intel® 64 and IA-32 Architectures Software Developer's Manual (2018)

Em alguns processadores, a interface permite configuração de limites específicos de memória RAM e para o processador, sendo possível, ainda, ler status de consumo específico para cada componente e do pacote como um todo, levando em consideração as unidades de medida utilizadas para o modelo.

# 2.7. DVS E MODULAÇÃO DE CLOCK

Dynamic Voltage and Frequency Scaling (DVS ou DVFS), ou Escalonamento Dinâmico de Voltagem e Frequência, é aceito como uma técnica para reduzir potência e consumo de energia de microprocessadores [11].

# 2.7.1. MODULAÇÃO DE CLOCK POR DUTY CYCLE

A Intel define modulação de clock como um segundo método de controle térmico disponível para os processadores. Esta modulação é efetuada desligando e ligando o clock rapidamente em duty cycle (ciclos "ocupados") e pode resultar em reduções de até 50% na dissipação de calor (aplicando duty cycle de 30-50%) [20, Thermal Guide. 6.2.2.2 - Clock Modulation].

Segundo a definição da Intel [4, seção "14.7 THERMAL MONITORING AND PROTECTION", página 3177], "duty cycle" não se refere ao ciclo de trabalho real do sinal de clock, e sim ao período de tempo durante o qual o sinal de clock pode acionar o chip do processador. Usando o mecanismo de parada do clock para controlar com que freqüência o processador é "cronometrado" (recebe os sinais do clock), o consumo de energia do processador pode ser modulado.

Ainda segundo a Intel, os processadores a partir do Pentium 4, Intel Xeon e Pentium M apresentam suporte para modulação de clock controlada por software, permitindo que o sistema operacional implemente uma política de redução de consumo de

energia dos processadores [4, seção "14.7.3 Software Controlled Clock Modulation", páginas 3179 e 3180].

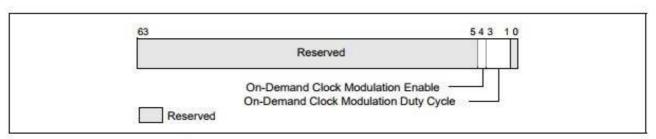

O controle de modulação de clock é exercido através de escritas no MSR IA32\_CLOCK\_MODULATION, conforme Figura 2.3 e a descrição abaixo da mesma.

Figura 2.3 – Layout do MSR IA32\_CLOCK\_MODULATION,

Figure 14-25. IA32\_CLOCK\_MODULATION MSR

Fonte: Intel® 64 and IA-32 Architectures Software Developer's Manual (2018)

- On-Demand Clock Modulation Enable, bit 4 Habilita o controle de software de modulação de clock por demanda quando em 1 e o desabilita quando 0.

- On-Demand Clock Modulation Duty Cycle, bits 1 through 3 Seleciona o duty

cycle da modulação de clock por demanda (ver Figura 2.4). Esse campo só é válido

quando o bit 4 (descrito acima) esta habilitado.

Figura 2.4 – Descrição dos Duty Cycles

Table 14-3. On-Demand Clock Modulation Duty Cycle Field Encoding

| Duty Cycle Field Encoding | Duty Cycle      |  |

|---------------------------|-----------------|--|

| 000B                      | Reserved        |  |

| 001B                      | 12.5% (Default) |  |

| 010B                      | 25.0%           |  |

| 011B                      | 37.5%           |  |

| 100B                      | 50.0%           |  |

| 101B                      | 63.5%           |  |

| 110B                      | 75%             |  |

| 111B                      | 87.5%           |  |

Fonte: Intel® 64 and IA-32 Architectures Software Developer's Manual (2018)

É importante ressaltar que em sistemas multicore, cada core controla seu duty cycle, porém quando se usa a tecnologia de hyperthreading, o duty cycle do core físico será configurado para o valor mais alto entre as threads.

#### 2.8. NÃO INTRUSIVIDADE

A não intrusividade na computação é tratada como a capacidade de um sistema, ou aplicação, de executar minimizando o seu impacto sobre o desempenho do resto do sistema. Segundo Harelick e Stoyen (1999), um sistema de monitoramento não intrusivo, deve respeitar o Princípio de Heisenberg, descrito por Rosenberg (1996) como a garantia de que o processo monitor não afete o comportamento do processo monitorado.

Ainda conforme Harelick e Stoyen (1999), um sistema de monitoramento em Tempo-Real deve cumprir com objetivos severos. A instrumentação não pode fazer com que as tarefas percam suas deadlines e não deve requerer recompilação, além de que, talvez, o monitor pode ter a necessidade de operar sobre os dados antes de imprimí-los.

#### 2.9. DATA MINING

Data Mining, ou mineração de dados, é o nome dado a todo processo de se aplicar uma metodologia baseada na computação, incluindo novas técnicas, para extrair conhecimento de um conjunto de dados [15].

Ainda segundo Kantardzic [15], Data Mining é um processo interativo no qual cada progresso é definido por descobertas, por métodos manuais ou automáticos, sendo que o seu uso é mais útil num cenário de análise exploratória onde não se tem ideias premeditadas do que seria uma saída interessante.

São dois os objetivos primários da aplicação de Data Mining:

- Predição: com intuito de produzir um modelo do sistema descrito pelo conjunto de dados;

- Descrição: com intuito de produzir informação nova e não trivial sobre os dados.

Para alcançar tais objetivos usam-se métodos de mineração de dados para agrupamento (clusterização ou clustering), que consiste em separar registros em grupos, associação, que é utilizado para identificar atributos (ocorrências) que se relacionam com um determinado atributo (evento), e, ainda, classificação, que é utilizado para identificar a qual conjunto de categorias/classes pertence um determinado evento.

#### 2.9.1.WEKA

Weka (Waikato Environment for Knowledge Analysis - Ambiente para Análise de Conhecimento da Waikato) é uma coleção de algoritmos de aprendizado de máquina (machine learning) para tarefas de mineração de dados, disponibilizado gratuitamente pela Waikato University, da Austrália.

Estão disponíveis, no Weka, ferramentas para preparação de dados, classificação, regressão, agrupamento (clustering), associação e visualização [25].

#### 2.10. MATERIAIS UTILIZADOS

Para execução do presente trabalho foram utilizados os seguintes equipamentos:

- Computador equipado com um processador Intel Core i7-2600 @3.4GHz [19], memória RAM de 4GB DDR3 @1333MHz, placa mãe PCWARE IPMH61R3, com fonte de alimentação ALLIED SL-8180 BTX instalado sob corrente de 220V, disponibilizado pelo laboratório (LISHA) para captura de dados e testes das heurísticas.

- Analisador de potência e qualidade de energia Fluke 435 series II [24], para aferições de consumo energético.

O computador utilizado pertence à segunda geração dos processadores Intel Core i7, com arquitetura Sandy Bridge.

# 3 IMPLEMENTAÇÃO

Esta seção tem como objetivo expor os sistemas desenvolvidos durante a execução do projeto, envolvendo toda a parte de captura dos dados, armazenamento, impressão, transformação/formatação, envio e busca. Esta etapa do trabalho foi desenvolvida em conjunto com o discente José Luis Conradi Hoffmann, de matrícula 15100745, também aluno deste mesmo curso.

Uma descrição mais detalhada da implementação, contendo parte do estudo feito e algumas conclusões que levaram a mudanças e evoluções que trouxeram o sistema até o estado atual, pode ser encontrada em *"Performance Monitoring with EPOS"* [7].

#### 3.1. LEITURA DE TEMPERATURA

De acordo com o manual de desenvolvedores da Intel [4], na arquitetura IA-32, a temperatura de um processador pode ser lida usando o MSR IA32\_THERM\_STATUS. No tópico 14.7.5.2 "Reading the Digital Sensor" (2018, vol 3B, capítulo 14, p. 2697), foi definido o seguinte método para leitura do valor da temperatura:

Primeiramente, é preciso lembrar que, diferentemente de um leitor analógico de temperatura, a saída do sensor térmico digital é uma temperatura relativa a máxima temperatura permitida para operação do processador:

- Digital Readout (bits 22:16, RO) Leitura da temperatura digital em 1 grau

Celsius relativos ao temperatura de ativação do TCC (Thermal Control

Circuitry circuito de controle térmico).

- 0: Temperatura de ativação do TCC;

- 1: (Ativação do TCC 1), etc.

Neste sentido, a leitura de um valor baixo do campo Digital Readout (bits 22:16) indica uma temperatura, que na verdade, é alta.

# 3.2. MODULAÇÃO DE CLOCK

O modelo de modulação de clock implementado segue a descrição do tópico 2.7.1, se utilizando da técnica de duty cycle. O método foi implementado no EPOS especificamente para cpus Intel IA32, sendo que foi optado por utilizar o modelo geral, com variações de 12.5%, não se valendo da extensão para controle com granularidade de 6,25% por questões de garantia de compatibilidade com outros modelos de processadores.

Um aspecto importante a se ressaltar é a thread (tarefa) que executa o método de modulação de clock aplica o duty cycle na cpu sobre a qual está executando.

# 3.3. MEDIÇÃO DE CONSUMO DE ENERGIA DO PROCESSADOR

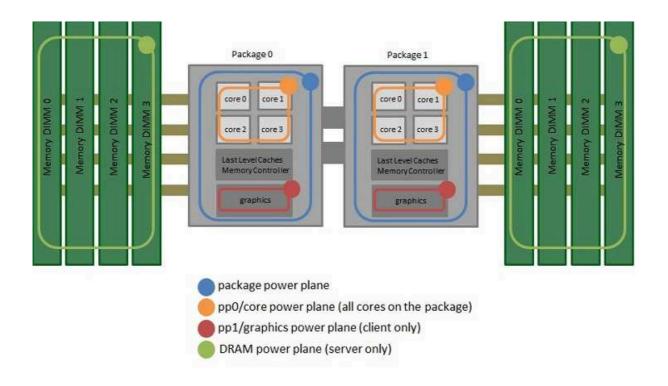

Para além da possibilidade de se aferir consumo com uso de ferramentas externas, é possível, ainda, nos processadores Intel, utilizar os registradores da interface RAPL [4], para efetuar "medições" do consumo de forma mais específica. A interface provê suporte para leitura do consumo do pacote (*PKG*), e dos componentes internos ao mesmo (Figura 3.1) e, também, o consumo energético da DRAM.

**Figura 3.1** – Divisão de componentes utilizada pela Interface RAPL.

Fonte: Intel® Power Governor (2012) [23].

O suporte as medidas, no entanto, varia de acordo com a versão arquitetural do processador. A versão arquitetural Sandy Bridge (utilizada neste trabalho), por exemplo, possui suporte apenas para informações de consumo no nível de PKG, PP0 e PP1 (http://web.eece.maine.edu/~vweaver/projects/rapl/rapl\_support.html). Vale ressaltar que o EPOS não inicializa o componente gráfico integrado, não tendo, portanto, suporte ao PP1.

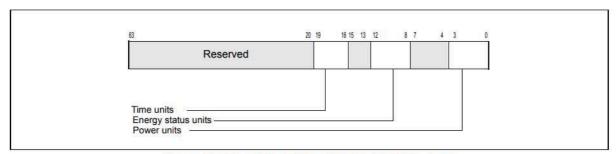

Figura 3.2 - Layout do registrador MSR RAPL POWER UNIT.

Figure 14-31. MSR\_RAPL\_POWER\_UNIT Register

Fonte: Intel® 64 and IA-32 Architectures Software Developer's Manual (2018)

Figura 3.3 – Layout do MSR para leitura dos dados energéticos do Package.

Figure 14-33. MSR\_PKG\_ENERGY\_STATUS MSR

Fonte: Intel® 64 and IA-32 Architectures Software Developer's Manual (2018)

Figura 3.4 – Layout dos MSRs de leitura dos componentes PP0 e PP1.

Figure 14-37. MSR\_PPO\_ENERGY\_STATUS/MSR\_PP1\_ENERGY\_STATUS MSR

Fonte: Intel® 64 and IA-32 Architectures Software Developer's Manual (2018)

Conforme o manual da Intel, o procedimento para aferir consumo energético do Pacote ("Package" ou "PKG"), ou de um de seus componentes, consiste em ler, do registrador referente ao componente a ser aferido, (Figuras 3.3 e 3.4) os 32 bits menos significativos e multiplicar pela unidade de contagem (u), valor calculado a partir dos bits 8 a 12 do registrador MSR\_RAPL\_POWER\_UNIT (Figura 3.2), pela fórmula: u = 1/2<sup>ENERGY\_STATUS\_UNIT.</sup> O resultado deste cálculo será o valor energético em Joules. Para obter o consumo em Watts, basta dividir o valor encontrado na operação pelo tempo de execução em segundos (Watts = Joules/s).

Uma importante observação é que o valor lido pelos registradores de contagem são referentes ao período desde a última vez que a contagem foi reiniciada, este momento é chamado pela Intel de wraparound (14.9.3 Package RAPL Domain - [4]). A Intel prevê um tempo de 60s para o wraparound quando a carga de trabalho (workload) é alta, mas o tempo pode aumentar conforme a carga diminui. Ainda segundo o manual, as atualizações do valor do registrador são esperadas serem feitas a cada 1 milissegundo.

No EPOS foram implementados apenas os códigos de leitura dos registradores e separação dos valores para unidade e consumo. Os valores de consumo podem ser calculados após a execução, através do log que imprime as capturas.

### 3.4. SISTEMA NÃO INTRUSIVO DE CAPTURAS

Uma captura tem como objetivo gravar informações do sistema em um determinado momento. Tais informações podem vir a ser utilizadas para uma análise detalhada de uma execução e do comportamento do Software e do Hardware.

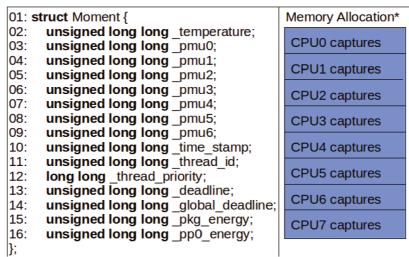

Ao efetuar uma captura, o "Momento" atual do sistema é armazenado. Este momento é composto pelo *timestamp* da leitura, a temperatura, os três canais fixos da PMU, os quatro configuráveis, o id, a prioridade e o número de *deadline misses* da thread (que está executando ou passará a executar), o número de *deadline misses* em todo o sistema, o valor do contador de energia do package (pacote onde se encontra os cores e a cache) e contador de energia dos cores.

Para lidar com tais variáveis, foi escolhida uma *struct* em C++ (Figura 3.5), composta por 15 variáveis, que por sua vez, descrevem o momento atual do sistema operacional e do Hardware, de acordo com os critérios configurados na inicialização (canais da PMU monitorados).

Figura 3.5 – Estrutura de um Moment

```

struct Moment {

unsigned long long temperature;

unsigned long long _pmu0;

unsigned long long _pmu1;

unsigned long long _pmu2;

unsigned long long _pmu3;

unsigned long long pmu4;

unsigned long long _pmu5;

unsigned long long _pmu6;

unsigned long long _time_stamp;

unsigned long long _thread_id;

long long thread priority;

unsigned long long local_deadline_miss;

unsigned long long _global_deadline_miss;

unsigned long long _pkg_energy;

unsigned long long _pp0_energy;

};

```

As capturas ocorrem sempre que é executado o *dispatch* de uma thread, ou seja, quando uma troca de contexto acontece, ou quando há uma solicitação de execução feita por uma tarefa periódica.

É importante ressaltar que as leituras feitas dos registradores da PMU e de temperatura estão relacionados diretamente ao *Core* que executa o código.

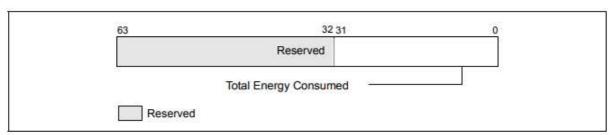

#### 3.4.1. ESTRUTURA DE ARMAZENAMENTO

Dentre as opções disponíveis para armazenar as capturas (buffer consumido em determinados momentos - idle, por exemplo - ou armazenamento total dos dados), a escolha foi por armazenar todas as capturas de uma execução em memória, sem o consumo desses dados até que o sistema finalize sua execução.

A região alocada para o armazenamento foi separada em um vetor de vários elementos da *struct Moment* (ver Figura 3.5). O vetor em questão divide igualmente o

espaço alocado entre todas as CPU's, onde cada uma escreve na sua respectiva "faixa", essa divisão vai da CPU 0 até a CPU 7 (Figura 3.6). Esta divisão ocorre, desta forma, devido ao fato de a máquina disponibilizada para executar os testes ter 8 *Cores* lógicos.

Figura 3.6 – Estrutura de Armazenamento

Cada *Moment* ocupa 120 bytes (15 \* o tamanho de um long long na arquitetura IA32 = 15 \* 8), sendo assim, o vetor deve ter no mínimo 8 \* 120 = 960 bytes (um *moment* por CPU). Após alguns testes, encontrou-se um valor máximo de 64000 capturas por CPU em testes com elevado número de troca de contexto e com período de execução de dois minutos.

Sendo assim, o vetor foi configurado para o tamanho de aproximadamente 61 MB (61440000 B = 61.440000 MB), o que, por sua vez, exigiu um aumento no tamanho padrão da *Heap* do EPOS (configurada no traits da aplicação, arquivo onde são configurados aspectos do programa a ser compilado usando técnica de metaprogramação estática).

### 3.4.2. NÃO INTRUSIVIDADE

Um dos principais requisitos do sistema de capturas, é que ele não gere interferências no desempenho do sistema como um todo, ou seja, o tempo final da execução deve ser, idealmente, o mesmo do que quando o sistema operacional executa sem o sistema de capturas habilitado. Todavia, manter exatamente o mesmo tempo de execução é impossível, uma vez que, naturalmente, foram adicionadas instruções ao código e, portanto, existe uma pequena tolerância (na grandeza de microsegundos).

Com o objetivo de dar ao sistema uma característica de não intrusão, é necessário uma boa escolha quanto a onde, e quando, as capturas e a inicialização dos componentes ligados a elas devem ocorrer. Com este objetivo, foi realizado um estudo (leitura da documentação e do código) sobre a inicialização e funcionamento do sistema EPOS.

A partir dos resultados dos estudos, foram delimitados locais específicos para realizar estas operações, garantindo um impacto baixíssimo no desempenho do sistema. Sendo assim, o sistema de capturas é inicializado juntamente ao SO, mais especificamente ao inicializar as primeiras threads (idle), evitando qualquer impacto sobre a execução das aplicações. Sobre a questão de quando capturar, foi selecionado o instante da troca de contexto, a fim de evitar uma nova interrupção no sistema.

Outro ponto importante era armazenar as capturas de forma rápida, dado o fato de que as execuções podem gerar um grande volume de dados, deixando inviável realizar a impressão dos dados na tela ou enviá-los via porta serial durante a execução (algo que poderia ocorrer se o buffer alocado fosse menor do que o número de dados alocados, o que geraria a necessidade de esvaziá-lo durante a execução), pois mesmo isso sendo

realizado em um período de *idle* do sistema, dependendo da utilização do task-set sendo executado, pode não haver tempo suficiente para o consumo dos dados sem que ocorra perda.

O paralelismo de escrita também foi focado na implementação, pois se o recurso utilizado não for cercado por uma tranca, as impressões se misturam quando duas ou mais CPUs estão realizando esta tarefa. Logo, deve ser alocado um espaço em memória com capacidade para armazenar todas as capturas durante a execução.

## 3.4.2.1 VERIFICAÇÃO DA NÃO INTRUSIVIDADE

Para avaliar a não intrusividade do sistema, foi realizado uma comparação de uma execução com e sem o sistema de monitoramento de performance, sendo os tempos analisados medidos ao início e fim da execução do código da aplicação que coordena as tarefas executadas. A verificação apresentou um aumento de aproximadamente 0.000002% em relação a execução com o sistema desabilitado (segundo taskset apresentado na Tabela 3.1, com 15 tarefas projetadas para o escalonador C-EDF). Seguem os cálculos efetuados:

- Tempo de execução sem o sistema de Monitoramento = 122122579 us;

- Tempo de execução com o sistema de Monitoramento = 122122803 us;

- Diferença = 224 us = 0.000224 seg = 0.000001834%.

**Tabela 3.1** – Conjunto de Tarefas Utilizado para os testes de não intrusividade.

| Período (us) | Deadline (us) | WCET (us) | CPU (Cluster) |

|--------------|---------------|-----------|---------------|

| 4000         | 4000          | 435       | 0             |

| 14000        | 14000         | 1084      | 0             |

| 20000        | 20000         | 1094      | 0             |

| 5000  | 5000  | 84   | 0 |

|-------|-------|------|---|

| 23000 | 23000 | 2377 | 1 |

| 31000 | 31000 | 2513 | 1 |

| 25000 | 25000 | 1849 | 1 |

| 25000 | 25000 | 2547 | 2 |

| 22000 | 22000 | 1838 | 2 |

| 20000 | 20000 | 1277 | 2 |

| 30000 | 30000 | 440  | 2 |

| 15000 | 15000 | 1425 | 3 |

| 6000  | 6000  | 556  | 3 |

| 22000 | 22000 | 1018 | 3 |

| 23000 | 23000 | 810  | 3 |

#### 3.4.3. ESCALONADORES PARA MONITORAMENTO

Como já citado, as inicializações dos componentes ligados ao sistema de captura foram feitas juntamente a inicialização do sistema. Para concretizar a inicialização da PMU, portanto, foi adicionada uma chamada de método na inicialização das primeiras threads do sistema.

Tal método foi implementado, originalmente vazio, dentro dos escalonadores, criando uma pequena modificação na estrutura já existente. Assim, para habilitar um escalonador ao monitoramento da PMU, basta preencher este método com os comandos de inicialização e configuração. Além disso, um dos objetivos da implementação era que o monitoramento pudesse ser facilmente ativado ou desativado. Para isso, optou-se por

adicionar uma variável de checagem a ser alterada dentro do método citado, ao qual foi atribuído o nome de init.

Para diferenciar os escalonadores nos quais o método init contém a configuração e inicialização da PMU e a atribuição de valor verdade para variável condiciona, os que foram configurados segundo esse princípio foram renomeados para M<nome do escalonador>.

Todo o código de monitoramento usa estruturas de checagem e, portanto, desativá-lo significa apenas mudar o escalonador no traits antes da compilação, ou simplesmente alterar o valor verdade da variável que libera o monitoramento.

O procedimento citado acima, não altera o funcionamento dos escalonadores, e poderia ser sido replicado em qualquer outro escalonador, a separação foi feita apenas com o intuito de ressaltar as diferenças da configuração padrão do sistema para a configuração para o processo do sistema de monitoramento de performance.

## 3.4.4. CONFIGURAÇÃO DOS EVENTOS PMU

A partir das configurações citadas no tópico acima, quando um critério de escalonamento que habilita o monitoramento é inicializado (configurados até agora são MGEDF, MCEDF e MPEDF), ele habilita a flag de monitoramento do sistema, além de configurar e inicializar os canais de monitoramento da PMU.

Para selecionar quais canais configuráveis serão monitorados durante a presente execução, uma variável estática foi definida na própria classe PMU do EPOS, com a função de definir a posição do evento escolhido no *enum* presente na classe.

Visando facilitar a configuração do sistema para execuções de testes em batch (lote), foi adotado como padrão que a variável definida na classe PMU representa apenas a posição do primeiro evento. Como consequência disso, ao configurar a PMU na

inicialização do escalonador, se inicializam os eventos configuráveis a partir da posição descrita pela variável da classe PMU e as 3 posições seguintes no vetor.

#### 3.4.5. ENVIO PARA O BANCO

Como já descrito, um dos objetivos desta implementação, era que os dados capturados fossem enviados para plataforma IoT da UFSC. Para tanto foram analisadas as seguintes possibilidades:

- Envio em tempo real:

- envio do dado assim que capturado;

- o bufferização dos dados para envio em intervalos;

- Envio após execução;

Com a análise das opções e dos impactos de cada uma, e buscando manter a ideia de um sistema de monitoramento com o mínimo possível de jitter/interferência na execução (não intrusividade), foi escolhida a estratégia de envio após a execução.

Partindo da escolha do método de envio, foi implementado um conjunto de aplicações para administrar o funcionamento do EPOS, além de algumas funções para impressão de dados dentro do próprio SO.

#### 3.4.5.1 METADADOS DE ENVIO

O envio dos dados para IoT segue uma estrutura definida por series e smartdatas, na qual as series representam a série temporal sob a qual os dados estarão associados, e as smartdatas representam os dados em si, juntamente com alguns metadados inerentes a eles, que ajudam na identificação da series a qual está associado [6].

A partir disto, são necessários alguns dados do sistema, além dos capturados, para executar o envio a plataforma IoT UFSC [5], são eles:

- Id's das threads configuradas no teste;

- Series a serem criadas (são geradas antes da execução pois contém os timestamps inicial e final);

- Lista de units (unit é um dos parâmetro das series) utilizadas (varia conforme configuração dos eventos não estáticos);

- Timestamps iniciais e finais.

Destes, os únicos que dependem da execução das tasks e, portanto, são impressos após a execução, são os id's das threads.

#### 3.4.5.2 SISTEMA EXTERNO

Visando enviar os dados capturados, é necessário, primeiramente, um algoritmo para monitorar a execução do EPOS e salvar o conteúdo impresso em um arquivo, doravante chamado de log, através da leitura constante de uma porta serial durante a execução.

Após o término da execução é preciso, então, de um algoritmo capaz de ler o log e organizar os dados e metadados de maneira a poder realizar o envio das series e das smartdatas.

Por fim para o envio das series e smartdatas são necessários scripts configurados conforme a plataforma.

#### 3.4.5.3 SISTEMA INTERNO

Para possibilitar o envio dos dados, capturados durante a execução, para IoT, foram necessárias as implementações de funções para impressão dos dados, em si, e de alguns metadados para facilitar o processo de envio.

Tendo em mente as questões ligadas ao funcionamento e ao desempenho do sistema, o melhor lugar para realizar a impressão dos metadados e dados relacionados a execução era após a conclusão da mesma, enquanto os dados e metadados independentes da execução são impressos antes do início da execução das tasks. Logo, o único impacto durante a execução é o do processo de captura.

A partir disso, o sistema começa esta etapa de impressão logo após perceber o fim da execução da última thread que, no EPOS, acontece na primeira verificação feita ao entrar em idle, antes do comando que ordena o desligamento do computador.

### 4 CAPTURA E ANÁLISE DOS DADOS

A partir da implementação realizada, foram iniciados os processos de captura de dados, onde foi testados *task-sets* (conjuntos de tarefas) com diferentes operações explorando operações com inteiros e pontos flutuantes, de modo recursivo e iterativo, e leituras consecutivas de vetores aleatórios em memória) em busca de variáveis que pudessem embasar a escolha de eventos para o desenvolvimento da heurística.

## 4.1. DEFINIÇÃO DOS TASK-SETS E DAS OPERAÇÕES EXECUTADAS

A geração dos conjuntos de tarefas a serem utilizados para captura dos dados foi feita com o auxílio do conceito de particionamento de tarefas para escalonadores Multi-Core de tempo real descrito por Gracioli em Real-Time Operating System Support for Multicore Applications (2014) [27].

Os conjuntos de tarefas gerados consideraram o escalonador P-EDF, e para a continuação dos trabalhos foram utilizados três grupos de tarefas, descritas nas tabelas 4.1, 4.2 e 4.3. O conjunto de tarefas 1, por ter maior porcentagem de uso, foi utilizada para geração dos dados capturados, enquanto os conjuntos 2 e 3, com menor uso, foram utilizadas para validação da heurística.

Tabela 4.1 - Conjunto de tarefas 1.

| Período (us) Deadline (us) |        | WCET (us) | CPU |

|----------------------------|--------|-----------|-----|

| 50000                      | 50000  | 27098     | 0   |

| 25000                      | 25000  | 5504      | 1   |

| 100000                     | 100000 | 68919     | 2   |

| 100000                     | 100000 | 64664     | 3   |

| 50000                      | 50000  | 9310      | 4   |

| 200000                     | 200000 | 105758    | 5   |

| 200000 | 200000 | 29326 | 6 |

|--------|--------|-------|---|

| 200000 | 200000 | 67222 | 7 |

| 50000  | 50000  | 21151 | 6 |

| 50000  | 50000  | 6757  | 4 |

| 50000  | 50000  | 34329 | 1 |

| 50000  | 50000  | 8203  | 4 |

| 100000 | 100000 | 44566 | 7 |

| 25000  | 25000  | 8853  | 4 |

**Tabela 4.2 -** Conjunto de tarefas 2.

| Período (us) | Deadline (us) | WCET (us) | CPU |

|--------------|---------------|-----------|-----|

| 50000        | 50000         | 24388     | 0   |

| 25000        | 25000         | 4954      | 1   |

| 100000       | 100000        | 62027     | 2   |

| 100000       | 100000        | 58198     | 3   |

| 50000        | 50000         | 8379      | 4   |

| 200000       | 200000        | 95182     | 5   |

| 200000       | 200000        | 26393     | 6   |

| 200000       | 200000        | 60500     | 7   |

| 50000        | 50000         | 19036     | 6   |

| 50000        | 50000         | 6081      | 4   |

| 50000        | 50000         | 30896     | 1   |

| 50000        | 50000         | 7383      | 4   |

| 100000       | 100000        | 40109     | 7   |

| 25000        | 25000         | 7968      | 4   |

**Tabela 4.3 -** Conjunto de tarefas 3.

| Período (us) | Deadline (us) | WCET (us) | CPU |

|--------------|---------------|-----------|-----|

| 25000        | 25000         | 13958     | 0   |

| 100000       | 100000        | 15135     | 1   |

| 200000       | 200000        | 136986    | 2   |

| 50000        | 50000         | 25923     | 3   |

| 25000        | 25000         | 11637     | 4   |

| 100000       | 100000        | 20072     | 5   |

| 50000        | 50000         | 30484     | 6   |

| 200000       | 200000        | 25220     | 7   |

| 200000       | 200000        | 23924     | 7   |

| 100000       | 100000        | 31920     | 1   |

| 50000        | 50000         | 18343     | 5   |

| 50000        | 50000         | 19205     | 7   |

A Tabela 4.4 apresenta as porcentagens de uso de cada conjunto de tarefas.

**Tabela 4.4** - Uso de cada CPU nos Conjuntos de Tarefas 1, 2 e 3.

| CPU | Conjunto 1 (Tabela 1) | Conjunto 2 (Tabela 2) | Conjunto 3 (Tabela 3) |

|-----|-----------------------|-----------------------|-----------------------|

| 0   | 54,20%                | 48,78%                | 55,83%                |

| 1   | 90,67%                | 81,60%                | 47,06%                |

| 2   | 68,92%                | 62,03%                | 68,49%                |

| 3   | 64,66%                | 58,19%                | 51,85%                |

| 4   | 83,95%                | 75,56%                | 46,55%                |

| 5   | 52,88%                | 47,59%                | 56,76%                |

| 6   | 56,97%                | 51,27%                | 60,97%                |

| 7   | 78,18%                | 70,36%                | 62,98%                |

A partir da definição dos conjuntos de tarefas, foi elaborado o conjunto de operações a serem executadas, para cobrir maior número de possibilidades, foram programadas três tipos de operações, sendo elas recursivas, iterativas e operações de leitura e escrita de memória. A base das operações realizadas é descrita abaixo:

- Operação recursiva: consiste na repetição do cálculo da função de Fibonacci para o número 25, com tempo aproximado de 600 us. O número de repetições é determinado pela divisão do WCET da tarefa por 600. Após cada execução do método, uma multiplicação de pontos flutuantes é executada para que se aumente o estresse na máquina e que se aumente a cobertura das funções executadas pelo processador;

- Operação iterativa: execução da função de Fibonacci para um número grande. Tem tempo de execução de 1 us, portanto o número de execuções é WCET;

- Operação de leitura e escrita de memória: executa repetidamente a leitura de regiões aleatórias de um vetor. Tempo médio de 30 us. Repetições são definidas pela divisão de WCET por 30. O tamanho do espaço de memória lido é de 128KB.

Os tempos para execução de cada operação foram calculados em uma execução sem heurística ativa.

#### **4.2. CAPTURA DE DADOS**

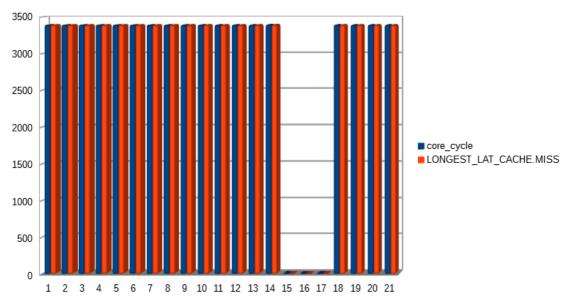

O total de eventos, possíveis para captura, implementados no EPOS e disponíveis na versão Sandy Bridge da PMU é 218, sendo 3 desses, configurados como contadores

fixos, totalizando 215 eventos configuráveis. Como a versão suporta apenas a contagem simultânea de 4 eventos, foram necessárias 54 execuções por task-set e tipo de execução.

Todas as execuções foram feitas utilizando o escalonador P-EDF (Partitioned EDF). Uma vez que os contadores foram alinhados para uma primeira análise, era necessário que as CPUs tivessem número semelhante de capturas (cada CPU possui uma fila de execução e, pela característica, já citada, de não intrusão do EPOS, as diferentes execuções mantém número semelhante de capturas, mantendo assim um certo determinismo entre as execuções).

Este nível de "determinismo" não aconteceria em execuções G-EDF, uma vez que a fila de execução é única e a distribuição das tarefas entre as CPUs sofre interferência de fatores não determinísticos, e também não seria possível com execuções sobre um escalonador C-EDF (Clustered EDF), uma vez que as filas podem ser compartilhadas por mais de uma CPU, logo as capturas seriam semelhantes entre clusters e não entre CPUs.

Para facilitar o processo de execução, foram criados um arquivo shell-script para compilar e enviar as imagens (alternando os eventos da PMU) e um outro para executar e enviar para a plataforma IoT os logs de execução, fazendo backup dos mesmos em uma mídia removível.

### 4.3. ANÁLISE

Uma vez realizadas todas as capturas, era necessário realizar uma análise para determinar os eventos a serem utilizados no desenvolvimento da heurística de Power-Cap. Num primeiro momento, porém, era necessário estimar o consumo

energético nas execuções para que se pudesse determinar um rumo quanto as correlações úteis.

### **4.3.1.ESTIMATIVA DE CONSUMO**

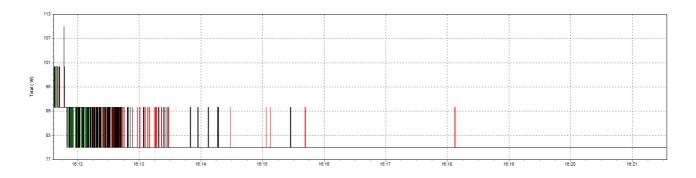

A partir dos dados capturados, era necessário fazer estimativas do consumo durante a execução das task-sets antes de estipular-se um ponto de aplicação de Power-Cap.

Esta tarefa foi realizada, neste primeiro momento, com o auxílio da ferramenta Fluke [24], com diagrama de montagem do circuito de captura apresentado na Figura 4.1, utilizando alicates i430flex com limitação de 300 A (amperes) e utilizando o logger (monitor) para capturas a cada 0,25 segundos, ou seja, 250 milissegundos, com a adição dos medidores de consumo energético (nomeado pelo Fluke de Potência ou Power) aos dados a serem capturados.

1 PHASE + NEUTRAL FLUKE 435-11 V04.00

BACK

**Figura 4.1** – Diagrama de montagem do circuito de medição - Fluke.

Imagem retirada em forma de fotografia do diagrama apresentado pelo Fluke.

A análise dos dados capturados é feita através do software Power Log, disponibilizado em um CD de instalação que acompanha o aparelho, juntamente com manual de uso em vários idiomas e algumas outras ferramentas, e também disponível no site da Fluke (<a href="https://www.fluke.com/pt-br">https://www.fluke.com/pt-br</a>).

Ao se realizar o comparativo com os valores de consumo obtidos a partir da interface RAPL, porém, o valor apontado não era compatível, fato já esperado uma vez que os indicadores da interface RAPL no processador utilizado são capazes de indicar apenas o consumo do pacote ou de um de seus componentes internos, não representando o consumo de energia total da execução das tarefas.

Neste momento se fez necessária uma escolha entre duas alternativas, sendo elas as opções de se trabalhar com a análise de consumo do processador e aplicar Power-Cap apenas sobre seu consumo, ou tratar do Power-Cap sobre todo o sistema.

Tendo em vista a dificuldade de aferir consumo utilizando a interface RAPL para alguns intervalos de tempo (dependendo do tamanho do intervalo de tempo as leituras eram imprecisas, principalmente quando os intervalos de tempo eram menores que um milissegundo), aliada aos fatos de que os dados utilizados para elicitação de eventos correlatos ainda não conterem as leituras dos registradores de consumo da interface e que ao aplicar-se Power-Cap sobre o sistema por completo, automaticamente estaria-se aplicando, também, sobre o processador, foi optado por trabalhar com o desenvolvimento de Power-Cap sobre o sistema por completo.

Uma vez efetuadas as aferições de consumo e levando em conta a escolha adotada, foi buscado um dos eventos da PMU ou dos demais eventos de Software e

Hardware capturados que melhor descrevesse a variação energética. Durante leituras e pesquisas, foi encontrada a relação entre dissipação de energia e temperatura. Para um melhor entendimento dessa relação, foi necessário entender os conceitos de TDP e do Perfil Térmico do processador utilizado.

#### 4.3.1.1 TDP

Potência de Design Térmico (TDP - Thermal Design Power) representa a potência média, em Watts, que o processador dissipa quando operando na Frequência Básica do processador (Processor Base Frequency) com todos os cores ativos sobre uma carga de trabalho de alta complexidade definida pela Intel.

A Frequência Básica do processador descreve a taxa em que os transistores do processador abrem e fecham.

No caso do processador utilizado no desenvolvimento deste trabalho, tanto para captura de dados, quanto para testes, o TDP é fixado em 95W, atingidos com uso de memória RAM DDR3 de 1333MHz.

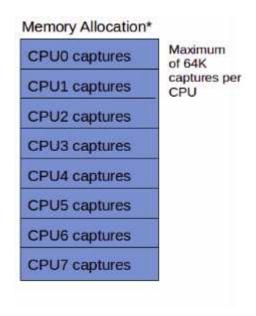

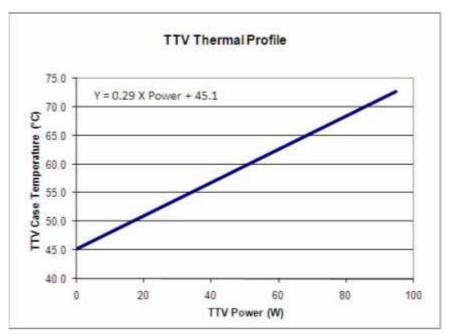

### **4.3.1.2 PERFIL TÉRMICO E TTV**

Perfil Térmico é definido pela Intel [20] como a linha que representa a especificação de temperatura do case do TTV num determinado nível de energia consumida, sendo o TTV definido como Veículo de Teste Térmico (Thermal Test Vehicle - TTV), definido como um pacote mecanicamente equivalente que contém um aquecedor resistivo na matriz ("cama" do processador) para avaliar as soluções térmicas.

Para entender melhor esta linha, deve-se entender alguns termos, são eles:

- Psi-CA: definido como parâmetro de caracterização térmica do case para o ambiente. Trata-se de uma medida de performance da solução térmica utilizando a toda a energia do pacote. É calculado como (T<sub>CASE</sub> - T<sub>LA</sub>) / Energia Total do Pacote (igual ao TDP);

- T<sub>CASE</sub>: Temperatura do processador. A temperatura T<sub>CASE</sub> do TTV é medida no topo do centro geométrico do dissipador de calor do TTV;

- T<sub>LA</sub>: Temperatura do ambiente, medida nos arredores do processador. Pode ser estimada como a soma da temperatura externa a cpu e o aumento de temperatura típico do chassi do processador;

- T<sub>CASE-MAX</sub>: Maior temperatura conforme especificação de um componente.

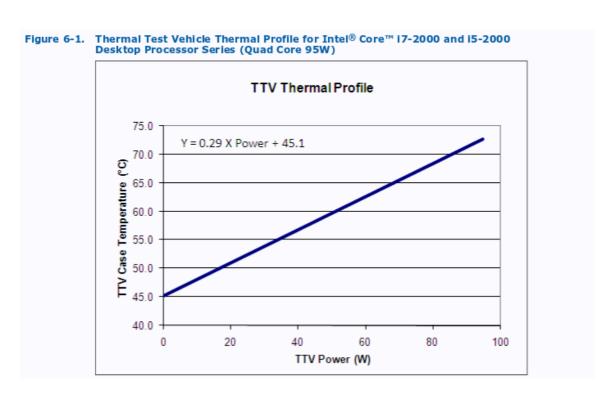

O gráfico de perfil térmico para o processador utilizado neste trabalho é fornecido pela Intel e pode ser conferido na Figura 4.2 (parte 'a') com temperatura ambiente de 45.1°C. O T<sub>CASE-MAX</sub> para o modelo é de 72.6°C em 95W e o Psi-CA é de 0,29.

**Figura 4.2 a)** – Perfil Térmico do Processador Intel® Core™ i7-2600.

Um dos fatores que interfere na relação entre energia dissipada e temperatura é a temperatura ambiente. A Intel disponibiliza, ainda, um gráfico (Figura 4.2 b) que ajuda a entender essa relação e a interferência da temperatura ambiente (T<sub>AMBIENT</sub>).

Example: Required YCA for Various TAMBIENT Conditions Psi-ca = 0.29 Psi-ca = 0.34 Psi-ca = 0.40 Psi-ca = 0.45 Ta = 45.1 °C Ta = 40.0 °C Ta = 35.0 °C Ta = 30.0 °C 80 70 60 50 40 30 20 10 0 20 0 40 60 80 95 TTV Power Dissipation

Figura 4.2 b) – Variação de Psi-CA para vários T<sub>AMBIENT</sub>.

Fonte: 2nd Gen Intel® Core™ Processor, LGA1155 Socket: Thermal Guide

Conforme determinado pela Intel no Guia Térmico do processador [20], quanto mais baixa a temperatura ambiente, mais alto será o Psi-CA requerido, o que significa velocidades mais baixas na ventilação e redução na acústica da solução térmica do processador.

## 4.3.2.PREPARAÇÃO

Uma vez os dados recolhidos, para aplicação de mineração de dados era necessário um pré-processamento. Tal procedimento foi dividido em etapas de seleção de dados, limpeza e transformação.

Para a análise dos dados capturados, foi optado por trabalhar com arquivos CSVs (comma-separated values). Para transformar os logs gerados em arquivos neste formato, foram utilizados scripts em python.

## 4.3.2.1SELEÇÃO DE DADOS

Esta etapa do pré-processamento dos dados tem como objetivo a redução do conjunto de dados a ser trabalhado nas próximas etapas e na mineração em si. Como o conhecimento prévio sobre os dados era pequeno, e os eventos poderiam não ser de fácil interpretação, foi optado por trabalhar com praticamente todo o conjunto de dados, não eliminando nenhum dos eventos capturados. Os únicos dados que foram excluídos da análise foram os identificadores da thread, sua prioridade e os contadores de deadline perdidas (deadline misses).

#### 4.3.2.2LIMPEZA DE DADOS

Esta etapa do pré-processamento tem como objetivo o tratamento de incompletudes, a remoção de ruídos, através da identificação de outliers, e a correção de inconsistências no conjunto de dados [26].

No caso dos dados trabalhados, as coletas foram feitas em um sistema planejado de modo a evitar incompletudes ou inconsistências, uma vez que todos os valores eram capturados com a devida tipagem em cada uma das capturas.

Quanto a remoção de ruídos, foi optado por ignorar a análise da primeira captura, uma vez que passa-se um período de inicialização onde os contadores demonstram um comportamento não advindo da aplicação e em um período de tempo tipicamente superior aos intervalos entre interrupções e inicializações e/ou finalizações de tarefas.

Outros dados removidos foram as paralisações que expressam o momento em que uma thread é liberada pelo *dispatch* para começar sua execução e o alarme que libera um novo ciclo de execução periódica ainda não foi liberado, logo o intervalo entre a execução dos métodos de *dispatch* e *wait-next* não representa um período de execução das tarefas e pode ter intervalo de tempo de 0 us (microsegundos), comprometendo assim o cálculo de crescimento dos contadores no intervalo.

Com exceção aos aspectos levantados acima, não foram retirados pontos de outlier, pois foi adotado o pressuposto de que o comportamento dos contadores durante a execução possam ser explicados e que as discrepâncias poderiam indicar alguma variação de importância na análise.

# **4.3.2.3INTEGRAÇÃO DE DADOS**

Este procedimento consiste em unir dados de várias fontes para a aplicação de mineração de dados. Num primeiro momento, partindo do pressuposto de que a interferência causada pelo EPOS é baixíssima e que não haviam fatores externos que viessem a interferir na execução dos conjuntos de tarefas (task-sets), foi adotada uma abordagem de unir dados de cada uma das 54 capturas num único arquivo.

Entretanto, a união das capturas acarretou numa pequena perda de precisão (na ordem de alguns microssegundos, ou até um milisegundo, diferença que pode ser causada por aspectos da computação Multi-Core que são, tipicamente, não

determinísticos) e também exigiu a escolha de utilizar média dos contadores fixos, ou ignorar os valores das demais capturas. Para que não houvesse perda de precisão quanto a nenhum contador, nem quanto as variações e as diferenças nos tempos dos intervalos, uma vez que, quando se perde precisão na contagem de tempo, as taxas de crescimento também perdem e os contadores têm seu comportamento distorcido (mesmo que minimamente).

Tendo em vista os problemas encontrados, foi adotada a estratégia de se analisar os comportamentos dos contadores de cada execução separadamente.

## 4.3.2.4TRANSFORMAÇÃO DOS DADOS

A etapa de transformação dos dados consiste em transformar ou consolidar os dados para que a mineração exercida seja mais eficiente [26]. São estratégias de transformação a aplicação de normalização, que consiste em deixar todos os dados numa igual faixa de variação (geralmente de 0 à 1), agregação, onde vários registros com granularidade maior são agrupados em um único registro com granularidade menor (de dia para mês, por exemplo), discretização, quando atributos numéricos são separados em intervalos e construção de atributos, onde um novo atributo é gerado através dos dados já existentes.

Para este trabalho, como os dados são capturas de contadores digitais e os mesmos são constantemente incrementados, a transformação necessária consistiu em calcular a diferença entre os contadores de modo a determinar o crescimento no atual período de tempo e, também, calcular as médias de crescimento pelo tamanho do intervalo de tempo (crescimento / tempo = unidades incrementadas/microssegundo).

## 4.3.3.LEVANTAMENTO DE CORRELAÇÕES

Durante a fase de levantamento de correlações foram utilizadas duas abordagens. A primeira delas buscava correlações sobre crescimentos absolutos de contadores (quanto os contadores cresciam no intervalo entre duas capturas), enquanto a segunda, buscava correlações entre valores médios de crescimento (crescimento no intervalo / tempo). A segunda abordagem contou também com testes analisando variação de temperatura.

Para a primeira abordagem foram usados dois algoritmos disponíveis no Weka, o *PrincipalComponents*, algoritmo que executa PCA (Principal Components Analysis - Análise dos Principais Componentes) e o *CorrelationAttributeEval*, algoritmo que avalia o valor de um atributo medindo a correlação, através do método de Pearson, entre ele e a classe escolhida. Ambos os métodos estão disponíveis por padrão na aba de Seleção de Atributos (Select attributes) do Weka nas suas versões 3.8.2 e 3.9.2.

Após esta primeira etapa, foi optado por trabalhar com análise de valores médios com a variação de temperatura (segunda abordagem), uma vez que o foco seria identificar quais contadores descreviam melhor uma situação de alta ou de baixa no aquecimento do processador. O processo também se seguiu focando no uso do algoritmo *CorrelationAttributeEval*, uma vez que sua saída é mais facilmente entendida pelo fato de que o algoritmo entrega as correlações de todos os atributos presentes com a classe.

Um modelo de saída do algoritmo para valores relativos de temperatura e média de crescimento dos contadores pode ser encontrado na Figura 4.3.

**Figura 4.3** – Aplicação do algoritmo *CorrelationAttributeEval* sobre dados capturados.

```

=== Run information ===

Evaluator:

weka.attributeSelection.CorrelationAttributeEval

weka.attributeSelection.Ranker -T -1.7976931348623157E308 -N -1

Search:

batch34 cpu7 named

Relation:

Instances:

3245

Attributes:

temperature

inst retired

core cycle

ref clock

OFFCORE REQUESTS.DEMAND DATA RD

OFFCORE REQUESTS.DEMAND RFO

OFFCORE REQUESTS.ALL DATA RD

UOPS DISPATCHED.CORE

timestamp

evaluate on all training data

Evaluation mode:

=== Attribute Selection on all input data ===

Search Method:

Attribute ranking.

Attribute Evaluator (supervised, Class (numeric): 1 temperature):

Correlation Ranking Filter

Ranked attributes:

0.50381 8 UOPS DISPATCHED.CORE

0.39905 4 ref clock

0.39901 3 core_cycle

0.35247 2 inst retired

0.34963 7 OFFCORE REQUESTS.ALL DATA RD

-0.00454 5 OFFCORE REQUESTS.DEMAND DATA RD

-0.00703 9 timestamp

-0.02427 6 OFFCORE REQUESTS.DEMAND RFO

```

Os parâmetros utilizados nos métodos aplicados são padrões do Weka, nenhum deles foi alterado.

O procedimento foi repetido para cada uma das 54 execuções usando métodos recursivos e operações de memória, gerando assim, todos os valores de correlação entre cada um dos eventos e a variação de temperatura. Os melhores resultados obtidos são apresentados na Tabela 4.5.

**Tabela 4.5** – Tabela das principais correlações com a Variação de Temperatura.

|    | Exec. Recursiva             | Correlação | Exec. Memcpy                    | Correlação |

|----|-----------------------------|------------|---------------------------------|------------|

| 1  | UOPS_DISPATCHED.THREAD      | 0.5        | UOPS_DISPATCHED.THREAD          | 0.48       |

| 2  | INT_MISC.RECOVERY_CYCLES    | 0.42       | ref_clock / core_cycle          | 0.35       |