# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLOGICO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELTÉTRICA

Rafael Luciano Radin

# A SELF-STARTUP ULTRA-LOW-VOLTAGE BOOST CONVERTER FOR THERMAL ENERGY HARVESTING

# Rafael Luciano Radin

# A SELF-STARTUP ULTRA-LOW-VOLTAGE BOOST CONVERTER FOR THERMAL ENERGY HARVESTING

Tese submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do título de Doutor em Engenharia Elétrica

Orientador: Prof. Dr. Márcio Cherem Schneider

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Radin, Rafael Luciano

A self-startup ultra-low-voltage boost converter for thermal energy harvesting / Rafael Luciano Radin; orientador, Márcio Cherem Schneider, 2020.

115 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2020.

Inclui referências.

1. Engenharia Elétrica. 2. Energy harvesting. 3. DC-DC converters. 4. Ultra-low-voltage electronics. 5. Zero current switching. I. Schneider, Márcio Cherem. II. Universidade Federal de Santa Catarina. Programa de Pós Graduação em Engenharia Elétrica. III. Título.

# Rafael Luciano Radin

# A SELF-STARTUP ULTRA-LOW-VOLTAGE BOOST CONVERTER FOR THERMAL ENERGY HARVESTING

O presente trabalho em nível de doutorado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. Tales Cleber Pimenta, Ph.D. Universidade Federal de Itajubá (UNIFEI)

Prof. Oscar da Costa Gouveia Filho, Dr. Universidade Federal do Paraná (UFPR)

Prof. Cesar Ramos Rodrigues, Dr.

Universidade Federal de Santa Catarina (UFSC)

Eng. Paulo Augusto Dal Fabbro, Dr. Chipus Microelectronics

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de doutor em Engenharia Elétrica.

Prof. PhD Bartolomeu Uchôa-Filho Coordenador do Programa

Prof. Dr. Márcio Cherem Schneider Orientador

Florianópolis, 08 de abril de 2020.

#### **AGRADECIMENTOS**

Agradeço ao meu orientador Márcio Cherem Schneider pela dedicação prestada ao longo dos anos de trabalho.

Agradeço ao Prof. Mohamad Sawan pela orientação e pela infraestrutura disponibilizada na École Polytechnique de Montréal durante o período de Doutorado Sanduíche. Agradeço também ao Carlos Galup-Montoro pelas importantes contribuições realizadas ao longo deste trabalho.

Agradeço a todos os meus colegas do Laboratório de Circuitos Integrados (LCI) da UFSC e da École Polytechnique de Montréal, em especial Lucas Pereira Luiz e Franciele Nörnberg.

Agradeço aos ex-integrantes do LCI, Arun Kumar. Sinha e Marcio Bender Machado, pelos trabalhos previamente desenvolvidos, que formaram a base fundamental para que este trabalho pudesse ser realizado.

Agradeço ao CNPq e a UNISE, pelo apoio financeiro durante a etapa de Doutorado Sanduíche no Canadá e a CMC Microsystems pela fabricação do chip.

Agradeço aos membros da banca examinadora, Prof. Tales Cleber Pimenta, Prof. Oscar da Costa Gouveia Filho, Prof. Cesar Ramos Rodrigues e Eng. Dr. Paulo Augusto Dal Fabbro, pelo tempo dedicado e pelas importantes sugestões que contribuíram positivamente para o resultado final deste trabalho.

Por fim, gostaria de agradecer aos meus pais, à minha esposa Michely e minhas filhas, Emilia e Lisa, pelo apoio e compreensão.

#### **RESUMO**

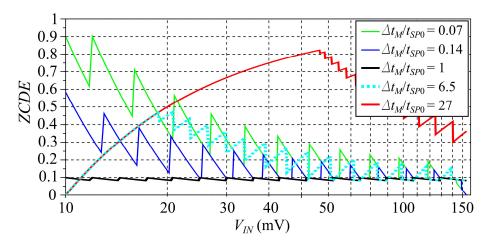

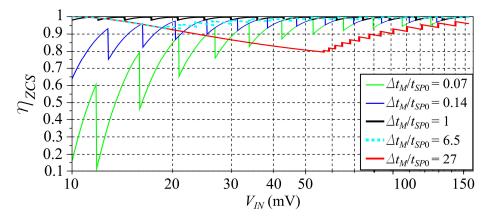

Esta tese apresenta a análise e implementação de um conversor DC-DC operando em ultra baixa tensão para aplicações em colheita de energia térmica. O projeto foca na redução da mínima tensão de entrada para autoinicialização e operação do conversor elevador de tensão indutivo, bem como na melhoria da eficiência em toda faixa de tensão de entrada. O conversor elevador de tensão indutivo é analisado e equações de projeto são fornecidas considerando a operação em ultra-baixa tensão de entrada, onde as não-idealidades características de operação com disponibilidade de potência restrita são contabilizadas. A inicialização do conversor é realizada por um mecanismo composto de um oscilador em anel com excursão ampliada e um retificador. Com o intuito de minimizar a tensão de inicialização do sistema, uma metodologia de co-projeto para o oscilador e o retificador é proposta, bem como a implementação de um conversor elevador de tensão que utiliza a chave do ramo inferior com largura variável. O sistema de chaveamento em corrente zero proposto introduz escalamento não linear para modulação do pulso que controla o tempo de descarga do indutor do conversor elevador de tensão, incrementando a eficiência para baixas tensões de entrada. As expressões derivadas para a definição do atraso de medição do esquema de chaveamento em corrente zero aumentam a acurácia da detecção do cruzamento da corrente por zero, maximizando a eficiência de conversão. Resultados experimentais mostram avanços na mínima tensão requerida para inicialização do conversor elevador de tensão quando comparado ao atual estado da arte. O conversor inicializa para uma tensão de apenas 11 mV, proporcionado operação em regime permanente para tensões de entrada de até 7,3 mV. A eficiência é superior a 50% para tensões de entrada superiores a 10,5 mV. Os resultados obtidos possibilitam o uso do conversor para operação independente e contínua a partir de gradientes de temperatura da ordem de 1°C.

**Palavras-chave:** Colheita de energia térmica. Ultra-baixa tensão, Gerador termelétrico. Conversor elevador de tensão. Autoinicialização. Chaveamento em corrente zero.

#### **RESUMO EXPANDIDO**

# Introdução

Com a crescente miniaturização e aumento da capacidade computacional dos dispositivos eletrônicos, tornaram-se possíveis diversas aplicações no cenário da Internet das Coisas, onde dispositivos conectados realizam a aquisição de grandes quantidades de dados, que podem ser processados usando técnicas de aprendizado de máquina, permitindo a execução de tarefas cada vez mais complexas. Diversas são as aplicações no contexto de cidades inteligentes, como a implantação de uma rede elétrica inteligente, monitoramento de ruído e poluição, gerenciamento de tráfego e de resíduos, estacionamento e iluminação inteligentes, etc. Dispositivos inteligentes possuem diversas aplicações também em edificações, relacionadas a entretenimento, qualidade de vida, automação inteligente, etc. O corpo humano também tem um forte potencial para várias aplicações, como sensores para treinamento esportivo, dispositivos de monitoramento de saúde acoplados ao corpo humano, etc. Dada a vasta aplicação de dispositivos inteligentes na vida cotidiana, o número de dispositivos conectados tem aumentado constantemente. Este elevado número requer uma interação transparente e descomplicada com o usuário, sendo impraticável gerenciar, recarregar ou substituir baterias para cada aplicação. Neste sentido, um requisito importante para os dispositivos conectados é o suprimento de energia autônomo, que permite que o dispositivo seja independente de fiação ou baterias, diminuindo a frequência de manutenção e permitindo maior portabilidade para o dispositivo. Nesse contexto, a colheita de energia tornou-se uma solução importante, permitindo que esses dispositivos atendam aos requisitos de operação autônoma e ininterrupta. A colheita de energia térmica é de particular interesse para várias aplicações relacionadas ao corpo humano, pois pode fornecer energia ininterruptamente a partir do calor dissipado, em níveis de grandeza superiores a outras formas de colheita de energia. Em uma aplicação típica de colheita de energia, conversores de tensão são empregados para aumentar o nível de tensão gerado pelos geradores termoelétricos, que geralmente é da ordem de algumas dezenas de mV. As figuras de mérito mais relevantes para esses conversores são a faixa de tensão de entrada, eficiência, tensão mínima de entrada, tensão de inicialização e o tamanho do dispositivo.

### **Objetivos**

Nesta tese foi desenvolvido um conversor de tensão para colheita de energia térmica, onde os seguintes tópicos foram propostos e pesquisados: análise do conversor elevador de tensão indutivo operando em ultrabaixa tensão e alimentado por uma fonte de alimentação limitada; desenvolvimento de uma topologia de conversor eficiente utilizando um esquema de crescimento da tensão de saída passo a passo; desenvolvimento de um procedimento de projeto para o bloco de inicialização do conversor com a premissa de minimizar a tensão mínima para inicialização; um esquema de comutação em corrente zero modificado que aumenta significativamente a precisão de detecção de corrente zero e eficiência de conversão. O conversor de tensão para aplicações em colheita de energia térmica foi projetado objetivando-se as seguintes contribuições para o estado da arte: a redução da mínima tensão de entrada do conversor para operação em regime permanente; a redução da tensão de inicialização do conversor; a maximização da eficiência em toda a faixa de tensão de entrada. Estas características permitem o conversor inicializar e operar eficientemente em baixos gradientes de temperatura, permitindo que a colheita de energia térmica possa ser realizada de forma eficiente a partir do corpo humano, mesmo em condições adversas de temperatura.

# Metodologia

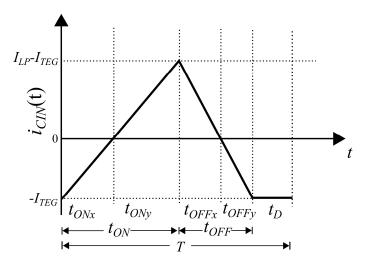

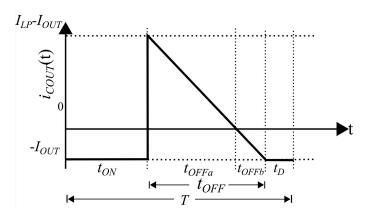

Um modelo matemático para o conversor elevador de tensão indutivo foi desenvolvido, utilizando modificações necessárias às equações do conversor que refletem as condições de baixa tensão de entrada e a restrição da capacidade de corrente do gerador termoelétrico. As expressões derivadas permitem definir o tamanho ótimo para as chaves do conversor elevador de tensão indutivo, bem como definir a frequência de chaveamento para maximizar a extração da potencia provida pelo gerador termoelétrico. A arquitetura desenvolvida utiliza o conversor elevador de tensão indutivo para operação em regime permanente e um circuito auxiliar para realizar a inicialização do conversor, cuja metodológica de otimização foi empregada no intuito de minimizar a tensão de entrada para inicialização do conversor. Como o conversor elevador de tensão indutivo opera no modo de condução descontínuo, foi desenvolvido um circuito de chaveamento em corrente zero com escalamento não linear do pulso relacionado ao tempo de descarga do indutor, provendo aumento da eficiência de conversão para níveis mais baixos de tensão de entrada. Também foram definidos parâmetros temporais importantes para o circuito de chaveamento em corrente zero, minimizando o erro de detecção do cruzamento da corrente por zero, o que contribui positivamente para o aumento da eficiência de conversão. A fase de projeto do conversor foi realizada através de ferramenta de automação de design eletrônico Cadence, disponibilizada na École Polytechnique de Montréal, sendo possível a simulação de esquemático, realização de layout do circuito integrado e simulações pós-layout, de modo a garantir a convergência dos resultados após a integração.

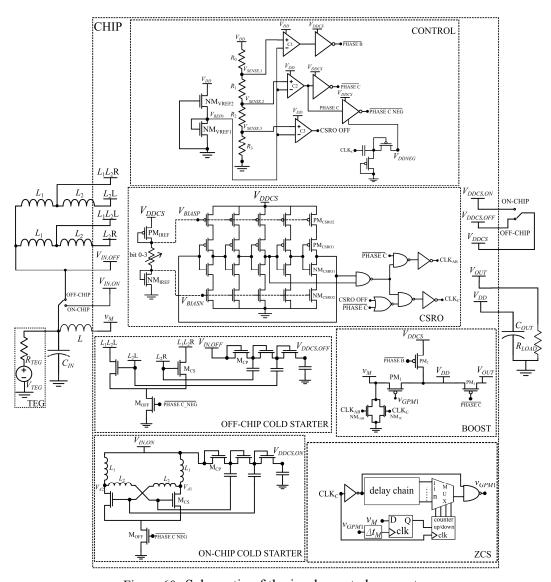

#### Resultados e Discussão

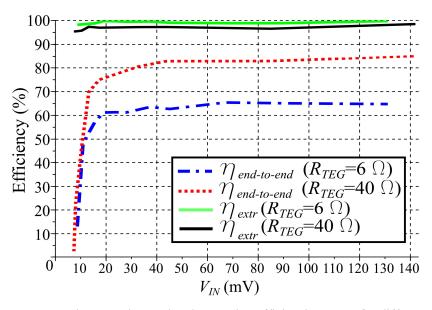

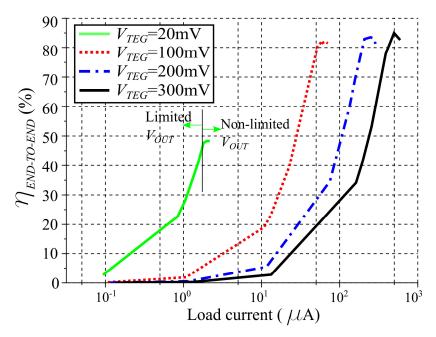

O conversor DC-DC proposto foi integrado na tecnologia CMOS de 130 nm através da facilidade de integração disponibilizada pela CMC Microsystems. O chip fabricado possui uma área total de 1,5x1,5 mm². Alem do circuito integrado, o conversor elevador de tensão indutivo utiliza um indutor e dois capacitores externos. A inicialização do conversor foi realizada através do circuito auxiliar também integrado no mesmo chip, podendo ser implementado de maneira totalmente integrada ou utilizando quatro indutores externos além do circuito integrado no chip. Nos resultados experimentais obtidos, a tensão mínima de inicialização foi de 90 mV utilizando-se indutores integrados. Utilizando-se indutores discretos, o conversor inicializa para níveis de tensão de entrada da ordem de 11 mV. A tensão de entrada mínima capaz de sustentar a operação em regime permanente foi de 7,3 mV. A tensão mínima de entrada necessária para atingir eficiência de 50% é de aproximadamente 10,5 mV. Para tensões de entrada superiores a 40 mV, o conversor mantém eficiência sempre superior a 83%, já á máxima eficiência medida é de 85%. A eficiência de extração é superior a 95% para toda a faixa de tensão de entrada.

# Considerações finais

A tensão de inicialização medida para o conversor é a mais baixa reportada até o momento, com avanço importante em relação ao estado da arte para esta figura de mérito. Os valores medidos para a eficiência em ultrabaixa tensão e mínima tensão de operação do conversor também foram compatíveis com o atual estado da arte. A combinação de alta eficiência para baixas tensões de entrada e inicialização em ultrabaixa tensão obtida neste trabalho permite a realização de colheita de energia térmica eficiente e autônoma mesmo quando o gradiente de temperatura é da ordem de 1 °C, possibilitando a operação autônoma e ininterrupta de dispositivos conectados alimentados pela energia térmica provida pelo corpo humano.

**Palavras-chave:** Colheita de energia térmica. Ultra-baixa tensão, Gerador termelétrico. Conversor elevador de tensão. Autoinicialização. Chaveamento em corrente zero.

#### **ABSTRACT**

This thesis describes the analysis and implementation of a DC-DC converter for ultra-low-voltage thermal energy harvesting applications. The design focuses on the reduction of the minimum input voltage to achieve self-startup and operation of the inductive boost converter, as well as on the improvement of the end-to-end efficiency throughout the input voltage range. The inductive boost converter is analyzed and design equations are provided considering the operation under ultra-low input voltages, where the non-idealities which arise under restricted power availability are taken into account. The startup of the converter is achieved by an auxiliary cold starter comprised of an enhanced-swing ring oscillator and a rectifier. In order to minimize the system startup voltage, a co-design methodology for the oscillator and the rectifier is proposed as well as the implementation of a boost converter using a low-side switch with variable width. The proposed zero-current switching scheme introduces non-linear time scaling for the modulation of the pulse that controls the boost inductor discharging time, which results in higher efficiency at low input voltages. The expression derived for setting the measurement delay of the zero-current-switching scheme increases the accuracy of the zero-current-crossing detection, improving the conversion efficiency. Experimental results show an improvement in the minimum startup voltage of the boost converter when compared to the current state-of-the-art devices. The converter starts up from an input voltage of only 11 mV and provides steady-state operation for input voltages as low as 7.3 mV. The end-to-end efficiency is higher than 50% for voltages above 10.5 mV. The results achieved enable the use of the converter for autonomous and uninterrupted operation from temperature gradients of the order of 1 °C.

**Keywords:** Thermal energy harvesting. Ultra low voltage. Thermoelectric generator. Boost converter. Self startup. Zero-current switching.

# LIST OF FIGURES

| Figure 1 - (a) A sensor node prototype powered by a TEG [11] and (b) a TEG integra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ted into |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| an athlete's clothes [13].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25       |

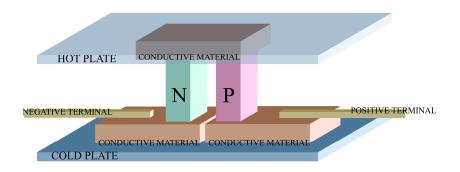

| Figure 2 - The basic structure of the thermocouple.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26       |

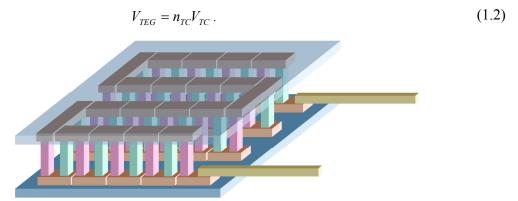

| Figure 3 - Common TEG construction using a series of thermocouples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26       |

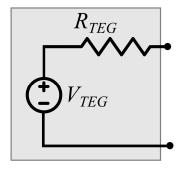

| Figure 4 - The equivalent electric circuit of a TEG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27       |

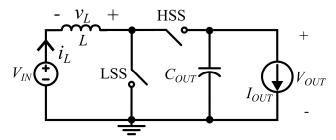

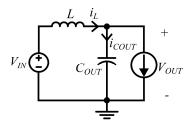

| Figure 5 - Inductive boost converter topology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32       |

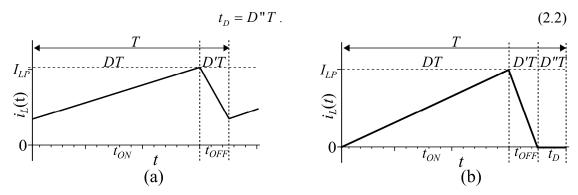

| Figure 6 - Inductor current for (a) CCM and (b) DCM operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32       |

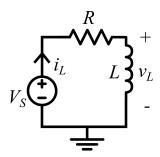

| Figure 7 - Circuit used for the analysis of the inductor charging efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33       |

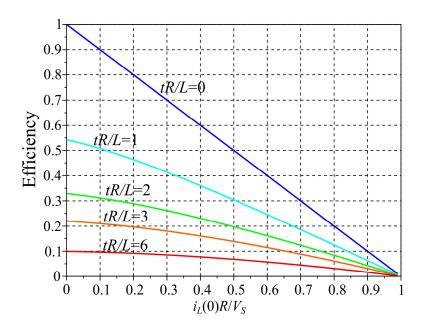

| Figure 8 - Inductor charging efficiency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34       |

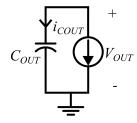

| Figure 9 - Equivalent circuit of the inductive boost converter during $t_{ON}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35       |

| Figure 10 - Equivalent circuit of the inductive boost converter during $t_{OFF}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35       |

| Figure 11 - Equivalent circuit of the inductive boost converter during $t_D$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35       |

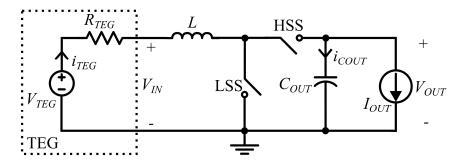

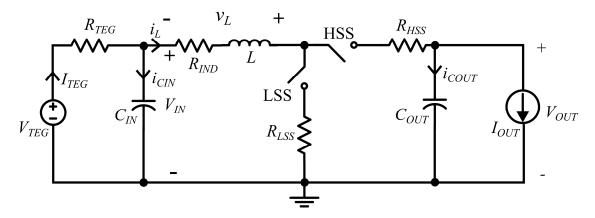

| Figure 12 - Inductive boost converter connected to a TEG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 37       |

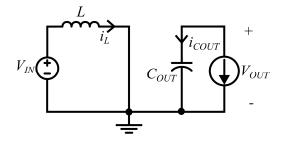

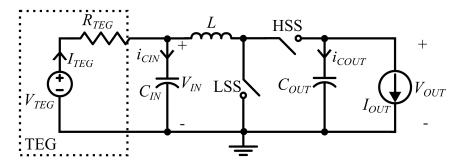

| Figure 13 - Inductive boost converter using an input capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38       |

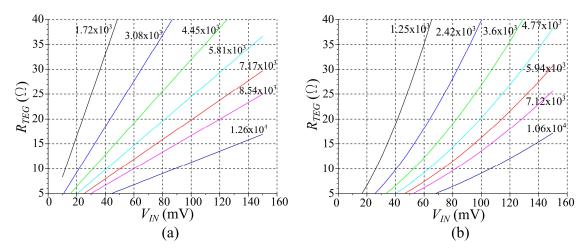

| Figure 14 - Optimum (a) $W_{LSS}$ (µm) and (b) $W_{HSS}$ (µm) as a function of $R_{TEG}$ and $V_{IN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | for the  |

| 130 nm technology. $V_{OUT}$ =1 V, $f_{SW}$ =40 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43       |

| Figure 15 - Model of the inductive boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44       |

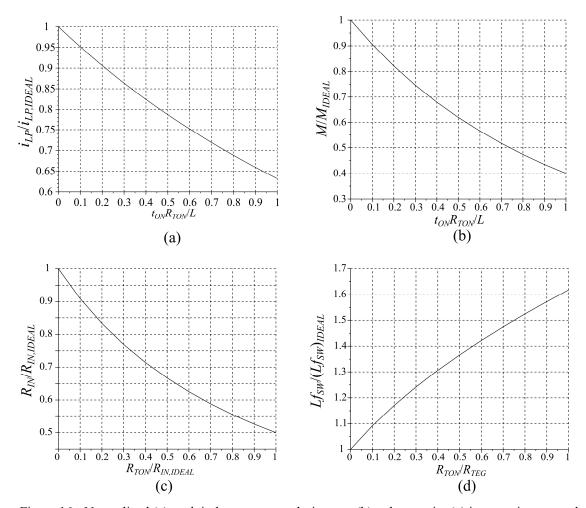

| Figure 16 - Normalized (a) peak inductor current during $t_{ON}$ , (b) voltage gain, (c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ) input  |

| resistance and (d) <i>Lf<sub>SW</sub></i> product for the non-ideal boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46       |

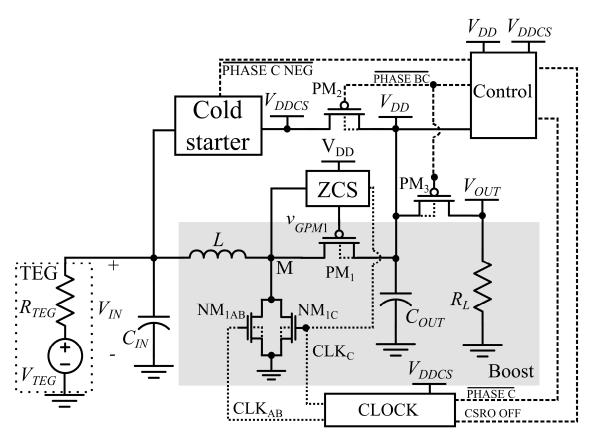

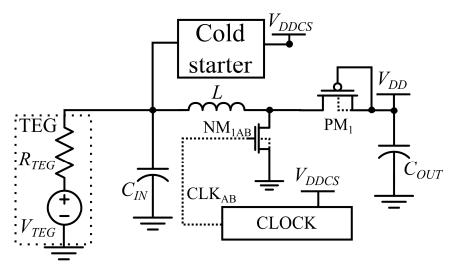

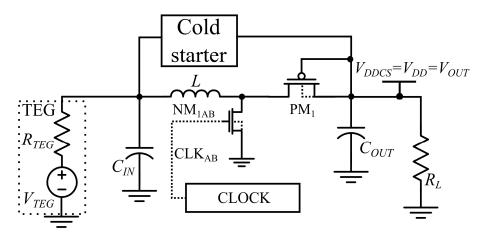

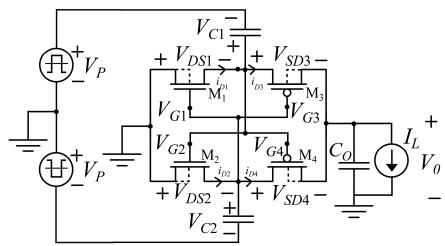

| Figure 17 - Developed converter topology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47       |

| Figure 18 - Converter equivalent circuit during Phase A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49       |

| Figure 19 - Converter equivalent circuit during Phase B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49       |

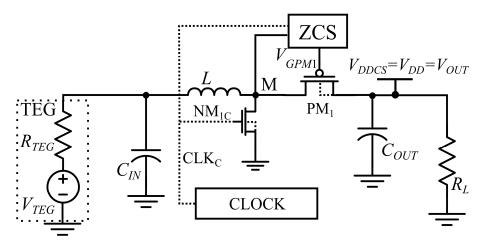

| Figure 20 - Converter equivalent circuit during Phase C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50       |

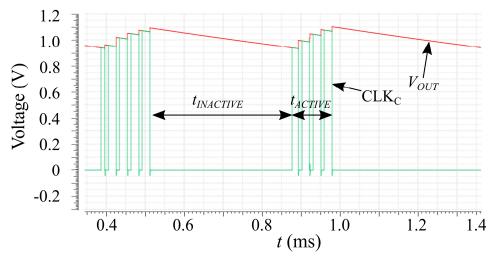

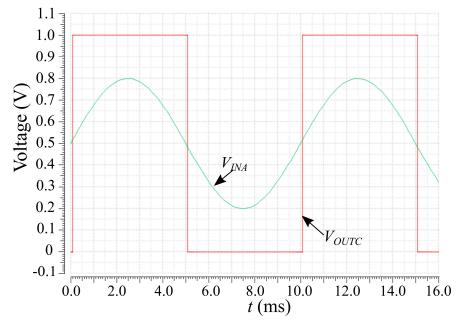

| Figure 21 - Simulation of $V_{OUT}$ limiting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51       |

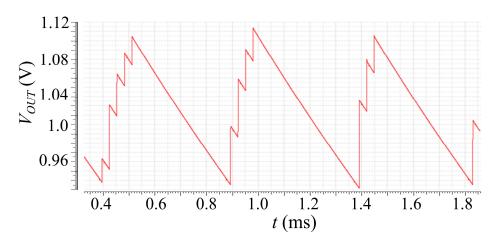

| Figure 22 - Output ripple for $V_{OUT}$ limited to approximately 1 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51       |

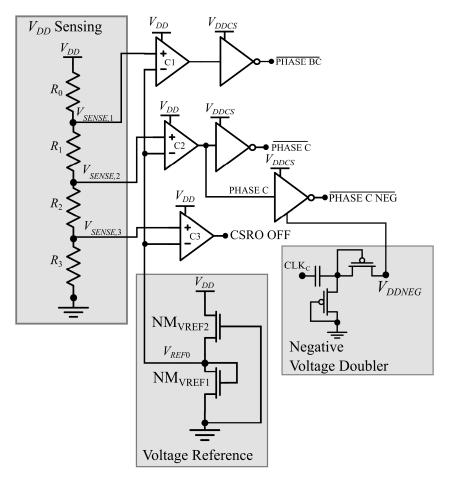

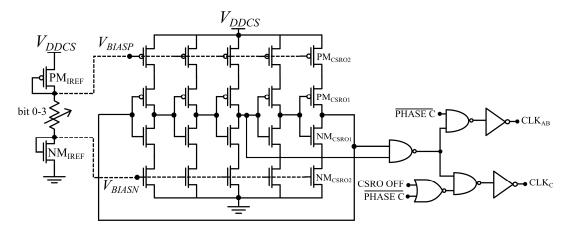

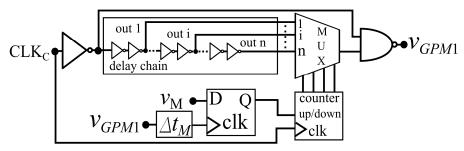

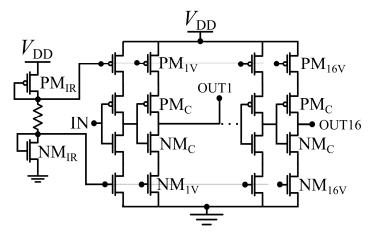

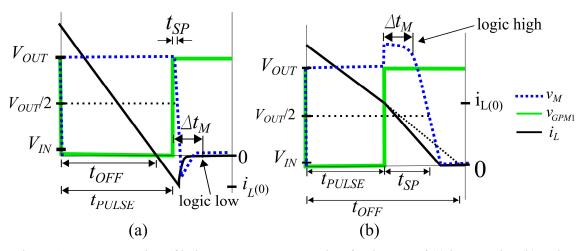

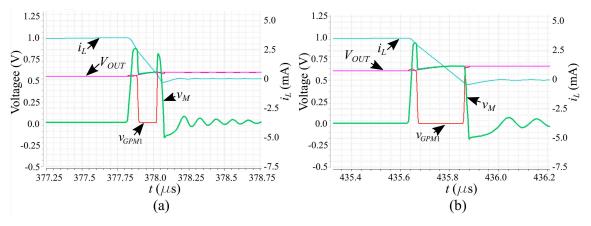

| Figure 23 - Control circuit schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52       |

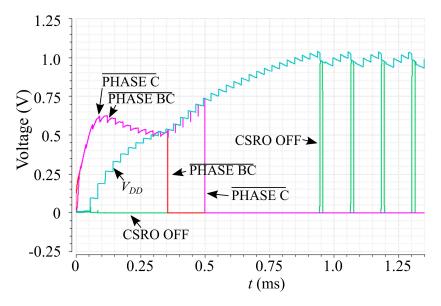

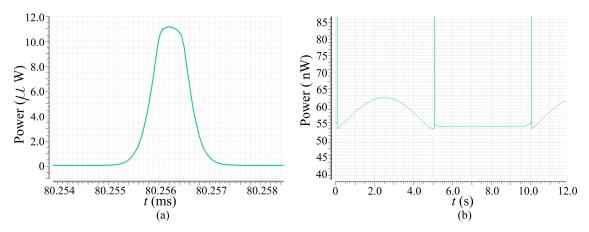

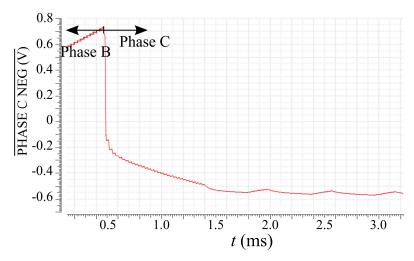

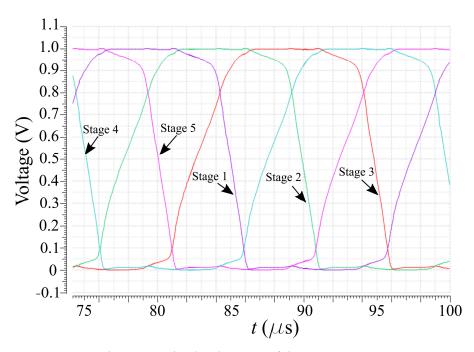

| Figure 24 - Simulation results of the control signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53       |

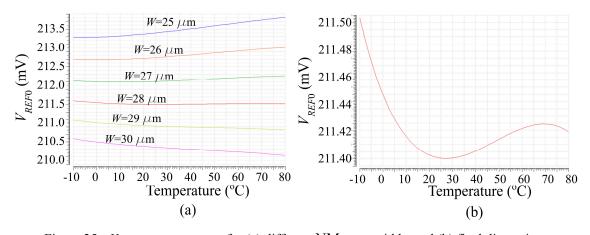

| Figure 25 - $V_{REF0}$ vs temperature for (a) different NM <sub>VREF1</sub> widths and (b) final dimensional formula of the contraction | ons. 54  |

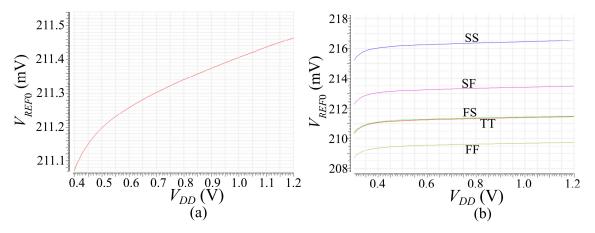

| Figure 26 - (a) $V_{REF0}$ vs $V_{DD}$ for TT corner and (b) for different corners.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54       |

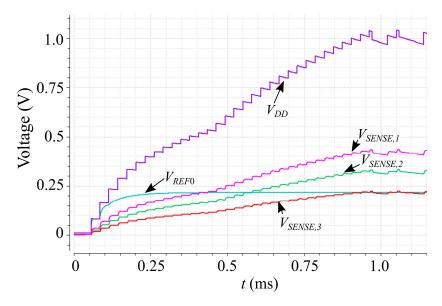

| Figure 27 - Sensed voltages and $V_{REF}$ during $V_{DD}$ buildup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56       |

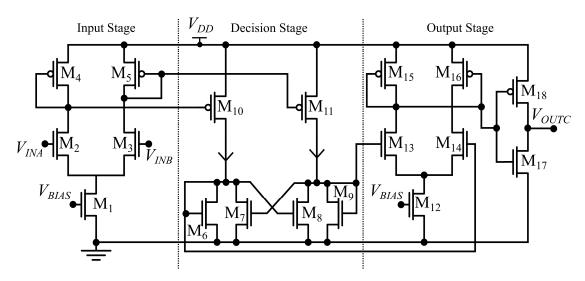

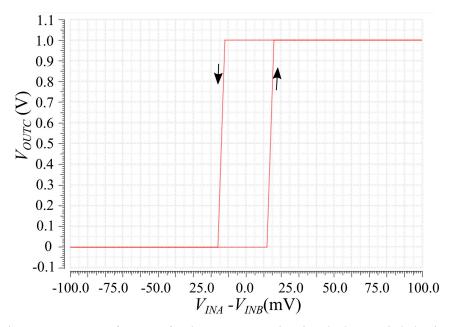

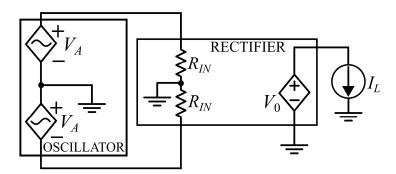

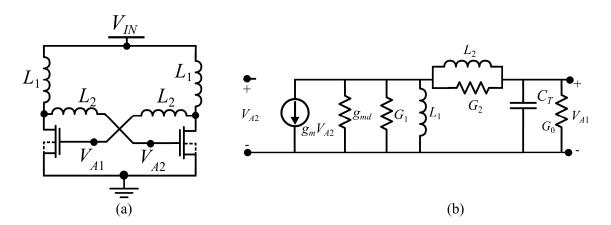

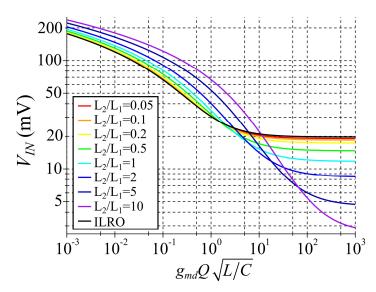

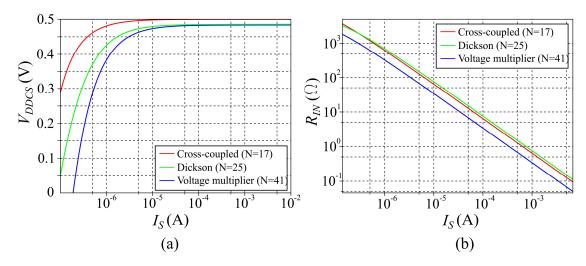

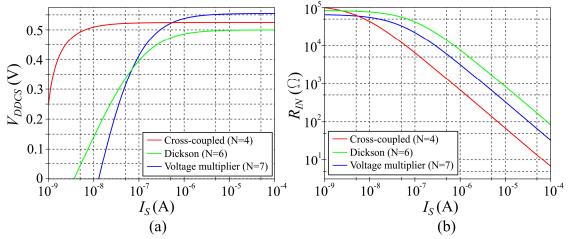

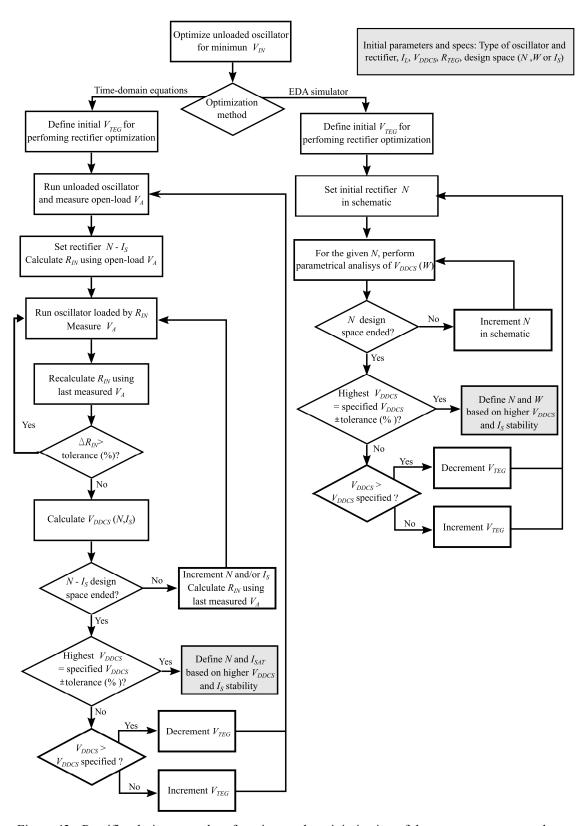

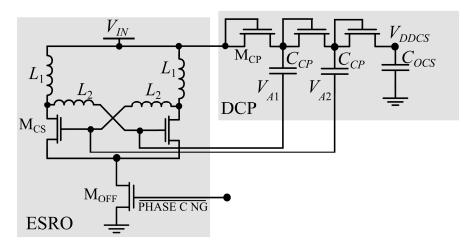

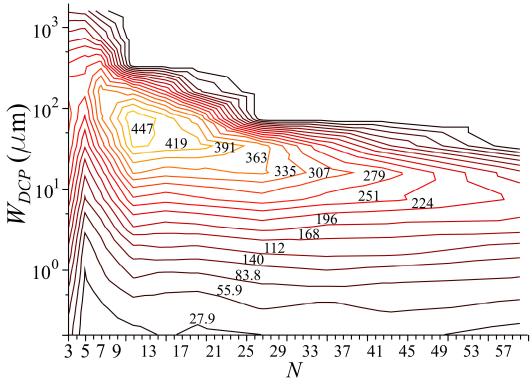

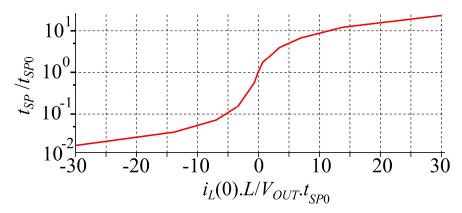

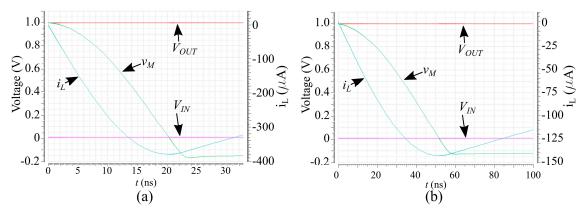

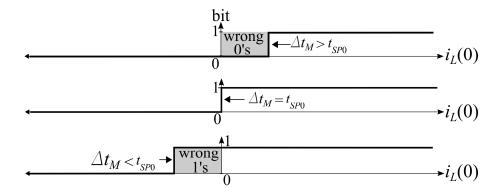

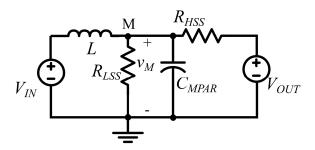

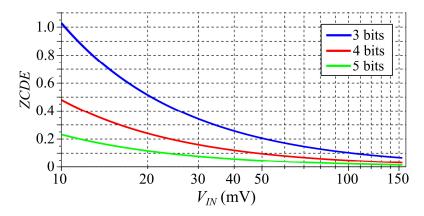

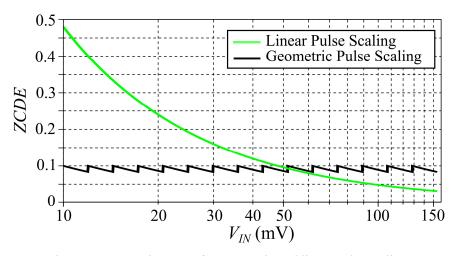

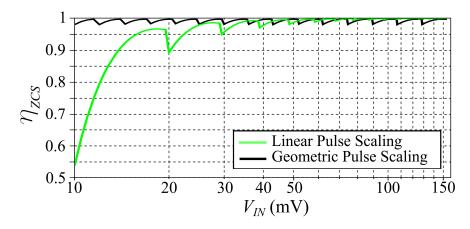

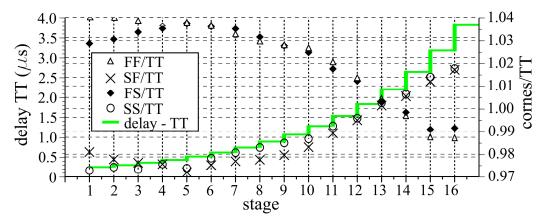

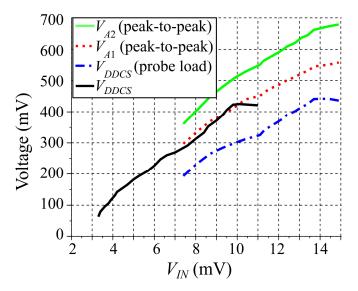

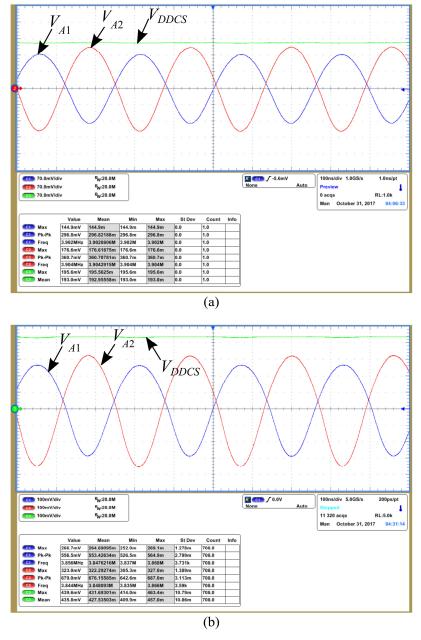

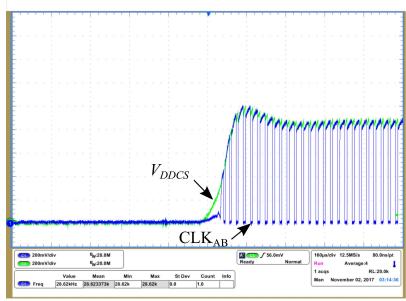

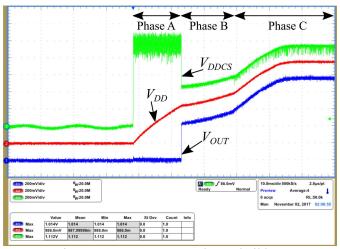

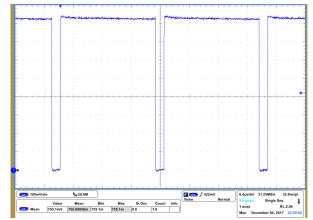

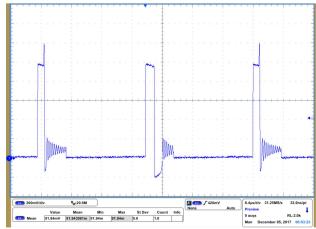

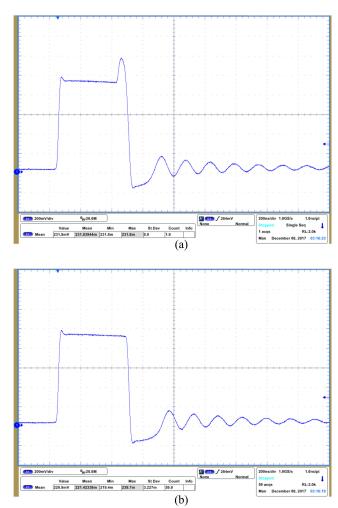

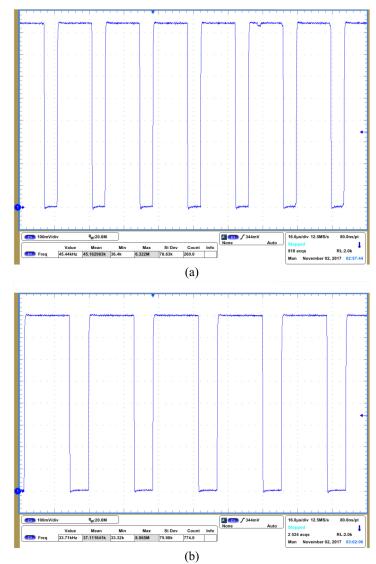

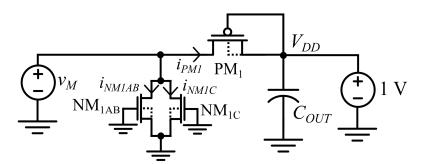

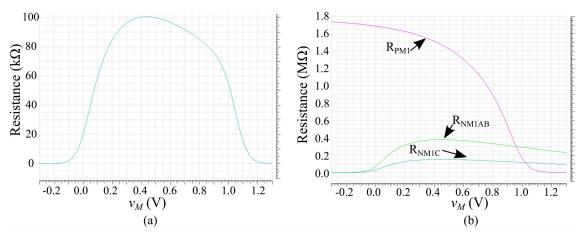

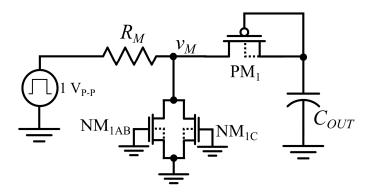

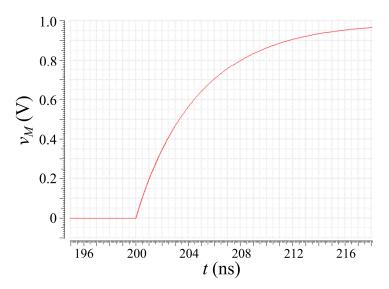

| Figure 28 - Comparator schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56       |