# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO DEPARTAMENTO DE INFORMÁTICA E ESTATÍSTICA CIÊNCIA DA COMPUTAÇÃO

João Fellipe Uller

A Simple MPI Library for Lightweight Manycore Processors

# João Fellipe Uller

# A Simple MPI Library for Lightweight Manycore Processors

Trabalho de Conclusão do Curso do Curso de Graduação em Ciência da Computação do Centro Tecnológico da Universidade Federal de Santa Catarina como requisito para obtenção do título de Bacharel em Ciência da Computação.

Orientador: Prof. Márcio Bastos Castro, Dr. Coorientador: Pedro Henrique Penna, Me.

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Uller, João Fellipe

A Simple MPI Library for Lightweight Manycore

Processors / João Fellipe Uller ; orientador, Márcio

Bastos Castro, coorientador, Pedro Henrique Penna, 2021.

117 p.

Trabalho de Conclusão de Curso (graduação) - Universidade Federal de Santa Catarina, Centro Tecnológico, Graduação em Ciências da Computação, Florianópolis, 2021.

Inclui referências.

1. Ciências da Computação. 2. Manycores Leves. 3. Sistemas de Execução. 4. MPI. 5. Computação de Alto Desempenho. I. Castro, Márcio Bastos. II. Penna, Pedro Henrique. III. Universidade Federal de Santa Catarina. Graduação em Ciências da Computação. IV. Título.

# João Fellipe Uller A Simple MPI Library for Lightweight Manycore Processors

Este Trabalho de Conclusão do Curso foi julgado adequado para obtenção do Título de Bacharel em Ciência da Computação e aprovado em sua forma final pelo curso de Graduação em Ciência da Computação.

Florianópolis, 18 de maio de 2021.

Prof. Jean Everson Martina, Dr. Coordenador do Curso

# Banca Examinadora:

Prof. Márcio Bastos Castro, Dr.

Orientador

Universidade Federal de Santa Catarina

Pedro Henrique Penna, Me.

Coorientador

Pontifícia Universidade Católica de Minas Gerais

Prof. Frank Augusto Siqueira, Dr.

Avaliador

Universidade Federal de Santa Catarina

Prof. Odorico Machado Mendizabal, Dr. Avaliador

Universidade Federal de Santa Catarina

This work is dedicated to my colleagues and siblings, who accompanied me througout this course, to my parents, who helped to build the foundation I needed to persevere in life's challenges, to Caroline, that always cheered me up when I needed it most, and finally, to God who made it all possible.

### **ACKNOWLEDGEMENTS**

I would like to thank all those people who helped in any way with the development of this undergraduate dissertation. First, I thank my both advisors, Márcio Bastos Castro and Pedro Henrique Penna, who, from the beginning, had all the attention and commitment to make this the best it could be. I thank for João Vicente Souto and the other colleagues from the research group who also were directly involved in the present work, being an essential part for its execution. In addition, this work was partially supported by Conselho Nacional de Desenvolvimento Científico e Tecnológico – Brasil (CNPq) and by Coordenação de Aperfeiçoamento de Pessoal de Nível Superior – Brasil (CAPES) under the Capes-PrInt Program (grant number 88881.310783/2018-01), to whom I am grateful for the incentive given that fostered the development of the present work.

### RESUMO

Nas últimas décadas, melhorar o desempenho de núcleos individuais e aumentar o número de núcleos de alta potência por *chip* foram as principais tendências na construção de processadores. No entanto, esta combinação levou não apenas a um aumento no poder computacional, mas também a um aumento considerável no seu consumo de energia. Há uma preocupação crescente entre a comunidade científica a respeito da eficiência energética dos supercomputadores modernos. Nos últimos anos, muitos esforços têm sido feitos em pesquisas, buscando soluções alternativas capazes de resolver este problema de escalabilidade e eficiência energética. O desempenho e a eficiência energética providos pelos manycores leves são inegáveis. Contudo, a falta de suporte avançado e portátil para esses processadores, como interfaces padrão de alto desempenho para o desenvolvimento de código portável, torna o desenvolvimento de software um desafio. Atualmente, duas abordagens são empregadas tentando aumentar a programabilidade em manycores leves: Sistemas operacionais (SOs) e sistemas de execução (runtimes). A primeira fornece portabilidade mas expõe interfaces de programação complexas no nível do SO aos desenvolvedores. Já a segunda se concentra em fornecer interfaces ricas e de alto desempenho, as quais são específicas do fabricante e resultam em software não portável. Portanto, as soluções existentes forçam os desenvolvedores a escolher entre a portabilidade do software ou um processo de desenvolvimento mais rápido. Para resolver esse dilema, neste trabalho é proposta uma biblioteca MPI leve e portável (LWMPI) projetada do zero para lidar com as restrições e complexidades dos manycores leves. A LWMPI foi integrada a um SO direcionado a esses processadores, oferecendo assim uma melhor programabilidade e portabilidade implícita para manycores leves, sem incorrer em sobrecargas de desempenho excessivas que inviabilizariam o seu uso. Para fornecer uma avaliação abrangente da LWMPI, foram utilizadas três aplicações de uma suíte de benchmarking representativa, usada para avaliar o desempenho de manycores leves, além de um benchmark sintético. Os resultados obtidos no processador Kalray MPPA-256 revelaram que a LWMPI atinge uma performance e uma escalabilidade de desempenho melhor do que uma solução feita especificamente para essa análise e que se utiliza puramente das abstrações de IPC do Nanvix, ao mesmo tempo em que oferece uma interface de programação mais rica.

Palavras-chave: Manycores Leves. Sistemas de Execução. MPI. Computação de Alto Desempenho.

## ABSTRACT

In the last decades, improving the performance of individual cores and increasing the number of high power cores per chip were the main trends in the construction of processors. However, this combination led not only to an increase in the computing capacity, but also to a considerable growth in energy consumption. There is a crescent concern among the scientific community about the energy efficiency of modern supercomputers. In the last years, many efforts have been made in research, searching for alternative solutions capable of solving this problem of scalability and energy efficiency. The performance and energy efficiency provided by lightweight manycores is undeniable. Although, the lack of rich and portable support for these processors, such as high-performance standard interfaces that deliver portable source codes, makes software development a challenging task. Currently, two approaches are employed trying to improve programmability in lightweight manycores: Operating Systems (OSes) and baremetal runtime systems. The former provides portability but exposes complex OS-level programming interfaces to developers. The latter focuses on providing rich and high performance interfaces, which are vendorspecific and yield to non-portable software. Thus, the existing solutions force software engineers to choose between software portability or a faster development process. To address this dilemma, we propose a portable and lightweight MPI library (LWMPI) designed from scratch to cope with restrictions and intricacies of lightweight manycores. We integrated LWMPI into a distributed OS that targets these processors, thus featuring better programmability and implicit portability for lightweight manycores, without incurring excessive performance overheads that could hinder its use. To deliver a comprehensive evaluation of LWMPI, we relied on three applications from a representative benchmark suite used to assess the performance of lightweight manycores, and a synthetic benchmark. Our results obtained on the Kalray MPPA-256 processor unveiled that LWMPI present better performance and scalability when compared with a specifically made solution that uses the raw Nanvix Inter-Process Communication (IPC) abstractions, while exposing a richer programming interface.

**Keywords:** Lightweight Manycores. Runtime Systems. MPI. High Performance Computing.

# LIST OF FIGURES

| Figure 1 – Multiprocessor conceptual view                                        | 30   |

|----------------------------------------------------------------------------------|------|

| Figure 2 – Multicomputer conceptual view                                         | 31   |

| Figure 3 – Examples of network topologies                                        | 32   |

| Figure 4 $-$ Overview of the Kalray MPPA-256 lightweight many<br>core processor  | 33   |

| Figure 5 – The OpenMP fork-join model                                            | 36   |

| Figure 6 – Conceptual view of the Nanvix microkernel                             | 42   |

| Figure 7 – Portal and Mailbox conceptual views                                   | 44   |

| Figure 8 – Overview of a distributed OS                                          | 45   |

| Figure 9 – Virtualization conceptual view                                        | 46   |

| Figure 10 – Conceptual view of IKC resource multiplexing                         | 47   |

| Figure 11 – Architectural overview of LWMPI                                      | 51   |

| Figure 12 – Overview Message Passing Interface (MPI) process management in       |      |

| LWMPI                                                                            | 60   |

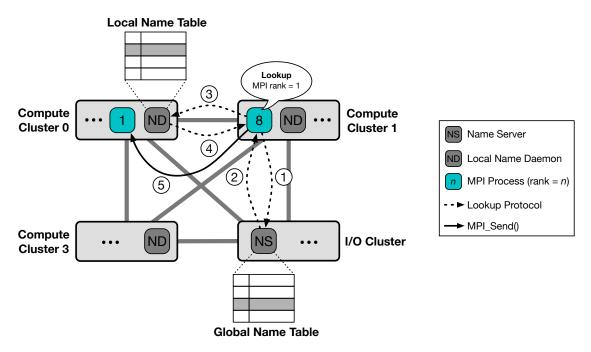

| Figure 13 – Protocol for address lookup and internal structures                  | 63   |

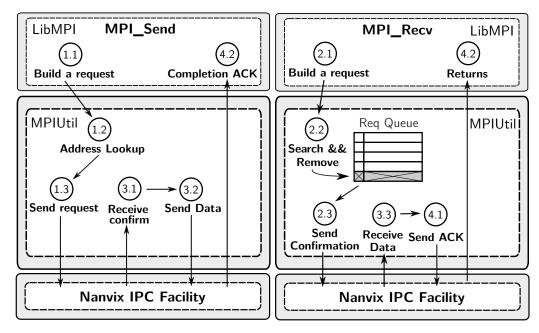

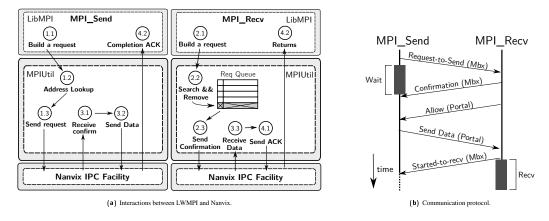

| Figure 14 – Interactions between LWMPI and Nanvix                                | 65   |

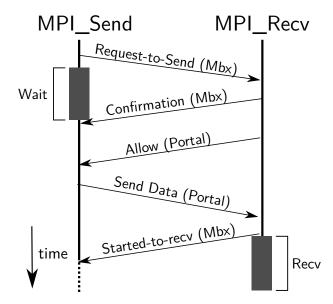

| Figure 15 – Communication protocol                                               | 67   |

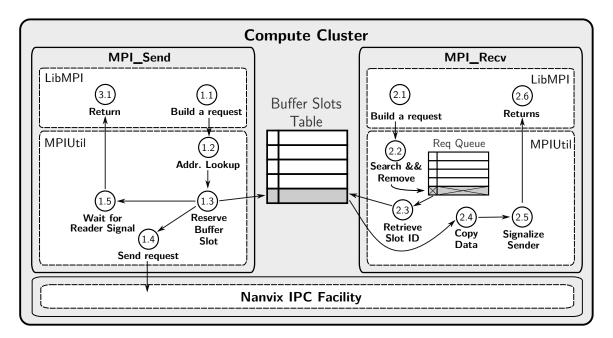

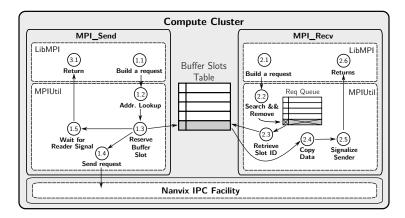

| Figure 16 – Interactions between LWMPI and Nanvix in local communications. $$    | 68   |

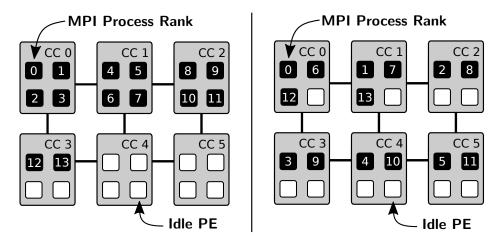

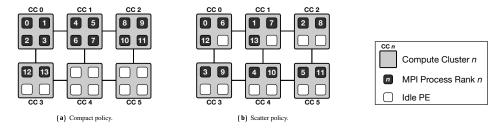

| Figure 17 – Example of <i>compact</i> (left) and <i>scatter</i> (right) policies | 69   |

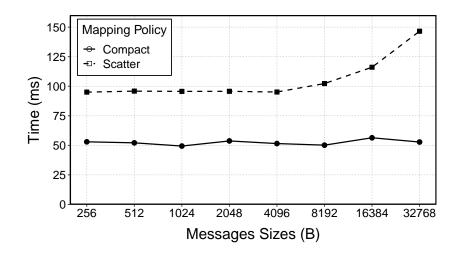

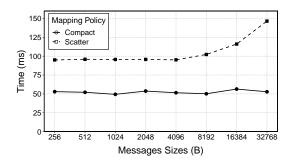

| Figure 18 – Execution times obtained with different MPI process mapping policies |      |

| in a scenario with $12$ MPI processes and the optimized version of LWMPI         | . 75 |

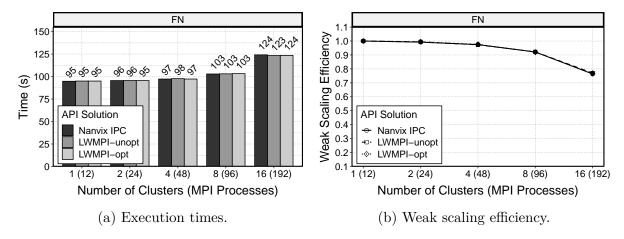

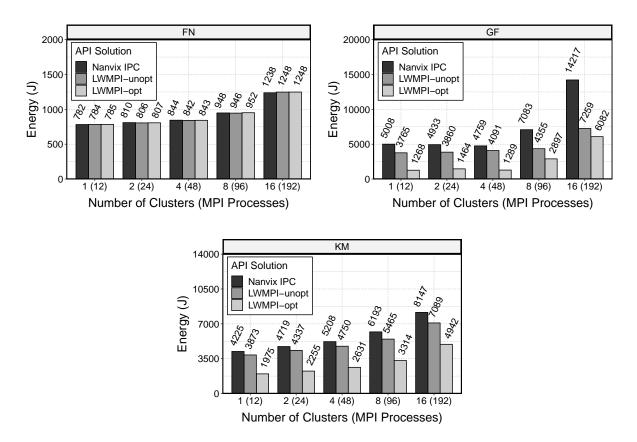

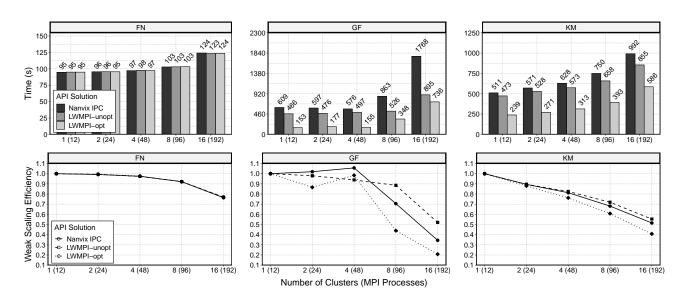

| Figure 19 – FN application results                                               | 76   |

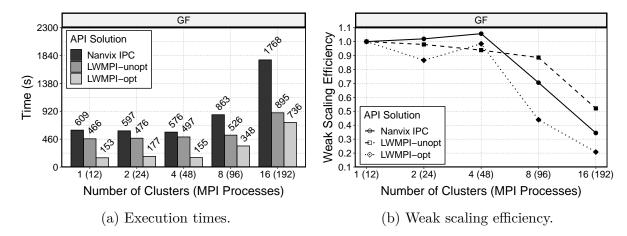

| Figure 20 – GF application results                                               | 77   |

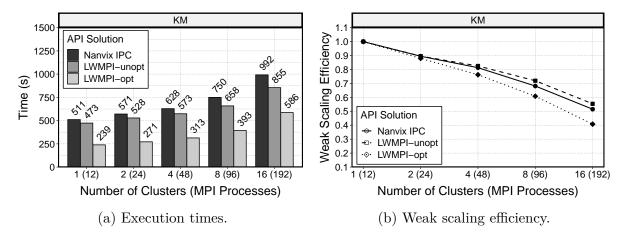

| Figure 21 – KM application results                                               | 78   |

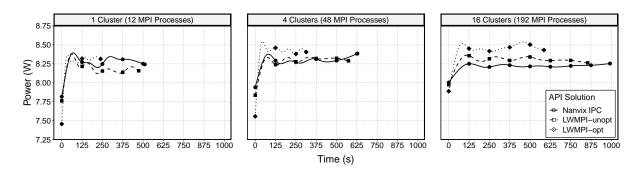

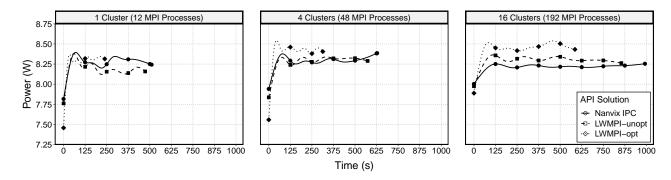

| Figure 22 – Power consumption for K-Means (KM) when varying the number of clus-  |      |

| ters/problem sizes                                                               | 78   |

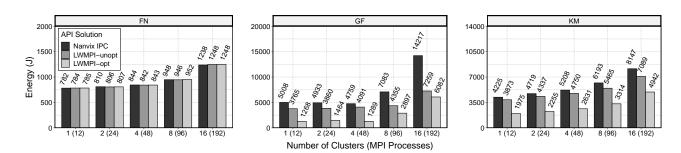

| Figure 23 – Energy consumption for Friendly Numbers (FN), Gaussian Filter (GF)   |      |

| and KM when varying the exp. scenarios                                           | 79   |

# LIST OF TABLES

| Table 1 - | Predefined MPI Groups                              | 55 |

|-----------|----------------------------------------------------|----|

| Table 2 - | Predefined MPI Communicators                       | 56 |

| Table 3 - | Predefined MPI Error Handlers                      | 57 |

| Table 4 - | Predefined C Datatypes                             | 59 |

| Table 5 - | Parameters of synthetic and CAP Bench applications | 73 |

# LIST OF ALGORITHMS

| 1 | MPI_Comm_rank entry point             |

|---|---------------------------------------|

| 2 | mpi_comm_rank underlying function     |

| 3 | mpi_group_rank implementation         |

| 4 | Runtime initialization implementation |

| 5 | Synchronous send implementation       |

| 6 | Receive function implementation       |

# LIST OF ABBREVIATIONS AND ACRONYMS

| AOS   | Asynchronous One-Sided                                                                          |

|-------|-------------------------------------------------------------------------------------------------|

| API   | Application Programming Interface                                                               |

| C-NoC | Control NoC. 33                                                                                 |

| CPU   | Central Processing Unit                                                                         |

| DMA   | Direct Memory Access                                                                            |

| D-NoC | Data NoC                                                                                        |

| DRAM  | Dynamic Random Access Memory                                                                    |

| DSM   | Distributed Shared Memory                                                                       |

| FN    | Friendly Numbers                                                                                |

| GF    | Gaussian Filter                                                                                 |

| GPU   | Graphics Processing Unit                                                                        |

| HAL   | Hardware Abstraction Layer                                                                      |

| НРС   | High Performance Computing                                                                      |

| IKC   | Inter-Kernel Communication                                                                      |

| IPC   | Inter-Process Communication13, 27, 39, 41, 45, 46, 51, 61, 65, 67, 68, 73, 75, 79, 81, 111, 115 |

| KM    | K-Means                                                                                         |

| MIMD  | Multiple Instruction Multiple Data                                                              |

| MISD  | Multiple Instruction Single Data                                                                |

| MPB   | Message Passing Buffer                                                                          |

| MPI   | $Message\ Passing\ Interface15,\ 23,\ 26,\ 27,\ 37,\ 39,\ 40,\ 49,\ 50,\ 51,\ 52,\ 53,\ 54,$    |

|       | 55, 56, 57, 58, 59, 60, 61, 62, 63, 64, 65, 66, 67, 68, 69, 71, 72, 73, 75, 76, 77,             |

|       | 78, 80, 81, 111, 112, 113, 115                                                                  |

| MPSoC | Multiprocessor System-on-Chip                                                                   |

| MW    | Megawatt                                                                                        |

| NoC   | Network-on-Chip25, 26, 32, 33, 46, 47, 61, 67, 69, 72, 73, 76                                   |

| NUMA  | Non-Uniform Memory Access                                                                       |

| OpenMP ARB | OpenMP Architecture Review Board                                                   |  |  |

|------------|------------------------------------------------------------------------------------|--|--|

| OS         | Operating System 13, 26, 27, 34, 35, 40, 41, 43, 44, 45, 46, 49, 50, 51, 53,       |  |  |

|            | 61, 62, 69, 81, 111, 113, 115                                                      |  |  |

| PE         | Processing Element                                                                 |  |  |

| PGAS       | Partitioned Global Address Space                                                   |  |  |

| POSIX      | Portable Operating System Interface 26, 34, 35, 39, 41, 43, 44, 45, 49, 59, 69, 81 |  |  |

| PUC Minas  | Pontifícia Universidade Católica de Minas Gerais                                   |  |  |

| RAM        | Random Access Memory                                                               |  |  |

| RM         | Resource Manager                                                                   |  |  |

| RPC        | Remote Procedure Call                                                              |  |  |

| SIMD       | Single Instruction Multiple Data29                                                 |  |  |

| SISD       | Single Instruction Single Data                                                     |  |  |

| SMP        | Symmetric Multiprocessing                                                          |  |  |

| SPM        | Scratchpad Memory                                                                  |  |  |

| SRAM       | Static Random Access Memory                                                        |  |  |

| UFSC       | Universidade Federal de Santa Catarina                                             |  |  |

| UGA        | Université Grenoble Alpes                                                          |  |  |

| UMA        | Uniform Memory Access                                                              |  |  |

| UPC        | Unified Parallel C                                                                 |  |  |

# CONTENTS

| 1     | INTRODUCTION                                  |

|-------|-----------------------------------------------|

| 1.1   | RESEARCH GOAL                                 |

| 1.2   | CONTRIBUTIONS                                 |

| 1.3   | WORK STRUCTURE                                |

| 2     | BACKGROUND                                    |

| 2.1   | MULTIPLE PROCESSORS COMPUTER ARCHITECTURES 29 |

| 2.1.1 | Multiprocessors                               |

| 2.1.2 | Multicomputers                                |

| 2.2   | LIGHTWEIGHT MANYCORE PROCESSORS               |

| 2.2.1 | Software Development Support                  |

| 2.3   | PARALLEL PROGRAMMING ENVIRONMENTS             |

| 2.3.1 | OpenMP                                        |

| 2.3.2 | MPI                                           |

| 3     | RELATED WORK                                  |

| 3.1   | DISCUSSION                                    |

| 4     | NANVIX OS                                     |

| 4.1   | NANVIX MICROKERNEL 41                         |

| 4.1.1 | IPC Abstractions                              |

| 4.2   | NANVIX MULTIKERNEL                            |

| 4.3   | ENHANCEMENTS IN NANVIX IKC                    |

| 4.3.1 | Virtualization                                |

| 4.3.2 | Resource Multiplexing                         |

| 5     | LWMPI: A MPI LIBRARY FOR LIGHTWEIGHT MANY-    |

|       | CORES                                         |

| 5.1   | DESIGN GOALS                                  |

| 5.2   | OVERVIEW                                      |

| 5.3   | MPIUTIL                                       |

| 5.3.1 | Objects                                       |

| 5.3.2 | Processes                                     |

| 5.4   | LIBMPI                                        |

| 5.4.1 | Runtime Management                            |

| 5.4.2 | Communication Groups                          |

| 5.4.3 | Communicators                                 |

| 5.4.4 | Error Handlers                                |

| 5.4.5 | Datatypes                                          | 57         |

|-------|----------------------------------------------------|------------|

| 5.5   | MPI PROCESS MANAGEMENT                             | 58         |

| 5.6   | THREAD ADDRESSING SCHEME                           | 61         |

| 5.7   | POINT-TO-POINT COMMUNICATION                       | 63         |

| 5.7.1 | Send and Receive Operations                        | 63         |

| 5.7.2 | Request Cycle                                      | 65         |

| 5.7.3 | Communication Protocol                             | 66         |

| 5.7.4 | Local Communication Optimization via Shared Memory | 67         |

| 5.8   | PROCESS MAPPING POLICIES                           | 68         |

| 5.9   | ADDITIONAL CONSIDERATIONS                          | 69         |

| 6     | EVALUATION METHODOLOGY                             | 71         |

| 6.1   | APPLICATIONS                                       | 71         |

| 6.2   | EXPERIMENTAL DESIGN                                | 72         |

| 7     | EXPERIMENTAL RESULTS                               | <b>7</b> 5 |

| 7.1   | IMPACTS OF MPI PROCESS MAPPING POLICIES            | 75         |

| 7.2   | PERFORMANCE EVALUATION WITH CAP BENCH APPLICA-     |            |

|       | TIONS                                              | 76         |

| 7.2.1 | FN Application                                     | <b>7</b> 6 |

| 7.2.2 | GF Application                                     | 77         |

| 7.2.3 | KM Application                                     | 77         |

| 7.2.4 | Energy Efficiency Evaluation                       | <b>78</b>  |

| 7.3   | ADDITIONAL CONSIDERATIONS                          | 79         |

| 8     | CONCLUSIONS AND FUTURE WORK                        | 81         |

|       | BIBLIOGRAPHY                                       | 83         |

|       | APPENDIX A – SCIENTIFIC ARTICLE                    | 89         |

|       | APPENDIX B – LIST OF IMPLEMENTED FUNCTIONS.        | 109        |

|       | APPENDIX C – LWMPI SOURCE CODE EXAMPLES            | 111        |

| C.1   | MPI_COMM_RANK                                      | 111        |

| C.2   | MPI_INIT                                           | 113        |

| C.3   | MPI_SEND AND MPI_RECV                              | 115        |

|       |                                                    |            |

### 1 INTRODUCTION

For many years, the advances in semiconductors technology and computer architecture were enough to meet the growing demands for computational power (LARUS; KOZYRAKIS, 2008). In the last decades, the increase in clock frequency of individual cores or, more recently, in the number of high power cores per chip, were the main trends in the construction of processors. However, the combination of these two approaches led not only to an increase in the architectural complexity of these processors, but also to a considerable growth in their power consumption.

There is a crescent concern among the scientific community about the energy efficiency of modern supercomputers. Kogge et al. (2008) emphasizes that the acceptable power consumption of a supercomputer to reach the *Exascale* is around 20 Megawatt (MW). This would lead to a minimum efficiency of 50 GFlops/W, much more than the most power-efficient supercomputer currently in use. According to Green500 (2020), Preferred Networks MN-3 (PFN, 2020) is the number one in this list performing 21.1 GFlops/W.

In the last years, many efforts have been made in order to study, evaluate and develop different solutions trying to solve this problem of scalability and energy efficiency. In this context, lightweight manycore processors surged to address demands on high performance and energy efficiency (FRANCESQUINI et al., 2015). Processors belonging to this class are classified as Multiprocessor System-on-Chips (MPSoCs), as they group all the components of a computer in a single chip. On the one hand, to deliver high performance and scalability, these processors rely on a distributed memory architecture and interconnections based on rich Networks-on-Chip (NoCs). On the other hand, to achieve energy efficiency, they are built with simple low-power Multiple Instruction Multiple Data (MIMD) cores (ROSSI et al., 2017), also known as Processing Elements (PEs), and Scratchpad Memories (SPMs) (MELPIGNANO et al., 2012) with no hardware coherency support. Moreover, these processors may exploit hardware heterogeneity by featuring PEs (or entire clusters) with different capabilities (DAVIDSON et al., 2018). Some industrysuccessful examples of lightweight manycores are the Kalray MPPA-256 (DINECHIN et al., 2013a), PULP (ROSSI et al., 2017) and the Sunway SW26010 (FU et al., 2016), being the latter employed in the fourth most powerful commercially available supercomputer to date according to TOP500<sup>1</sup> (Sunway TaihuLight).

While the aforementioned architectural features make lightweight many cores more scalable than other parallel processors in both performance and energy efficiency, they introduce several challenges in software programmability. For instance, the *distributed* memory architecture requires a non-trivial software design to handle data access across multiple physical address spaces. Hence, software should explicitly fetch data from remote

https://www.top500.org

memories to local ones to be manipulated (FRANCESQUINI et al., 2015). Furthermore, the *small amount of on-chip memory* demands software to explicitly tile the working data set into chunks and locally manipulate them one at a time (SOUZA et al., 2017). Additionally, it is up to the software to take care of data caching and replication to boost performance. Finally, the rich NoC exposes mechanisms for asynchronous programming to overlap communication with computation (HASCOËT et al., 2017); and hand-operated routing to guarantee uniform communication latencies.

Currently, two approaches are employed to address programmability challenges in lightweight manycores: Operating Systems (KLUGE; GERDES; UNGERER, 2014; AS-MUSSEN et al., 2016; PENNA et al., 2019) and baremetal runtime systems (DINECHIN et al., 2013b; VARGHESE et al., 2014; RICHIE; ROSS; INFANTOLINO, 2017). The former is meant to bridge critical programmability gaps imposed by hardware intricacies. The latter aims to expose a rich, performance-oriented programming environment, narrowed to the underlying architecture. While these two approaches are effective for some use cases, they have a significant duality drawback. Application development directly on top of OS interfaces yields to software portability across architectures, but the actual programming interface provided is complex and delays the software development process. In contrast, baremetal and vendor-specific runtime systems expose richer interfaces that accelerate the development process, but they exclusively concern to the software stack ecosystem of a specific lightweight manycore. As an immediate consequence, software written on top of these higher-level interfaces end up to be non-portable. This way, the software stack for lightweight manycores lacks in programmability, once it fails to provide support for both fast development process and software portability.

## 1.1 RESEARCH GOAL

Based on the aforementioned motivations, the main goal of this undergraduate dissertation is to propose LWMPI: a lightweight and portable MPI library that targets lightweight manycores. We integrated it on top of Nanvix, a Portable Operating System Interface (POSIX)-compliant OS that targets these processors. We believe that combining both of the aforementioned approaches would make possible to our library to provide better programmability and implicit portability for lightweight manycores, without incurring excessive performance overheads that could hinder its use. This work is part of the Nanvix research project, a collaborative project between *Universidade Federal de Santa Catarina (UFSC)*, Pontificia Universidade Católica de Minas Gerais (PUC Minas) and Université Grenoble Alpes (UGA), that aims at the design and implementation of a POSIX-compliant OS for lightweight manycore processors.

### 1.2 CONTRIBUTIONS

This work delivers the following contributions to the state of the art in portable communication libraries for lightweight manycore processors:

- 1. We propose new enhancements to the Nanvix low-level communication primitives to better support the proposed library;

- 2. We propose a simple yet performant lightweight MPI library that leverages the IPC abstractions of Nanvix and includes some of the optimizations of the underlying communication system to reduce the overhead imposed by having an additional software layer;

- We show that the proposed approach has a very low overhead compared to the lowlevel communication primitives when running representative benchmarks on Kalray MPPA-256.

Part of the contributions presented in this work have been published in *Escola Regional de Alto Desempenho da Região Sul (ERAD/RS)* (ULLER et al., 2020b) and in *Simpósio em Sistemas Computacionais de Alto Desempenho (WSCAD)* (ULLER et al., 2020a). The authors of the paper published in WSCAD have been invited to submit an extended version of the paper to the journal *Concurrency and Computation: Practice and Experience*.

# 1.3 WORK STRUCTURE

The remainder of this work is organized as follows. In Chapter 2, we cover the theoretical background needed for the discussion of the present work. In Chapter 3, we discuss the related work. In Chapter 4, we present Nanvix, an open-source distributed OS that targets lightweight manycores, which serves as base for the development of the proposed library. In Chapter 5, we present the developed library and discuss its design and implementation details. In Chapter 6, we detail our evaluation method, while in Section 7 we analyze our experimental results. Finally, we draw our conclusions and discuss our future work in Chapter 8.

### 2 BACKGROUND

In this chapter, we uncover the fundamental concepts related to the present work. In Section 2.1, we discuss concepts that are related to parallel architectures. Next, in Section 2.2, we present the lightweight manycore processors and discuss some of their architectural features, as well as the software development support currently available for them. Finally, in Section 2.3, we present some of the runtime systems that are applicable to lightweight manycores, and that have potential to increase software programmability for this class of processors.

### 2.1 MULTIPLE PROCESSORS COMPUTER ARCHITECTURES

The ever increasing necessity for computational power always pushed the technological advances of modern computers. Nowadays, there are a countless applications that involve a colossal number of operations to be realized, specially those involved in High Performance Computing (HPC). For this reason, modern architectures focus not only on creating faster computers by adding more powerful components, but also on how to organize these resources to better utilize them. This way, they try to achieve the best performance with better efficiency. To understand the variety of parallel architectures available, Flynn (1972) proposed a taxonomy that classifies parallel architectures in four classes, based in their data and instruction flows.

In the Single Instruction Single Data (SISD) class we have sequential machines that operate over a single execution flow, executing at most one instruction per clock cycle and operating over a single data stream. This way, these machines exploit no parallelism in any of these streams, like single core machines. Next, in the Multiple Instruction Single Data (MISD) class we have machines that execute multiple instructions flows over a single data stream. This is the most uncommon class, and it is difficult to find examples of real systems that belong to this class, but critical systems that need fault tolerance may implement this characteristic. The third class is the Single Instruction Multiple Data (SIMD), that describes computers that are able to apply a single instruction over multiple data streams simultaneously. These computers use hardware replication to achieve this characteristic, and a good example of such machines are the Graphics Processing Units (GPUs). Finally, the MIMD class describes machines that have multiple Central Processing Units (CPUs), where each CPU is capable to execute multiple instructions over multiple data streams, simultaneously, i.e., multiple processes may run on these processors independently and in parallel. Actually, this is the class where most of the modern multiprocessors are included, like the CPUs from Intel and AMD.

In the present work, we are particularly interested in architectures that are capable to support MIMD workloads. There are two main groups that fall into this class, which we present in the next subsections: *multiprocessors* and *multicomputers*.

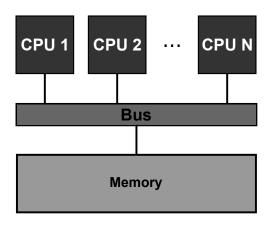

Figure 1 – Multiprocessor conceptual view. Source: Adapted from Tanenbaum & Bos (2014).

# 2.1.1 Multiprocessors

Shared-memory multiprocessors are computing systems where two or more CPUs share full access to a common Random Access Memory (RAM) (TANENBAUM; BOS, 2014). Figure 1 illustrates this type of system, in which all CPUs share the same interconnection to access the shared memory module. Additionally to the shared memory, each CPU may have its local cache to reduce access contention to the main memory.

In general, this type of system takes advantage of high rates of parallelism having multiple execution streams. However, since this multiple processors may access the same memory regions, this parallelism may lead to concurrency issues and race conditions, if no synchronization mechanisms are provided. The communication between the different processes is achieved using shared memory regions. For that, the communicant sides agree in a common structure landed in a common memory region, that is read/written when they want to communicate with one another.

According to memory accesses, multiprocessed architectures can be classified into two main classes: Uniform Memory Access (UMA) architectures, where all CPUs have the same latency in memory accesses; and Non-Uniform Memory Access (NUMA) architectures, at which processors may experience different latencies when accessing memory.

In the case of UMA architectures, the memory is centralized and shared across all CPUs, with the characteristic of having the same access latencies for all processors, independently of the interconnection type. The first UMA architectures were bus-based. However, the bus becomes a bottleneck as the number of interconnected processors grows up. This way, crossbar switches and multistage switching networks have become other possibilities for interconnection in these architectures.

Even so, the number of CPUs in UMA multiprocessors is limited to a few dozens. NUMA multiprocessors, on the other hand, offer much more scalability in terms of the number of processors in the same architecture. This type of system stills being characterized by a single address space that is common to all CPUs, but these CPUs may

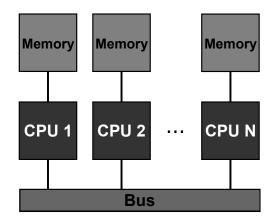

Figure 2 – Multicomputer conceptual view. Source: Adapted from Tanenbaum & Bos (2014).

have different access latencies, depending on which memory bank is accessed. NUMA architectures are constructed on top of an interconnection that connects multiple NUMA nodes, where each node has its CPUs and close memory bank that is still accessible to CPUs that are external to the node, at the cost of higher access latencies.

Multiprocessors are popular since they are easier to program. The shared memory makes communication and synchronization much simpler, since any process may achieve this functionalities by simply using shared memory regions. However, building large multiprocessors is difficult and may be very expensive, once the architecture becomes much more complex (TANENBAUM; BOS, 2014). The alternative to keep increasing the number of cores of an architecture is to construct it as a multicomputer.

### 2.1.2 Multicomputers

Multicomputers are computational systems where the basic components are elementary computers. Each node of this type of system consists in one or more multiprocessors, a local memory module and at least one interface that is used to communicate with the rest of the system. In this type of architecture, a processor has access only to its local memory. To access data that is not locally present, it needs some message passing mechanisms to explicitly communicate with the other nodes. Figure 2 illustrates this type of architecture, in which each CPU has access to its local memory module and a high-performance network interconnects the CPUs.

This approach makes it possible to integrate up to thousands of nodes under the vision of a single clustered architecture. This type of system relieves the burden of providing a single address space and cache coherency across all CPUs in exchange for the problem of providing fast networks and high-speed communication interfaces. However, the goal now is to provide message passing in the microsecond scale, instead of nanosecond in the case of shared memory, being much simpler and cheaper (TANENBAUM; BOS, 2014).

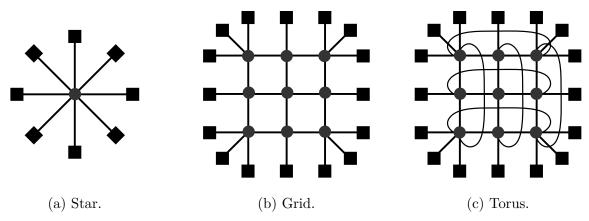

Figure 3 – Examples of network topologies.

Source: Adapted from Tanenbaum & Bos (2014).

To interconnect the nodes of a multicomputer, a switch set of a high-performance network may be organized into a variety of topologies, according to the intended characteristics. For small systems, a single switch in a star topology may be cheaper to implement and also fulfill the system necessities. Commercially used multicomputers, however, generally adopt bi- or even tri-dimensional topologies like mesh, torus or cube that have better scalability and regular behavior to interconnect multiprocessor systems. Figure 3 illustrates some examples of traditional network topologies.

In software, there is the necessity of message passing mechanisms to enable explicit communication between the nodes. There is a variety of options to implement such mechanisms: a *send/receive* library that can be synchronous or asynchronous, depending on the hardware available; Remote Procedure Call (RPC) calls (NELSON, 1981); or even some mechanism that implements Distributed Shared Memory (DSM) notions (NURN-BERGER et al., 2014; CHEN et al., 2011), which offers the illusion of shared memory on top of the distributed memory system implemented by the architecture.

# 2.2 LIGHTWEIGHT MANYCORE PROCESSORS

Lightweight manycores are a new class of manycore processors that have an endeavor to deliver high performance and energy efficiency in a single die. Considering the aforementioned classification, lightweight manycores can be seen as multicomputer systems on a chip. To achieve this, they rely on specific architectural features such as:

- i thousands of low-power cores;

- ii MIMD capability;

- iii tightly-coupled groups of cores (aka *clusters*);

- iv distributed memory architecture and small local memories;

- v reliable and fast NoCs for message-passing; and

- vi heterogeneous processing capabilities in I/O and computing clusters.

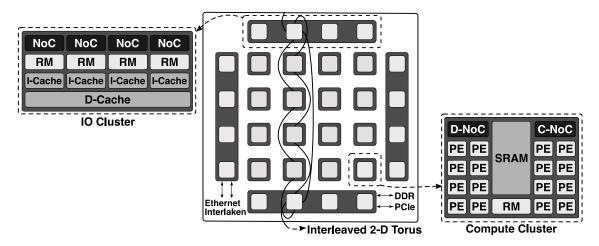

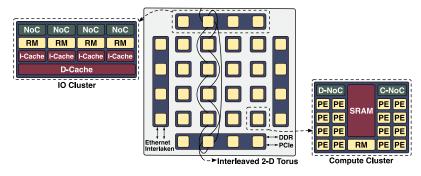

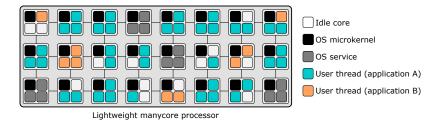

Figure 4 – Overview of the Kalray MPPA-256 lightweight manycore processor. Source: (PENNA; FRANCIS; SOUTO, 2019)

To provide substantial insight on lightweight manycores, we consider in the present work an industry-successful example of such type of processor: the Kalray MPPA-256 (DINECHIN et al., 2013a). Notwithstanding, the following discussion extends to other lightweight manycores (ROSSI et al., 2017; FU et al., 2016). Figure 4 presents an overview of this processor. Overall, Kalray MPPA-256 integrates 256 general-purpose cores and 32 firmware cores, called PEs and Resource Managers (RMs), respectively, totalizing 288 cores. These cores are disposed into 20 clusters, being 16 Compute Clusters, intended for general-purpose processing, and 4 I/O Clusters, intended for general I/O connectivity, being two of these clusters connected to the Dynamic Random Access Memory (DRAM), and two with PCI/Ethernet controllers. Each cluster is composed of heterogeneous and limited hardware capabilities to perform different roles. For instance, I/O Clusters have four RMs, four NoC interfaces, and 4 MB local Static Random Access Memory (SRAM) to exchange data with external resources and internal clusters. Differently, Compute Clusters have one RM, 16 PEs, one NoC interface, and only 2 MB local SRAM to run user workloads. Cores within the cluster share and have uniform access to hardware resources.

Communication between clusters is exclusively achieved by explicitly exchanging hardware-level messages through two NoCs. Specifically, the Control NoC (C-NoC) enables synchronization and small control messages handover, whereas the Data NoC (D-NoC) supports arbitrary-sized data exchanges. At this point, the I/O heterogeneity among clusters becomes more evident. I/O Clusters have direct access to the attached DRAM or a device, while Compute Clusters must tile their data into messages and send them through the NoC using an I/O Cluster as an intermediary to access these resources. To improve communication performance, Kalray MPPA-256 features a built-in Direct Memory Access (DMA) engine in its NoC interfaces to enable asynchronous communications and higher bandwidth for dense data transfers.

To summarize, the aforementioned set of architectural features grants important distinctions between lightweight manycores and other well-known manycore processors:

- Manycore processors such as Intel Xeon Phi, Tilera TILE-Gx100 and Intel Single-Cloud Computer do not have a constrained memory system, with a distributed architecture and small local memories;

- Symmetric Multiprocessing (SMP) architectures based on NUMA design are built with multiple CPU packages interconnected by a dedicated hardware outside of the processor chips (e.g., NUMAlink); and

- GPUs do not cope efficiently with MIMD workloads.

# 2.2.1 Software Development Support

The paradigm breakthrough brought by lightweight manycores allows computer systems to scale their performance and energy efficiency. However, challenges introduced by their architectural intricacies to software programmability impact from low- to user-level applications. Examples of these challenges are dark silicon (HAGHBAYAN et al., 2017), data prefetching and tiling (FRANCESQUINI et al., 2015), asynchronous communication (HASCOËT et al., 2017), non-coherent caches (DINECHIN et al., 2013a) and application deployment (SOUZA et al., 2017).

The challenges that arise from the architectural characteristics of lightweight manycores make better development environments an important requirement to porting software for these processors. To do that, there are two approaches currently employed to provide better programmability in lightweight manycores: OSes and baremetal runtime systems.

OSes are meant to bridge critical programmability gaps in architectures. To this end, they provide resource sharing and multiplexing mechanisms, as well as they expose rich abstractions to user-level applications. Inherently due to the architectural features of lightweight manycores, OSes for these processors embrace a distributed design to achieve scalability (BOYD-WICKIZER et al., 2010). In this approach, the OS is factored in a set of services, each of which is deployed on a core of the parallel architecture. Cores that do not run OS services are made available to user-level applications.

Multiple architectures and implementations for a distributed OS are possible, each one targeting a specific set of design goals and constraints. However, a three-tier approach is commonly adopted by distributed OSes for lightweight manycores such as MOSSCA (KLUGE; GERDES; UNGERER, 2014), M³ (ASMUSSEN et al., 2016) and Nanvix (PENNA et al., 2019). In the bottom layer, a generic and flexible Hardware Abstraction Layer (HAL) enables portability across different processor architectures. A microkernel lies in the middle layer and provides minimum system abstractions, handles local resource multiplexing and ensures security policies. Finally, in the top layer, runtime OS libraries expose a standard interface to user-level applications such as POSIX.

In contrast to OSes, baremetal runtime systems aim at exposing a rich programming environment that is narrowed for the underlying architecture. In general, they implement only essential primitives that manage the hardware to avoid unnecessary overheads to the application or fit a specific programming model design. Usually, they are provided on top of the hardware as libraries and are directly linked with applications. As an immediate consequence, baremetal runtime systems may not hide low-level aspects of the underlying architecture. Moreover, they do not provide important abstractions that are usually implemented by OSes, such as virtual memory, resource sharing, core multiplexing and others. For instance, they do not enable multiple applications to be concurrently deployed in the processor nor provide mechanisms to time-share the hardware between different applications.

Overall, runtime systems are usually shipped by manufacturers of lightweight manycore processors as a cutting-edge performant programming environment. Programming models or well-known standards often guide the Application Programming Interface (API) of the runtimes to benefit a specific set of applications. For instance, NodeOS (DINECHIN et al., 2013b) uses the *pipe-and-filter* programming model to allow processes to communicate on Kalray MPPA-256. The primitives exported by NodeOS resemble the classical POSIX pipes interface, but they require specific knowledge from developers. Differently, libasync (HASCOËT et al., 2017) implements the Asynchronous One-Sided (AOS) communication and synchronization model for Kalray MPPA-256 inspired by libraries used in the HPC domain. The AOS layer defines put/get and atomic operations over requisition queues, allowing applications to read/write data from/to remote memory segments. This model mitigates the problems derived from small local memories in Kalray MPPA-256. However, this approach is focused on enhancing the overall performance of applications, putting aside all programmability and portability issues in lightweight manycores.

### 2.3 PARALLEL PROGRAMMING ENVIRONMENTS

As most of the modern parallel architectures have been evolving in recent years, better programming environments are needed to help the programmer to explore all the possibilities of parallelism that are offered by these architectures. To ease the software development and to reduce the time needed to develop parallel programs, an increasing effort has been made to make available ports of standard APIs for the most varied parallel architectures.

These programming environments not only make the software development an easier task, but also help the programmer to extract better performance from the underlying hardware. In the next subsections, we describe some of these standard programming environments that are used in the development of HPC applications.

# 2.3.1 OpenMP

OpenMP is a multi-platform API that intends to provide an easy way to take advantage of parallelism and multiprocessing in shared memory and distributed shared memory architectures. It consists in a set of compiler directives, library routines and environment variables for parallelism in C, C++ and Fortran, that influence the runtime behavior of an application (BOARD, 2020). Its specification is defined and maintained by the OpenMP Architecture Review Board (OpenMP ARB), a consortium composed mostly by hardware and software vendors.

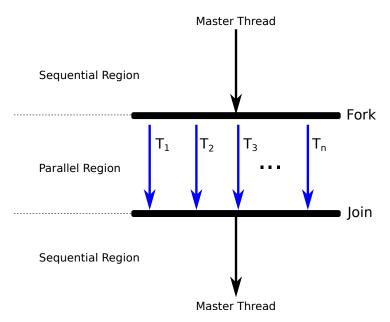

To perform a program parallelization, the OpenMP API implements a fork-join parallel model. All OpenMP programs start execution with a single thread (the master thread), which sequentially executes the program flow until the definition of a parallel region. When a definition of such type of region is encountered, the master thread will fork and create a team, that includes itself and other worker threads to execute in parallel the code inside the parallel region. When this team of threads finishes its execution at the end of the parallel region, all the worker threads are synchronized and rejoined by the master thread, that continues sequentially its execution. Figure 5 illustrates the described process, in which the master thread and N-1 other worker threads execute a parallel region. Then, all worker threads are joined at the end of the parallel region.

To define a parallel region, OpenMP makes use of a set of compiler directives, where the programmer specifies which regions will be executed in parallel by simply adding these directives in the sequential code. This way, it is easy to parallelize a sequential program in an incremental way (CHAPMAN; JOST; PAS, 2007), inserting compiler directives in small portions of the sequential code, testing if the execution still correct and repeating this process until the desired performance is achieved. Additionally to the compiler directives, OpenMP also defines library routines and environment variables that may be used by the programmer to specify how the parallel execution must behave. This gives a finer control and a better view to the programmer about the parallelism being exploited in the parallel execution.

#### 2.3.2 MPI

The MPI is a portable standard specification for libraries that implement the message passing programming model. It is the *de facto* standard for message passing in HPC, and broadly used in supercomputing and parallel programming. The MPI standard is defined and maintained by the MPI-Forum<sup>1</sup>, a group of researchers that includes both people from academia and from industry in its lines. Currently, the most recent official release of the specification is the 3.1 version<sup>2</sup>, from June, 2015, with drafts of a possible 4.0

<sup>&</sup>lt;sup>1</sup> MPI-Forum website: https://www.mpi-forum.org

<sup>&</sup>lt;sup>2</sup> MPI 3.1 Spec available at: https://www.mpi-forum.org/mpi-31/

Figure 5 – The OpenMP fork-join model. Source: Developed by the author.

version being released for discussion in the last few years. Also, there are some open-source implementations of MPI available in public domains, such as MPICH<sup>3</sup> and OpenMPI.<sup>4</sup>

One of the strong points of MPI is its flexibility. It can be applied to various supercomputers and parallel architectures, ranging from shared memory multiprocessors to distributed memory multicomputers (WU et al., 2013). Programs in MPI run as multiple processes, where each process has its own address space and communication occurs through an interconnection network. At the same time, it is important to note that it is flexible enough to be used in shared memory architectures handling the communications as read/write operations in shared memory. Another strong point from MPI is its standardization. A programmer that writes an MPI application may run it in any computer that has the MPI library installed, without making any additional changes to the source code (MUTTIL; LIONG; NESTEROV, 2007). So, MPI is also a way of providing portability across architectures, since there have been existing efficient MPI implementations on a wide range of platforms. Additionally, it presents good scalability in heterogeneous systems, as the processes offer a standardized and homogeneous view of the nodes in the system. This way, communication can be handled efficiently, regardless of the underlying hardware implemented.

The MPI standard includes in its specification functions for point-to-point communication, collective operations that are made on top of groups of processes specified by the user, communication domains to specify different universes of communication, virtual topologies to establish different patterns of communication in collective calls, environmental management, a profiling interface and code bindings for Fortran and C.

<sup>&</sup>lt;sup>3</sup> MPICH Website: https://www.mpich.org/

OpenMPI Website: https://www.open-mpi.org/

Point-to-point communications are made directly between the involved processes. It can be both synchronous or asynchronous, blocking or non-blocking, and it may use different communication modes, based on the resources exposed by the underlying hardware. These advanced topics, involving the semantics and configuration of point-to-point communication in MPI will be discussed in more depth in Section 5.7, when we discuss the implementation details of point-to-point communication in the proposed library.

### 3 RELATED WORK

Software development for lightweight manycores is challenging because it strives in finding the balance between performance and programmability. On the one hand, each new layer inserted in the software stack consumes a small part of the hardware resources of the architecture. In lightweight manycores, where some of these resources, such as local memory, are scarce and need to be used wisely, onerous development environments may result in significant performance degradation. In extreme situations, this degradation may even lead to the infeasibility of the solution. On the other hand, programmability is also an important requirement for lightweight manycores, due to all of their intricacies. Otherwise, porting applications to this class of processors may become a painful task.

In this context, and specifically concerning communication, there are two approaches currently employed that try to alleviate this problem:

- i vendor-specific communication libraries, which expose a performance-oriented interface for the underlying architecture; and

- ii industry-standard communication libraries, which provide a richer communication interface, in exchange for some performance penalty.

Vendor-specific solutions mostly rely on specific features of the underlying hardware to achieve high performance. For instance, synchronous (WIJNGAART; MATTSON; HAAS, 2011) and asynchronous (CLAUSS et al., 2011) interfaces are provided on top of Message Passing Buffer (MPB) for the Intel Single-Cloud Computer. On the other hand, Kalray MPPA-256 features both a communication library that shares some similarity with POSIX (DINECHIN et al., 2013b) and a specific interface for one-sided communications (HASCOËT et al., 2017). A high-level message-oriented parallel programming model is provided for the IMAPCAR (KELLY; GARDNER; KYO, 2013). Finally, a specific communication API is provided for the Adapteva Epiphany processor (VARGHESE et al., 2014).

In contrast, standard communication interfaces benefit from extensive improvements and optimizations, making them a solid choice for programming lightweight many-cores. However, to the best of our knowledge, all standard communication interfaces ports are built on top of low-level primitives and libraries provided by the vendors of these processors, making it difficult to adapt them to other manycore processors. Examples of such solutions are those based on the Partitioned Global Address Space (PGAS) programming model, such as the Unified Parallel C (UPC) port for the Intel Single-Cloud Computer (GAMELL et al., 2012) and Tilera TILE64 (SERRES et al., 2011) processors as well as the OpenSHMEM implementation (ROSS; RICHIE, 2016) for the Adapteva Epiphany processor. Moreover, there have been some efforts on providing an MPI port for Kalray MPPA-256 (HO et al., 2015) and Adapteva Epiphany (RICHIE; ROSS; IN-FANTOLINO, 2017). The former is the closest work to the present one, also presenting

an implementation from scratch to cope with the restrictions of lightweight manycores, having similar concepts to those adopted in the present work. The main difference, however, is the fact that it is implemented on top of a vendor-specific IPC library, and so, being not portable to other processors/architectures. The latter, in addition, does not conform with the MPI standard.

## 3.1 DISCUSSION

Overall, both of the aforementioned approaches lack application portability. On the one hand, there are very efficient solutions (i.e., vendor-specific libraries) that perfectly adhere to the design purposes of lightweight manycores, but require a greater effort in learning and software design time. On the other hand, there are well-known and widely used standards that alleviate portability problems and improve project development. However, implementations of these interfaces use baremetal facilities, making the entire standard stack architecture-dependent and difficult to be adapted to other lightweight manycores.

For this reason, this work takes a step further on providing a flexible and extendable implementation of a well-known parallel programming standard (MPI) on top of an open-source OS for lightweight manycores (Nanvix). We rely on an OS to provide rich hardware management, sharing and multiplexing and we implement and deploy a high-level, industry-standard library on top of this OS. We believe that the proposed solution brings the best of the aforementioned approaches, since it offers a standard high performance solution with implicit portability, that can be used in a broad range of lightweight manycores or easily adapted to be implemented on top of other runtime systems.

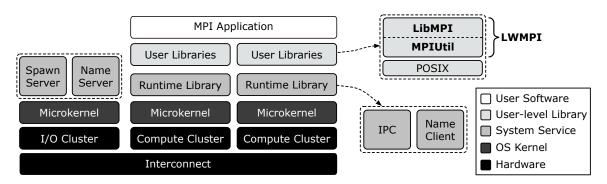

### 4 NANVIX OS

Nanvix<sup>1</sup> is an open-source research OS that aims at addressing the intricacies of lightweight manycores (PENNA et al., 2019). It is a POSIX-compliant OS designed from scratch to be compatible with this new class of processors, seeking for the balance between performance, portability and programmability. Nanvix adopts a distributed multikernel structure that consists in multiple instances of asymmetric microkernels, i.e., each cluster has a single core dedicated exclusively to executing the kernel, leaving the other cores for general-purpose computing.

In this chapter, we highlight some concepts and details of the Nanvix structure that are important to the present work, specially some related to the Nanvix Microkernel (Section 4.1) and the Multikernel (Section 4.2). Additionally, in Section 4.3 we present some enhancements that were made by us into Nanvix, in the context of the present work, in order to make it possible to implement LWMPI on top of the Nanvix IPC module.

## 4.1 NANVIX MICROKERNEL

The Nanvix OS implements a microkernel design, where a minimal version of a basic OS kernel provides resource management, sharing and multiplexing, security, minimum OS services, as well as resource abstractions and primitives at a cluster level (PENNA et al., 2019). This way, it provides the basic functionality to offer support for the implementation of more complex OS services in the user-level space, while keeping a small memory footprint for the kernel itself.

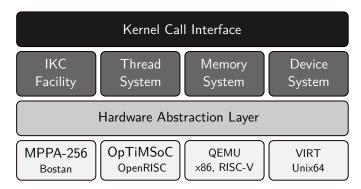

Figure 6 shows an overview of the layers structure adopted by the Nanvix Microkernel. In the lower level, we have the baremetal architectures supported by Nanvix, i.e., Kalray MPPA-256 (DINECHIN et al., 2013a), OpTiMSoC (WALLENTOWITZ et al., 2012), x86 and RISC-V emulated in QEMU, and a special platform for development that is a virtualization on top of Unix64. On top of them, a HAL is the responsible for abstracting the underlying hardware and providing an uniform interface for the above kernel layers. This way, this layer enables portability for the entire kernel, making it compatible with all the abstracted architectures. On top of the HAL, we have the Modules Layer that represents the core of the Nanvix Microkernel, in which are implemented the kernel functionalities and capabilities. Currently, four modules are implemented in the Nanvix microkernel:

• Thread System: provides a kernel thread abstraction. Kernel threads run in uninterruptible mode and have exclusive access to a core. It features scheduling, multiplexing and management functionalities to cooperative user threads that are implemented on top of these kernel threads.

Publicly Available at: https://github.com/nanvix

Figure 6 – Conceptual view of the Nanvix microkernel. Source: (PENNA et al., 2019)

- Memory System: provides rich memory management in a cluster, as well as a virtual memory extension that supports different page sizes and permissions tracking.

- **Device System**: controls the access permissions to memory and port mapped devices. Moreover, it exports routines for reading/writing data from/to these devices and for implementing device drivers at user space.

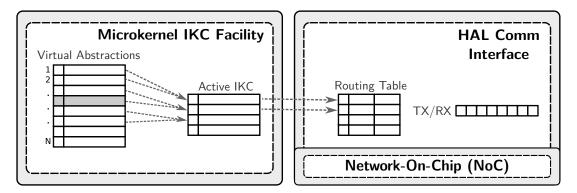

- Inter-Kernel Communication (IKC): provides simple abstractions and primitives to carry out inter-cluster communication. All the abstractions provided operate in a synchronous behavior, but may also include an asynchronous mode in lightweight manycores that feature a DMA engine.

On top of the Modules Layer, the Kernel Call Interface exposes the functionalities implemented by each module to the user space. This layer represents the entry point to the Nanvix kernel from the user perspective, and at this level are performed the verifications and parameters checking that help to provide security in the kernel space. Also, it is in this level where the control flow of the system calls is defined, and where the asymmetric characteristic of the Nanvix kernel is handled: complex routines of the kernel modules are executed exclusively by the master core, while simpler ones can be handled locally by the core that called the specific routine.

### 4.1.1 IPC Abstractions

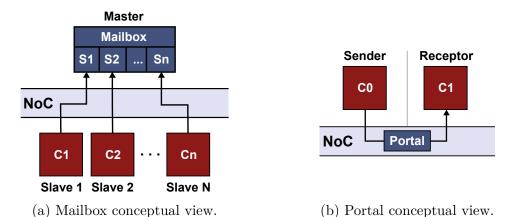

To enable inter-cluster communication, the Nanvix IKC exposes three basic message passing abstractions, to explicitly control the data flow across the kernel: *Mailbox*, *Portal* and *Sync*. These abstractions are designed to generalize three common behaviors that are observed in distributed systems: transferring small fixed-size control messages (Mailbox); handling dense data transfers (Portal) and building synchronization points (Sync) (SOUTO et al., 2020). Also, they can be used together, as building blocks, to compose more complex protocols and to construct runtime services. In this section, we give an overview on these abstractions, since they are the base to implementing the communication protocols on the upper layers, including those used by the proposed library.

### Mailbox

The Mailbox abstraction (similar to POSIX *Message Queue*), is intended to enable the exchange of small fixed-size control messages with low latency. These messages have their size fixed, generally, in a few hundreds of bytes, and may be handled asynchronously, depending on the abstraction usage.

To receive incoming messages, the receiver allocates a message queue with sufficient space to receive exactly one message from each possible sender. This way, each sender have its predefined space to communicate with an input mailbox, as we can see in Figure 7a. When this buffer is already occupied by a previous message, the sender must wait for the first one to be consumed by the receiver before transferring the new message, revealing the synchronous behavior of the abstraction. When the receiver wants to read a message from its incoming mailbox, it may specify the sender from which it wants to receive, or read any available message on the allocated buffer. If no message is available, it blocks waiting for a message to arrive.

In a distributed OS context, this abstraction can be used to implement the agreement phase between client and server of a given OS service, where the client makes a requisition encoding the desired operation and necessary parameters, for example.

### Portal

The Portal abstraction (similar to POSIX *Pipe*) provides arbitrarily-sized messages to be transferred with high bandwidth between two nodes. This abstraction is intended for dense data transfers from one cluster to another in an unidirectional channel, as we can see in Figure 7b. When a remote process wants to write data to an input portal, it needs to receive explicit authorization from the receiver. When the receiver wants to read a message from the channel, it specifies from which node it wants to receive data, and then, it grants the permission to write to that node using a special kernel call. If the remote node is not ready to send, the receiver blocks until it starts to receive data through the channel. The sender, in its side, may block in a write call until it receives the authorization from the receiver in the form of an allow signal, that signalizes it can start to send the data. Since this abstraction is totally synchronous, there is no necessity for intermediary buffering. The communication is configured using memory buffers passed as parameters by the user, consuming no additional memory to carry out the dense data transfers.

In the context of a distributed OS, this abstraction may be used as the main building block to carry out the data transfers across the system, since it is designed to handle the dense data transfers with the biggest bandwidth.

Figure 7 – Portal and Mailbox conceptual views. Source: (SOUTO; PENNA; CASTRO, 2019)

Sync

The Sync abstraction (similar to POSIX Signals) is intended to establish synchronization points among the clusters and to construct distributed barriers. It can be used in one of the two distinct modes available: ONE\_TO\_ALL, in which N slaves wait to be unblocked by a single master node; and ALL\_TO\_ONE, where the single leader wait for notifications of the N slaves. This way, different types of barriers may be created, giving more flexibility to the programmer of the applications.

#### 4.2 NANVIX MULTIKERNEL

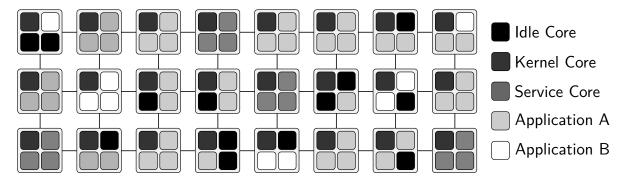

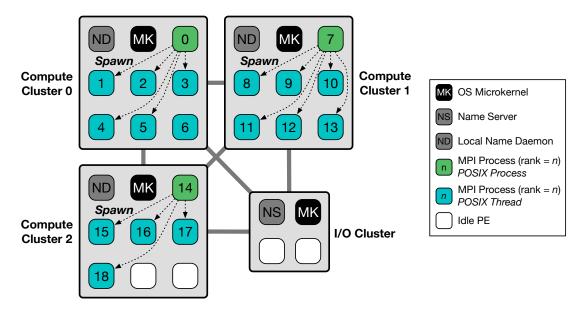

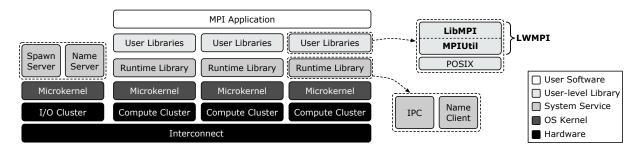

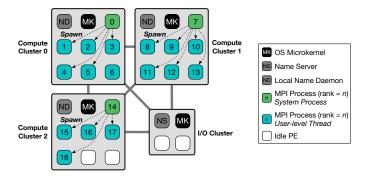

The multikernel OS design was introduced to address the intrinsic characteristics of lightweight manycores (WENTZLAFF; AGARWAL, 2009). The Nanvix Multikernel adopts this type of design, where it is implemented as a distributed system. In this model, each cluster of the distributed architecture executes an instance of the microkernel, and to communicate with one another, these instances use message passing mechanisms. Additionally, traditional OS services are also implemented in this distributed way. In the case of Nanvix, the OS services are modeled in a Client-Server fashion, where the servers are deployed in specific clusters (I/O Clusters), and attend to requisitions that arrive from the user processes, that are deployed in the general-purpose clusters of the architecture (Compute Clusters).

Figure 8 shows a snapshot of a distributed system running in a lightweight many-core in this programming model. The cores of a cluster may be either Idle (black squares), one core of each cluster will be running the kernel instance (dark grey squares), some cores will be executing OS services routines (grey squares), and the remaining may be executing user's space applications (white squares). To be POSIX-compliant, the Nanvix OS services implement standardized interfaces, keeping the client-server model transparent

Figure 8 – Overview of a distributed OS. Source: (PENNA et al., 2019)

to the user. The functionalities are provided in a transparent way, while the underlying implementation of these services perform the computing and communications needed.

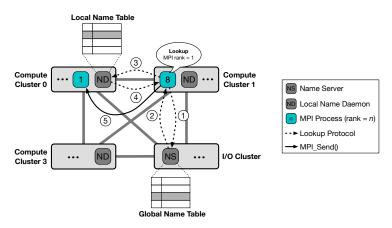

At this point, we can notice the versatility given by this model, in which any core of the processor may be used to any of the aforementioned purposes. Also, the set of available services may be adapted for each use-case scenario. At the startup, the user may define where and which kernel instances to deploy across the processor, defining only those services that will be needed, or even defining multiple instances of a single service to enable higher availability, for example. Some of the services currently supported by the Nanvix Multikernel are: (i) a Name Service that provides naming linking and resolution, similar to a DNS service, that translates processes logic names to their logic identifier in the distributed system; (ii) POSIX-compliant Named Semaphores; (iii) POSIX-compliant Shared Memory Regions abstraction; and (iv) a Virtual File System service.

### 4.3 ENHANCEMENTS IN NANVIX IKC

In this section, we discuss some of the improvements that have been made to the Nanvix IKC subsystem, in order to provide needed features to offer support for LWMPI and that were not yet available in Nanvix. In the next few sections, we discuss the proposed enhancements and explain why they were necessary to LWMPI development, emphasizing their development in the context of the present work.

### 4.3.1 Virtualization

In computing, the concept of virtualization corresponds to the act of creating a virtual version of a physical computational resource. This virtual resource may be used as a simplified form to generalize a complex component, or to permit a component to be efficiently shared and utilized (LI et al., 2013). In the context of the present work, it is precisely to permit that scarce hardware resources may be managed by the OS, removing this responsibility from the programmer.

Figure 9 – Virtualization conceptual view. Source: Developed by the author.

The Nanvix HAL exposes a standard interface of IPC abstractions that enable communication between distinct processes. The number of available abstractions that are exported by the HAL, however, is architecture-dependent, and is limited by the underlying hardware. In the case of lightweight manycores, where most of these hardware resources are scarce, the number of available abstractions is very limited. To cite an example, the Nanvix HAL permits the user in the Kalray MPPA-256 to create a single input portal and a single input mailbox, using the available NoC interfaces in a regular Compute Cluster. This means that there is a single resource abstraction that needs to be shared by the OS and by all user applications that run in a specific cluster.

Because of that, the implementation of mechanisms that enable the virtualization of the IPC abstractions exported by the HAL becomes an important requirement before providing a communication library on top of the Nanvix IKC facility. Not only to make the resource management easier and to permit more peers to keep an active connection simultaneously, but also to permit a finer extraction of statistics related to communication of the kernel. The existence of virtual abstractions, in this case, would permit the programmer and system developers to distinguish communication statistics that are related to kernel communications and those that are respective to the user. Additionally, to LWMPI, it permits the library implementation to establish multiple universes of communication, since different contexts are allowed to use distinct virtual abstractions to carry out the communications, giving much more flexibility for the programmer.

Figure 9 illustrates the virtualization scheme adopted in Nanvix that was implemented as part of the present work. In this implementation, the Nanvix kernel stores two control tables for each IPC abstraction: the first, the *Active IKC Table*, is directly mapped to the hardware resources exposed by the HAL and keeps track of the active connections configured in the underlying interfaces; the second, the *Virtual Abstractions Table*, keeps a mapping scheme of the virtual abstractions exposed by the kernel to their respective active connection. An N:1 communication pattern is adopted, in which a maximum number of virtual abstractions (N) is allowed to be mapped to the same physical abstraction, representing the logic ports controlled by the kernel.

Figure 10 – Conceptual view of IKC resource multiplexing. Source: Developed by the author.

# 4.3.2 Resource Multiplexing

The concept of multiplexing consists in combining multiple signals into a single one over a shared medium. In the present work, this concept is adapted and put altogether with the virtualization idea, in which multiple virtual abstractions are multiplexed over a single hardware resource. The importance of this feature is analogous to the virtualization one. In fact, these concepts are tightly linked in the context in which they are employed in this work. Virtualizing hardware resources is not sufficient to provide the intended functionality for the user. It is also necessary to provide means of resource sharing, in which multiple virtual abstractions are capable of using the hardware resources concurrently.

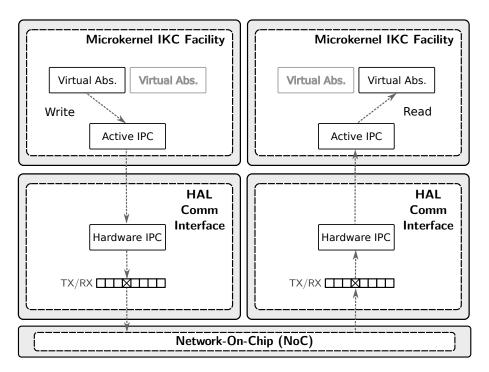

In Nanvix, we implemented a logic port-based scheme in which a limited number of virtual abstractions are mapped to abstractions that represent the hardware resources exposed by the HAL. After that, all of these mapped virtual abstractions may be capable of using the underlying resource, one at a time, while the others wait for it to become free. Figure 10 illustrates the expected data flow when one output abstraction (left) writes a simple message to be read by an input abstraction (right). When an abstraction receives a request from the user space to execute a communication call, it first looks to the lock of the active connection which it is mapped. If the underlying resource is already in use attending another request, it blocks waiting for an opportunity to handle its request. Otherwise, it acquires the lock and proceeds with the request to be processed by the HAL and transmitted through the NoC.

Originally, the communication calls in the Nanvix microkernel did not use any type of intermediary buffering. The input/output buffers used to carry on the communication operations simply came from the user space and were directly transmitted by the HAL routines. However, intermediary buffering schemes must be implemented to allow resource multiplexing, since the kernel needs to have means of storing messages that are read by a virtual abstraction and that are not addressed to it. More than specifying the remote node when writing a message, it is now necessary to address the target port which we want to communicate. This way, an additional Buffers Table was added to the kernel to permit this temporary storage of messages. When reading a message, a virtual abstraction may identify that the message that arrived through the interconnection is not addressed to it. This way, it reserves an entry in the Buffers Table and stores the arriving message there, while it keeps monitoring the hardware interface waiting for a message containing its logic address. Similarly, when a virtual abstraction wants to read an input message, it first traverses the Buffers Table to see if previous messages already arrived for it before trying to obtain access to the underlying hardware interfaces.

### 5 LWMPI: A MPI LIBRARY FOR LIGHTWEIGHT MANYCORES

In order to improve programmability and portability in lightweight manycores, we propose the Lightweight Message Passing Interface library (LWMPI). In contrast to alternative solutions (HO et al., 2015; RICHIE; ROSS; INFANTOLINO, 2017; DINECHIN et al., 2013b), more than developing an efficient solution in terms of performance and programmability, we intended to make LWMPI portable across different architectures, and achieved this thanks to a design and implementation that relies on top of a POSIX-compliant distributed OS for lightweight manycores. Before presenting the details and the internals of our solution, we first elucidate the reasons behind some of the design decisions that guided our library implementation and give the reasons why we believe that these decisions are important to achieve our main goal of providing a lightweight MPI-compliant library for lightweight manycores.

### 5.1 DESIGN GOALS

Lightweight manycores bring several challenges to software development, thereby making easy-to-use interfaces an important requirement for this class of processors. These challenges are not restricted to user-level programming, but also to basic software development. Thus, solutions must meet users demands while dealing with strict architectural constraints, especially memory issues. Hence, the main design goals of LWMPI are:

- 1. **Portability** The library should be portable and applicable to various lightweight manycores.

- 2. Compatibility The implementation must comply with the MPI specification.

- 3. **Extendability** It should be possible to add new functions or submodules to the implementation with little effort.

- 4. **Lightness** The implementation should be simple and lightweight to cope with restrictive resources of lightweight manycores.

To achieve these goals, we rely on important design decisions to cope with the aforementioned challenges:

- (i) design our library on top of an OS to enable portability across different architectures;

- (ii) adhere to the MPI standard to deliver *compatibility*;

- (iii) follow a tier-based approach to keep encapsulation and maintain the top-level library isolated from OS-dependent code, thereby enabling *extendability* without incurring excessive overheads that can arise from using more complex software patterns; and

- (iv) implement the library from scratch, rather than adapting an existing heavy-weight solution like OpenMPI (SPI, 2020) or MPICH (MPICH, 2020) to keep our solution light and suitable for lightweight manycores (HO et al., 2015).

The reason behind the choice of Nanvix to be the base OS for our library is that, to the best of our knowledge, it is the only open-source distributed OS that runs on commercially available baremetal lightweight manycores, like the Kalray MPPA-256 (DINECHIN et al., 2013a) and OpTiMSoC (WALLENTOWITZ et al., 2012). This way, it permits us to develop and test our solution directly on top of a real lightweight manycore, instead of an emulated machine or some other option based in virtualization, as it would have been if we had chosen another candidate OS like M³ or MOSSCA.

Currently, LWMPI implements an initial subset of the MPI specification and the reason behind this partial support is twofold: first, fully implementing the entire standard would demand much more time to be implemented and tested satisfactorily than the time available for the current work; and second, the complete implementation of the standard would also result in a much larger memory footprint, what violates our fourth design goal (lightness).

At this moment, an attentive reader may notice how difficult it is to find a balance between the four proposed design goals, especially considering the *lightness* goal, which may be the most difficult to achieve, while being one of the most important for lightweight manycores. It limits how much we can make the library extensible and how far we can go in the compliance with the full standard. Therefore, we give ourselves a concession in the second goal (*compatibility*) of understanding it in the sense of not diverting our implementation from what is specified by the standard, rather than completely supporting it. This way, we change our commitment from implementing the complete standard to implementing its essential parts, which are applicable for lightweight manycores, as they are specified.

## 5.2 OVERVIEW