# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA DE AUTOMAÇÃO E SISTEMAS

Gabriel Arthur Gerber Andrade

Test generation for shared-memory verification of multicore chips

Florianópolis 2021

Gabriel Arthur Gerber Andrade

# Test generation for shared-memory verification of multicore chips

Tese submetida ao Programa de Pós-Graduação em Engenharia de Automação e Sistemas para a obtenção do título de doutor em Engenharia de Automação e Sistemas. Orientador: Prof. Luiz Cláudio Villar dos Santos, Dr.

Florianópolis 2021 Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Andrade, Gabriel Arthur Gerber Test generation for shared-memory verification of multicore chips / Gabriel Arthur Gerber Andrade ; orientador, Luiz Cláudio Villar dos Santos , 2021. 112 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia de Automação e Sistemas, Florianópolis, 2021.

Inclui referências.

1. Engenharia de Automação e Sistemas. 2. Multicore. 3. Memória compartilhada coerente. 4. Verificação. 5. Geração de testes. I., Luiz Cláudio Villar dos Santos. II. Universidade Federal de Santa Catarina. Programa de Pós Graduação em Engenharia de Automação e Sistemas. III. Título.

# Gabriel Arthur Gerber Andrade Test generation for shared-memory verification of multicore chips

O presente trabalho em nível de doutorado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. Rodolfo Jardim Azevedo, Dr. Universidade Estadual de Campinas

Prof. Rômulo Silva de Oliveira, Dr. Universidade Federal de Santa Catarina

Prof. Márcio Bastos Castro, Dr. Universidade Federal de Santa Catarina

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de doutor em Engenharia de Automação e Sistemas.

Prof. Werner Kraus Junior, Dr Coordenador do Programa de Pós-Graduação

Prof. Luiz Cláudio Villar dos Santos, Dr. Orientador

Florianópolis, 2021.

Eu dedico este trabalho ao passado.

# ACKNOWLEDGEMENTS

I would like to thank all colleagues, professors, and fellow researchers that contributed, direct or indirectly, to the development of this work, in special my advisor, Luiz C. V. dos Santos, and coworkers, Marleson Graf and Nícolas Pfeifer, and seniors, Eberle Rambo and Leandro Freitas and Olav Henschel. Also, I would like to thank my family and friends for all support and encouragement provided over the years.

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Finance Code 001 and by the Conselho Nacional de Desenvolvimento Científico e Tecnológico - Brasil (CNPq) - Finance Code GD.

### **RESUMO**

Multiprocessadores consistem de processadores fortemente acoplados que compartilham um espaço de endereçamento de memória e são construídos com um ou múltiplos multicore chips. O susbsistema de memória compartilhada envolve componentes de hardware complexos que implementam um sofisticado protocolo de coerência cujo projeto em RTL é propenso a erros. Esta tese contribui para a verificação funcional do comportamento da memória compartilhada durante o projeto de multicore chips. Uma vez que o comportamento não determinístico é chave para expor erros de memória compartilhada, programas paralelos não sincronizados são frequentemente utilizados para a verificação do projeto e para o teste do protótipo. No entanto, durante a etapa de verificação, a lenta execução em um simulador requer o uso de técnicas não convencionais para expor erros e prover alta cobertura com programas mais curtos. Neste contexto, esta tese faz três contribuições. A primeira contribuição consiste em duas técnicas que impõem restrições à geração aleatória convencional de programas de teste para viabilizar a verificação eficiente da memória compartilhada. Uma delas explora cadeias canônicas de dependências para restringir a geração aleatória de sequências de instruções (de forma a aumentar a cobertura de transições entre estados que são induzidas por eventos de conflito em um mesmo endereço), outra explora restrições sobre o espaço de endereçamento para restringir o assinalamento aleatório de endereços distintos (de forma a aumentar a cobertura de transições entre estados devidas a eventos de evicção). Quando comparada a um gerador convencional, a combinação destas técnicas reduziu o esforço médio de verificação em uma ordem de magnitude em vários casos. A segunda contribuição é um novo mecanismo de geração dirigida por modelo de cobertura para melhorar a qualidade de testes não determinísticos. O mecanismo explora propriedades gerais de protocolos de coerência e de memórias cache para melhor controlar a cobertura de transições entre estados (a qual serve como proxy para aumentar a cobertura de acordo com a métrica que vier a ser adotada em um dado ambiente de verificação). Por ser independente de métrica de cobertura, de protocolo de coerência, e de parâmetros de cache, o mecanismo é reusável em projetos e ambientes de verificação bem diferentes. Este gerador baseado em modelo foi mais rápido para atingir valores de cobertura similares aos de um gerador dirigido por dados baseado em Programação Genética, reportado em trabalho correlato. Por exemplo, ao executar testes com 1K operações para verificar projetos de 32 núcleos, este nosso gerador alcançou 60% da cobertura dez vezes mais rápido. A terceira contribuição é uma abordagem híbrida, a qual não é uma simples combinação de uma técnica dirigida por dados com outra dirigida por modelo. A abordagem reformula a geração dirigida de testes como um problema de otimização com dois objetivos e explora vizinhanças para evitar a enumeração explícita do espaço de estados do protocolo de coerência, sem excluir soluções ótimas do espaço de pesquisa. Comparada com um gerador puramente dirigido por dados e com outro baseado em modelo, a abordagem híbrida levou a uma melhor evolução da cobertura ao longo do tempo, quando avaliada para 32 núcleos e para diferentes protocolos de coerência. Por exemplo, para um protocolo MOESI de dois níveis, a abordagem foi 2,7 vezes mais rápida do que o gerador baseado em modelo e cerca de 5 a 19 vezes mais rápido do que o gerador dirigido por dados. Finalmente, a abordagem híbrida também foi comparada com um gerador dirigido por dados baseado em Aprendizado por Reforço. Os resultados experimentais mostraram que a abordagem híbrida proposta é de 2 a 3 vezes mais rápida para obter a máxima cobertura atingida por aquele gerador.

Palavras-chave: Multicores. Memória compartilhada coerente. Verificação. Geração de testes.

### **RESUMO EXPANDIDO**

### Introdução

Multiprocessadores são computadores cujos processadores foram acoplados de forma a compartilhar um mesmo espaço de endereçamento de memória sob o controle de um único sistema operacional. Dado que multiprocessadores são construídos com um ou múltiplos multicore chips, esta tese investiga a verificação de projeto do seu componente básico: o multicore chip. A comunicação via memória compartilhada costuma aderir a um protocolo de coerência de cache, frequentemente implementado em hardware. Há indicadores de que a coerência tende a continuar importante para multicore chips voltados a aplicações de propósitos gerais. Embora o número de estados do protocolo de coerência cresça exponencialmente com o número de núcleos, há indícios de que (através de decisões de projeto adequadas) é possível preservar a escalabilidade do hardware de suporte à coerência. Portanto, a viabilidade prática da coerência em hardware - ao menos no escopo de um multicore chip - acaba resultando em um desafio à verificação de seu projeto, mesmo sob a limitação que a potência térmica impõe ao crescimento do número de núcleos. Além disso, uma vez que a maioria dos programas paralelos são elaborados com base em bibliotecas de sincronização, muitos fabricantes passaram a propor processadores que relaxam a consistência sequencial da memória compartilhada (permitindo o relaxamento da ordem entre leituras e escritas para endereços distintos), sem que o programador precise se preocupar com isso. Ora, esta tendência aumenta o número de comportamentos válidos de um programa paralelo e, consequentemente, contribui para aumentar, ainda mais, a complexidade da verificação do projeto. Nesse contexto, esta tese contribui para a verificação funcional do comportamento de operações em memória compartilhada ao se validar um multicore chip em tempo de projeto. A verificação funcional baseia-se na simulação da execução de programas não-sincronizados (uma vez que o comportamento não determinístico é chave para expor erros em memória compartilhada). Ela requer um gerador de programas de teste e um checker capaz de diagnosticar comportamentos anômalos em tempo de execução, a fim de sinalizar, o mais cedo possível, um erro de projeto.

### Objetivos

Os objetivos usuais para a verificação funcional são: (1) aumentar a probabilidade de descoberta de erros de projeto, (2) aumentar a cobertura, e (3) reduzir o esforço necessário para encontrar erros ou para alcançar uma cobertura apropriada. O escopo desta tese é a geração de programas paralelos não sincronizados. Ela aborda a geração de testes (aleatórios e dirigidos) de maneira a atingir esses três objetivos usuais, além de um quarto objetivo: a reusabilidade de um gerador em diferentes projetos, diferentes variantes de protocolos de coerência, e diferentes ambientes de verificação.

### Contribuições

Esta tese relata três contribuições científicas. A primeira contribuição consiste em duas novas técnicas que impõem restrições à geração aleatória convencional de programas de teste para viabilizar a verificação eficiente da memória compartilhada. Uma delas, denominada *chaining*, explora cadeias canônicas de dependências para restringir a geração aleatória de sequências de instruções (de forma a aumentar a cobertura de transições entre estados que são induzidas por eventos de conflito em um mesmo endereço); outra, denominada *biasing*, explora restrições sobre o espaço de endereçamento para restringir o assinalamento aleatório de endereços distintos (de forma a aumentar a cobertura de transições entre estados devidas a eventos de

evicção). A segunda contribuição é um novo mecanismo de geração dirigida por modelo de cobertura para melhorar a qualidade de testes não determinísticos. O mecanismo, denominado CTG (*coverage-driven test generation*), explora propriedades gerais de protocolos de coerência e de memórias *cache* para melhor controlar a cobertura de transições entre estados (a qual serve como *proxy* para aumentar a cobertura de acordo com a métrica que vier a ser adotada em um dado ambiente de verificação). A terceira contribuição é uma abordagem híbrida para a geração dirigida de testes, a qual não é uma simples combinação de uma técnica dirigida por dados com outra dirigida por modelo. A abordagem, denominada HTG (*hybrid test generation*) reformula a geração dirigida de testes como um problema de otimização com dois objetivos e explora vizinhanças para evitar a enumeração explícita do espaço de estados do protocolo de coerência, sem excluir soluções ótimas do espaço de pesquisa. Por serem independentes de métrica de cobertura, de protocolo de coerência, e de parâmetros de *cache*, as contribuições desta tese são reusáveis em diferentes projetos e em ambientes de verificação bem distintos.

# Metodologia

Para validação e avaliação experimental das contribuições propostas, foram adotados os seguintes passos metodológicos: (1) uso de geradores pré-existentes (que capturam o estado-da-arte) para servir de base de comparação; (2) construção de um novo gerador para cada uma das contribuições propostas nesta tese; (3) síntese de erros artificiais de projeto para desafiar os geradores; (4) simulação da execução dos programas sintetizados por cada um dos geradores disponíveis (os novos e os pré-existentes) para diferentes representações de projetos (com e sem erros); e (5) comparação dos geradores em termos de eficácia (descoberta de erros), cobertura (fração dos estados e transições visitados), e esforço (tempo para detectar erros ou para atingir uma dada cobertura). Para servir como representações de projeto, adotaram-se modelos de processador, memória e interconexão (O3, Ruby e simple, respectivamente) disponíveis no ambiente de simulação gem5. A escolha desse ambiente se deu por razões pragmáticas, em especial pela disponibilidade em domínio público de uma variedade de complexos protocolos de coerência, mas também por viabilizar o uso de checkers localmente disponíves, cujo reuso foi crucial para a viabilidade deste trabalho em tempo. A execução foi simulada para representações de projeto com 8, 16 e 32 cores (todos com suporte a escalonamento dinâmico) e para protocolos populares, tais como MESI de três níveis e MOESI de dois níveis. A eficácia dos geradores foi avaliada com a injeção de diferentes arquétipos de erros de projeto, sob diferentes métricas de cobertura e para uma ampla configuração de parâmetros de geração (e.g. número de operações e de variáveis compartilhadas).

## Resultados e Discussão

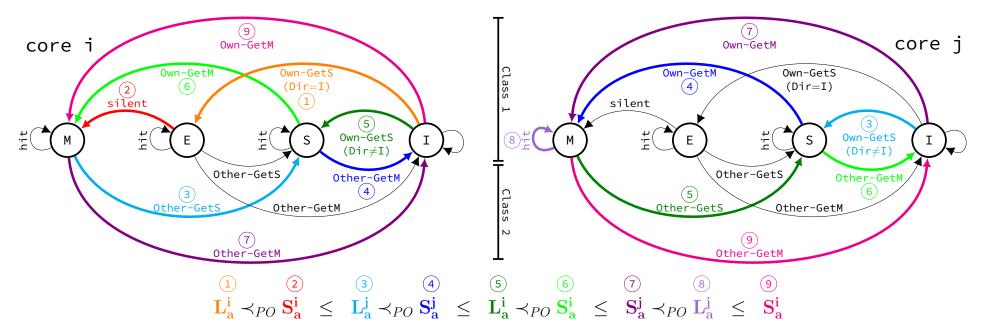

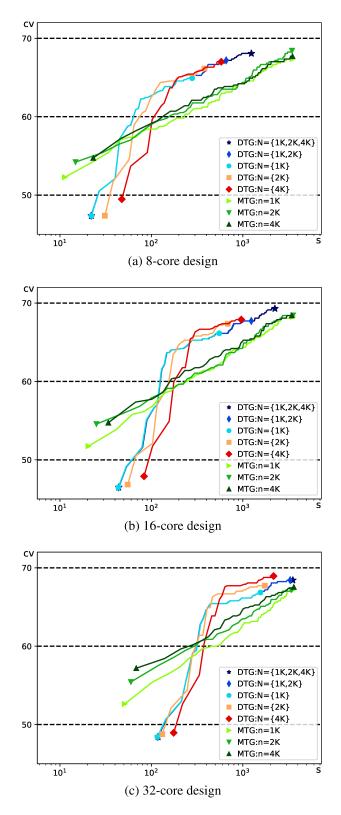

Ao avaliar a primeira contribuição desta tese em comparação com um gerador aleatório de testes convencional, observou-se que a aplicação das técnicas *chaining* e *biasing* tende a ampliar a capacidade de descoberta de erros de projeto, a aumentar a cobertura e a reduzir significativamente o esforço médio de verificação. Por exemplo, para projetos com 32 *cores*, pelo menos 50% do espaço de geração tornou-se capaz de expor erros, a mediana da cobertura aumentou em 44% e 83% nos dois níveis mais altos de hierarquia de memória, e o esforço médio de verificação foi reduzido em uma ordem de magnitude em vários casos. Ademais, os resultados experimentais observados – no âmbito de geração *aleatória* de testes – indicaram que uma simplificação da técnica genérica de *biasing* originalmente proposta poderia viabilizar a exploração *dinâmica* de restrições à formação de endereços, beneficiando assim a geração *dirigida* de testes, o que acabou motivando a segunda contribuição desta tese. Ao avaliar a segunda contribuição desta tese em comparação com o *McVersi Test Generator* (MTG) – que é um gerador dirigido por dados,

baseado em Programação Genética - observou-se que a técnica proposta de geração dirigida por modelo de cobertura (CTG) tende a atingir, em menor tempo, níveis de cobertura similares aos obtidos pelo MTG. Por exemplo, para projetos com 32 cores, ao executar testes com 1K operações, o CTG obteve a mesma cobertura máxima atingida pelo MTG, mas alcançou a cobertura de 60% em tempo dez vezes menor. Além disso, erros que o MTG levou cerca de uma hora para detectar foram expostos pelo CTG entre 5 a 30 minutos. Ao avaliar a terceira contribuição desta tese em comparação com o gerador MTG (puramente dirigido por dados) e o gerador CTG (puramente dirigido por modelo), observou-se que a abordagem proposta de geração híbrida (HTG) leva a uma melhor evolução da cobertura ao longo do tempo, mesmo quando aferida para diferentes protocolos de coerência. Por exemplo, para projetos com 32 cores e um protocolo MOESI de dois níveis, a abordagem HTG foi cerca de 8 a 19 vezes mais rápida para obter a máxima cobertura atingida pelo MTG e 2,7 vezes mais rápida para obter a máxima cobertura obtida pelo CTG. Para um protocolo MESI de 3 níveis, o HTG encontrou em 10 a 15 minutos, alguns erros que o MTG levou de 45 minutos a 7 horas para detectar. Finalmente, avaliou-se a terceira contribuição desta tese também em comparação com com um outro gerador puramente dirigido por dados, baseado em Aprendizado por Reforço, denominado RLG (Reinforcement Learning Test Generator). Embora o RLG tenha sido instrumentado para utilizar o mesmo módulo de RTG usado pelo HTG (de forma que ambos se beneficiem das técnicas de chaining e biasing nele aplicadas), observou-se que a abordagem de geração híbrida (HTG) é superior ao RLG em termos de evolução da cobertura para diferentes protocolos de coerência e métricas distintas de cobertura. Por exemplo, para projetos com 32 cores e um protocolo MESI de 3 níveis, o HTG atingiu a cobertura de 95,8% em 3 horas, enquanto o RLG levou 6 horas. Para um protocolo MOESI de 2 níveis, o HTG atingiu a cobertura de 95,26% em 2 horas, enquanto o RLG levou 6 horas.

# **Considerações Finais**

A evidência experimental indica que as técnicas propostas nesta tese reduziram o esforço de verificação, melhoraram a descoberta de erros, e aumentaram a cobertura. Por exemplo, as técnicas chaining e biasing melhoraram a qualidade dos testes não determinísticos sintetizados através de geração aleatória de testes (Capítulo 3), geração dirigida puramente baseada em modelo (Capítulo 4), geração puramente dirigida por dados (Capítulo 6) e geração dirigida híbrida (Capítulos 5). Os resultados experimentais também indicam que, quando técnicas de aprendizado são usadas para a geração dirigida de testes (como a Programação Genética no MTG e o Aprendizado por Reforço no RLG), é improvável que elas exibam evolução de cobertura superior se: (1) não explorarem dinamicamente restrições que capture propriedades gerais de memória compartilhada (como ocorre com o MTG) e (2) não se basearem em algum modelo para guiar a evolução de cobertura enquanto ainda estiverem aprendendo (como acontece com o RLG e o MTG). Como se espera que a próxima geração de ferramentas de EDA utilize Aprendizado de Máquina para atingir alta cobertura em menor tempo, as descobertas relatadas nesta tese parecem indicar que, em futuras técnicas de geração, a inovação possa efetivamente vir de técnicas avançadas de aprendizado, desde que não se desprezar a herança recebida da longa tradição em geração aleatória de testes nem de modelos de cobertura eficientes.

Palavras-chave: Multicores. Memória compartilhada coerente. Verificação. Geração de testes.

## ABSTRACT

Multiprocessors consist of tightly coupled processors that share some memory address space and are built with a single or multiple multicore chips. The shared-memory subsystem involves complex hardware components implementing a sophisticated coherence protocol whose RTL design is prone to errors. This thesis contributes to the functional verification of sharedmemory behavior during the design of multicore chips. Since non-deterministic behavior is key to exposing shared-memory errors, non-synchronized parallel programs are often used for design verification and prototype test. However, in the verification phase, the slow execution in a simulator requires non-conventional techniques for enabling error exposure and high coverage with shorter programs. In this context, this thesis makes three contributions. The first contribution consists of two techniques that build upon conventional random test generation for efficient shared-memory verification. One technique exploits canonical dependence chains for constraining the random generation of instruction sequences (to raise the coverage of state transitions due to memory events conflicting at a same shared location), another exploits address space constraints for biasing random address assignment (to raise the coverage of state transitions due to eviction events). As compared to a conventional generator, their combination reduced the average verification effort by one order of magnitude in many cases. The second contribution is a new mechanism for directed generation that improves the quality of non-deterministic racy tests. The mechanism exploits general properties of coherence protocols and cache memories for better control on transition coverage (which serves as a proxy for increasing the actual coverage metric adopted in a given verification environment). Being independent of coverage metric, coherence protocol, and cache parameters, the mechanism is reusable across quite different designs and verification environments. Such a model-based generator was faster to reach similar coverage as obtained by a data-driven generator (based on Genetic Programming), reported in a related work. For instance, when executing tests with 1K operations for verifying 32-core designs, our test generator reached 60% coverage ten times faster. The third contribution consists of an hybrid approach that is not a simple combination of data-driven and model-based techniques. It reformulates directed test generation as a doubleobjective optimization problem, and it explores neighborhoods to avoid explicit enumeration of the coherence state space without excluding optimal solutions from the search space. As compared to purely data-driven and model-based generators, the hybrid approach led to superior coverage evolution with time, when targeting 32-core designs relying on different protocols. For instance, for a MOESI 2-level protocol, the approach was up to 2.7 faster than the modelbased generator and around 5 to 19 times faster than the data-driven generator. Finally, the hybrid approach was also compared to a data-driven generator based on Reinforcement Learning. The experimental results showed that the proposed hybrid approach was 2 to 3 times faster to obtain the maximal coverage reached by that generator.

Keywords: Multicores. Coherent shared memory. Verification. Test generation.

# LIST OF FIGURES

| Figure 1 –  | An overview of the proposed framework                          | 33  |

|-------------|----------------------------------------------------------------|-----|

| Figure 2 –  | Structure of the proposed generator                            | 43  |

| Figure 3 –  | Examples of chain categories 0, 1, 2 and 3                     | 44  |

| Figure 4 –  | How a canonical chain improves the coverage                    | 46  |

| Figure 5 –  | Example of address assignment                                  | 47  |

| Figure 6 –  | Meaning of competition pattern                                 | 48  |

| Figure 7 –  | Impact on functional coverage for random test generation       | 60  |

| Figure 8 –  | How colliding operations avoid revisiting transitions          | 70  |

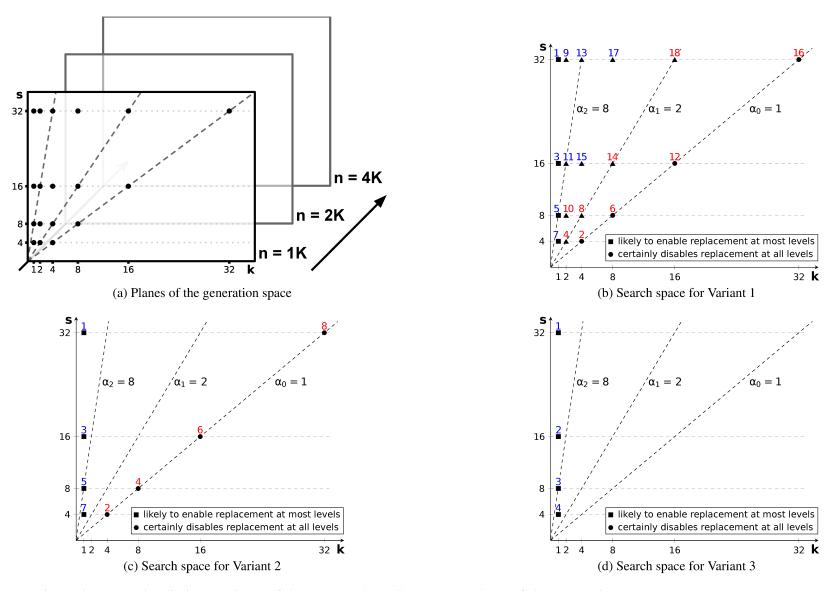

| Figure 9 –  | How proposed variants traverse a plane of the generation space | 73  |

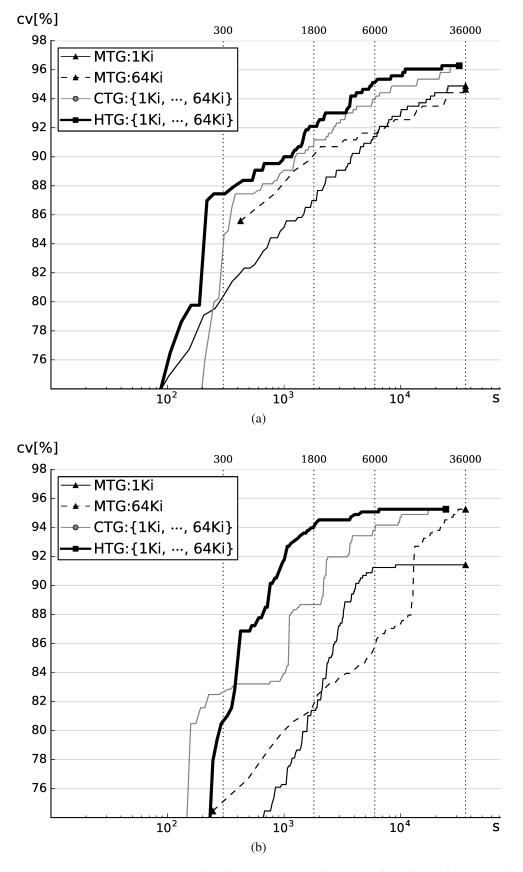

| Figure 10 – | Coverage evolution for directed test generation                | 79  |

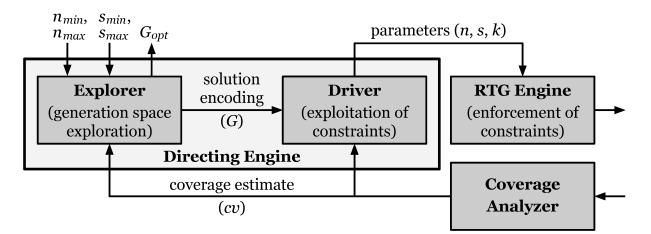

| Figure 11 – | The anatomy of the proposed Directing Engine                   | 83  |

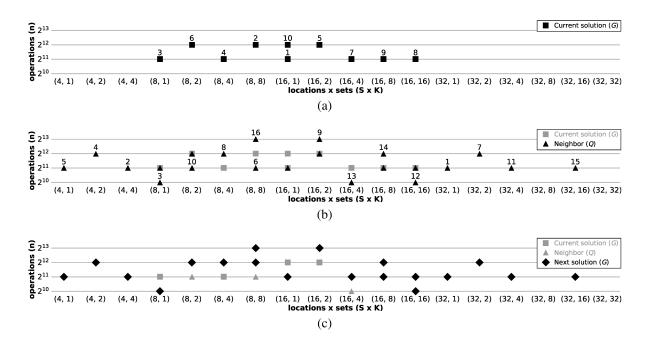

| Figure 12 – | Explorer and Driver at work                                    | 86  |

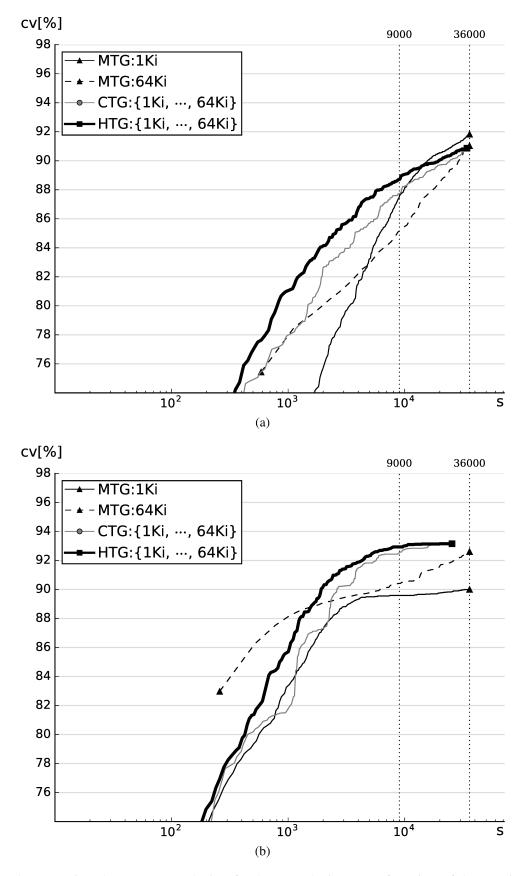

| Figure 13 – | Structural coverage evolution for the hybrid generator         | 94  |

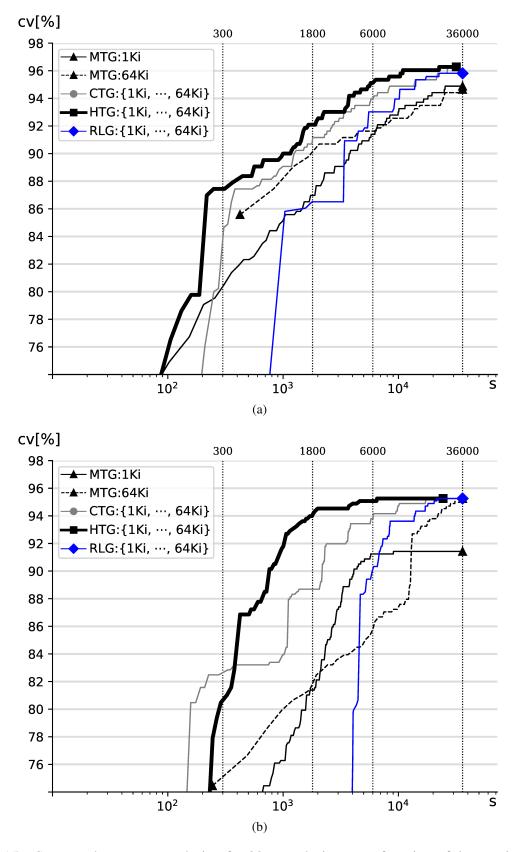

| Figure 14 – | Functional coverage evolution for the hybrid generator         | 96  |

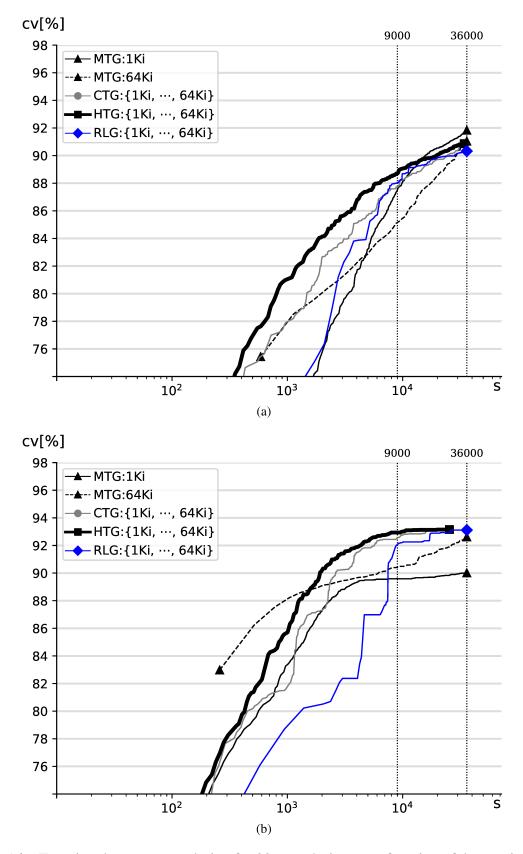

| Figure 15 – | Structural coverage evolution against Reinforced Learning      | 102 |

| Figure 16 – | Functional coverage evolution against Reinforced Learning      | 103 |

# LIST OF TABLES

| Table 1 – Relation between distinct terminologies for cache levels              | 36  |

|---------------------------------------------------------------------------------|-----|

| Table 2 – Target mixes                                                          | 50  |

| Table 3 – Types of artificial design errors                                     | 52  |

| Table 4 – Median improvement in coverage for random test generation             | 55  |

| Table 5 – Fractions of generation space with potential for error exposure       | 56  |

| Table 6 – Average improvement in effectiveness and in effort                    | 59  |

| Table 7 – Impact for SWMR violations                                            | 62  |

| Table 8 – Impact for DV violations                                              | 62  |

| Table 9 – How related works address test generation                             | 66  |

| Table 10 – Events inducing distinct classes of transitions                      | 68  |

| Table 11 – Studied design errors                                                | 77  |

| Table 12 – Effort required for finding errors (I)                               | 81  |

| Table 13 – Effort required for finding errors (II)                              | 81  |

| Table 14 – DTG approaches for functional verification of multicore chips        | 84  |

| Table 15 – Studied errors for MESI 3-level designs                              | 92  |

| Table 16 – Studied errors for MOESI 2-level designs                             | 93  |

| Table 17 – Time for finding errors in MESI 3-level for the hybrid generator     | 97  |

| Table 18 – Time for finding errors in MOESI 2-level for the hybrid generator    | 98  |

| Table 19 – Time for finding errors in MESI 3-level against Reinforced Learning  | 105 |

| Table 20 – Time for finding errors in MOESI 2-level against Reinforced Learning | 105 |

# LIST OF ALGORITHMS

| Algorithm 1 – The algorithm underlying the directing engine         |                      | 75 |

|---------------------------------------------------------------------|----------------------|----|

| Algorithm 2 – The algorithm underlying the generalized directing en | ngine                | 87 |

| Algorithm 3 – The algorithm underlying the Explorer                 |                      | 88 |

| Algorithm 4 – The algorithm underlying the auxiliary routine Reduc  | ce Neighbor          | 88 |

| Algorithm 5 – The algorithm underlying the auxiliary routine Gener  | rate Neighbor        | 88 |

| Algorithm 6 – The algorithm underlying the auxiliary routine Select | t Neighboring Points | 89 |

| Algorithm 7 – The algorithm underlying the Driver                   |                      | 90 |

## LIST OF ABBREVIATIONS AND ACRONYMS

- CP Competition Pattern.

- **CPU** Central Processing Unit.

- CTG Coverage-driven Test Generator.

DFSM Dichotomic Finite State Machine.

DTG Directed Test Generator.

**DV** Data Value.

EDA Electronic Design Automation.

FSM Finite State Machine.

HTG Hybrid Test Generator.

MCM Memory Consistency Model.

MESI Modified Exclusive Shared Invalid.

MOESI Modified Owned Exclusive Shared Invalid.

MOSI Modified Owned Shared Invalid.

MTG McVerSi Test Generator.

RLG Reinforcement Learning Test Generator.

- RTG Random Test Generation.

- **RTL** Register Transfer Level.

- SWMR Single-Writer-Multiple-Reader.

# CONTENTS

| 1       | INTRODUCTION                                       | 31 |

|---------|----------------------------------------------------|----|

| 1.1     | TRENDS IN MULTICORE CHIP DESIGN                    | 31 |

| 1.2     | CHALLENGES OF SHARED-MEMORY VALIDATION             | 32 |

| 1.3     | SHARED-MEMORY FUNCTIONAL VERIFICATION GOALS        | 33 |

| 1.3.1   | Main approaches                                    | 33 |

| 1.3.2   | Main engines and steps                             | 33 |

| 1.3.3   | Challenging problems tackled by this thesis        | 34 |

| 1.4     | CONTRIBUTIONS                                      | 34 |

| 1.5     | METHODOLOGY                                        | 36 |

| 1.6     | ORGANIZATION OF THIS THESIS                        | 37 |

| 1.7     | ACKNOWLEDGEMENTS                                   | 37 |

| 2       | FUNDAMENTAL CONCEPTS                               | 39 |

| 2.1     | SHARED-MEMORY BEHAVIOR                             | 39 |

| 2.2     | COLLISIONS AND CONFLICTS                           | 39 |

| 2.3     | CANONICAL DEPENDENCE CHAINS                        | 40 |

| 3       | RANDOM TEST GENERATION                             | 41 |

| 3.1     | RELATED WORK                                       | 41 |

| 3.2     | THE PROPOSED GENERATION FLOW                       | 43 |

| 3.3     | A CONCEPTUAL RE-ELABORATION                        | 43 |

| 3.3.1   | Exploitation of chains for thread generation       | 44 |

| 3.3.2   | Exploitation of constraints for address assignment | 47 |

| 3.4     | EXPERIMENTAL EVALUATION                            | 49 |

| 3.4.1   | Experimental setup                                 | 49 |

| 3.4.2   | Metrics                                            | 51 |

| 3.4.2.1 | Metric 1: Potential for error exposure             | 51 |

| 3.4.2.2 | Metric 2: Effectiveness in error exposure          | 53 |

| 3.4.2.3 | Metric 3: Verification effort                      | 53 |

| 3.4.2.4 | Metric 4: Functional coverage                      | 54 |

| 3.4.3   | Broad assessment of impact                         | 55 |

| 3.4.3.1 | Impact on coverage over the generation space       | 55 |

| 3.4.3.2 | Impact of parameter choice on error exposure       | 55 |

| 3.4.3.3 | Impact on effectiveness over joint exposure spaces | 58 |

| 3.4.3.4 | Impact on effort over the entire generation space  | 58 |

| 3.4.4   | Assessment for a fixed core count                  | 58 |

| 3.4.4.1 | Impact on functional coverage                      | 58 |

| 3.4.4.2 | Impact on error exposure and effort                | 61 |

| 3.5     | CONCLUSIONS                                        | 53        |

|---------|----------------------------------------------------|-----------|

| 4       | DIRECTED TEST GENERATION                           | 65        |

| 4.1     | RELATED WORK                                       | 55        |

| 4.2     | MAIN IDEAS BEHIND THE CONTRIBUTION                 | 57        |

| 4.2.1   | Proposed classification of transitions             | 67        |

| 4.2.2   | Proposed constraints on RTG                        | <b>68</b> |

| 4.2.2.1 | Constraint 1: alternation between Classes 1 and 2  | 59        |

| 4.2.2.2 | Constraint 2: uniform competition                  | 59        |

| 4.2.3   | Proposed coverage model                            | 71        |

| 4.3     | DESCRIPTION OF THE DIRECTING ENGINE                | 72        |

| 4.3.1   | An example of how it works                         | 72        |

| 4.3.2   | The proposed algorithm                             | 74        |

| 4.4     | EXPERIMENTAL EVALUATION                            | 76        |

| 4.4.1   | Experimental setup                                 | 76        |

| 4.4.2   | Experimental results                               | 76        |

| 4.5     | CONCLUSIONS                                        | 82        |

| 5       | HYBRID DIRECTED TEST GENERATION       8            | 83        |

| 5.1     | RELATED WORK                                       | 34        |

| 5.2     | DTG FORMULATION AS AN OPTIMIZATION PROBLEM         | 85        |

| 5.3     | THE DIRECTING ENGINE AT WORK: AN EXAMPLE           | 86        |

| 5.4     | THE DIRECTING ENGINE: ALGORITHMS                   | 87        |

| 5.4.1   | The Data-Driven Explorer                           | 87        |

| 5.4.2   | The Model-Based Driver                             | 89        |

| 5.5     | EXPERIMENTAL EVALUATION                            | 91        |

| 5.5.1   | Experimental setup                                 | 91        |

| 5.5.2   | Structural coverage evolution                      | 93        |

| 5.5.3   | Functional coverage evolution                      | 95        |

| 5.5.4   | Error discovery rate and detection time            | 97        |

| 5.6     | CONCLUSIONS                                        | 98        |

| 6       | A COMPARISON OF APPROACHES TO DIRECTED TEST GENER- |           |

|         | ATION                                              | 99        |

| 6.1     | A BRIEFING ON THE KEY IDEAS BEHIND THE RLG         | 99        |

| 6.2     | EXPERIMENTAL EVALUATION                            | )0        |

| 6.2.1   | Structural coverage evolution                      | )0        |

| 6.2.2   | Functional coverage evolution                      | )1        |

| 6.2.3   | Error discovery rate and detection time            | )4        |

| 6.3     | CONCLUSIONS                                        | )6        |

| 7 | CONCLUSIONS AND PERSPECTIVES | <br>107 |

|---|------------------------------|---------|

|   | BIBLIOGRAPHY                 | <br>109 |

## **1 INTRODUCTION**

Multiprocessors are "computers consisting of tightly coupled processors whose coordination and usage are typically controlled by a single operating system and that share memory through a shared address space" (HENNESSY; PATTERSON, 2019). They are built with a single or multiple multicore chips. This thesis targets the *design verification* of the basic component of multiprocessors: the multicore chip.

This chapter first introduces the main architectural trends that affect multicore chip design and the resulting verification challenges. Then it clarifies the target problems that define the scope of this thesis. Finally, it summarizes the main contributions and the methodology used for their evaluation.

#### 1.1 TRENDS IN MULTICORE CHIP DESIGN

Shared-memory behavior is defined by two complementary aspects: *coherence* defines *which* values can be returned by a load, and consistency defines *when* a written value will be returned by a load (PATTERSON; HENNESSY, 2020). The first aspect is related to the serialization of store operations to a *same* location. The second one is defined by the ordering between load and store operations to distinct locations, and to which extent stores are seen as atomic operations (ADVE; GHARACHORLOO, 1996).

Among the trends in multicore chip design, three aspects are important for defining the relevance and the scope of this thesis:

- Multicore scaling limited by power. It has long been shown that "multicore scaling is

power limited to a degree not widely appreciated by the computing community" (ESMAEILZADEH et al., 2011; ESMAEILZADEH et al., 2012), as a result of the underutilization of integration capacity (aka dark silicon). However, even under such limited

multicore scaling, the projected growth still leads to a major challenge in coherent sharedmemory verification, because the protocol state space grows exponentially with the number of cores. Therefore, pragmatic techniques should not enumerate that space.

- **On-chip cache coherence.** Coherent shared-memory is expected in many multicore chips, especially those targeting general-purpose systems (DEVADAS, 2013). Although there is no consensus on the practical limit for coherent cores per chip, the techniques devised for graceful scaling up to tens of cores (MARTIN; HILL; SORIN, 2012) seem to be confirmed by recent examples like IBM Power 9, Xeon E7, and Fujitsu SPARC64X (HENNESSY; PATTERSON, 2019). Since many multicore chips are likely to be coherent, the exploitation of coherence properties to improve test generation seems pragmatic.

- Relaxed and sequential consistency modes. Most manufacturers have been building hardware that relax sequential consistency (IBM, 2019; ARM, 2018; WATERMAN;

ASANOVI, 2019). Sequential consistency (ADVE; GHARACHORLOO, 1996) is also often supported by some atomic instructions as an alternative mode. The main challenge in terms of consistency verification is how to efficiently check designs where the *non-multiple copy atomic* behavior of store instructions is architecturally visible (TRIPPEL et al., 2017), such as in Power and ARMv7, or is exposed in aggressive high-performance implementations, such as in the revised ARMv8 and RISC-V. Therefore, albeit the role of consistency is crucial for developing *checkers*, it is less important for building test *generators*. Indeed, to be reusable, a generator should be largely independent of the consistency model adopted by a given design. Although the exploitation of a specific consistency model for generation would limit reusability, any pragmatic generation technique should be able to handle the consistency requirements of sophisticated architectures, instead of being hampered by them. This trend increases the number of valid behaviors of a parallel program and, therefore, increases the complexity of design verification even further.

# 1.2 CHALLENGES OF SHARED-MEMORY VALIDATION

The practical feasibility of coherence in hardware – at least in the scope of a multicore chip for general-purpose systems – ends up challenging shared-memory validation due to the large protocol state space, even under the limitation imposed by power on core count. The relaxation of sequential consistency further increases the challenges.

The validation of the shared-memory system is challenged at different abstraction levels and distinct phases of the design cycle. The validation effort combines formal verification, e.g. Zhang et al. (2015), and simulation of the coherence protocol at the architectural level, relies on simulation-based functional verification of the design representation at the microarchitectural level (ADIR et al., 2004; FINE; ZIV, 2003; WAGNER; BERTACCO, 2008; QIN; MISHRA, 2012; ELVER; NAGARAJAN, 2016), and finishes with the test of the multicore chip prototype. Shared-memory *test* relies on Random Test Generation (RTG) and post-mortem checking, e.g. Manovit & Hangal (2006). It can exploit long tests with hundreds of thousands of operations to reach high coverage, because the speed of the hardware prototype allows for suitable test throughput. Shared-memory *verification* usually relies on constrained random test generation and runtime checking to stop simulation as soon as a design error is found (ADIR et al., 2004; SHACHAM et al., 2008; FREITAS; RAMBO; SANTOS, 2013; GRAF et al., 2019). It should exploit short tests with tens of thousands of operations (ADIR et al., 2004), because the speed of the simulator would limit test throughput if much larger tests were used.<sup>1</sup>

The scope of this thesis is the *functional verification* of the coherent shared-memory behavior observed in a representation of a multicore chip at design time.

<sup>&</sup>lt;sup>1</sup> In contrast, post-silicon testing usually relies on tests with tens of millions of operations (MANOVIT; HAN-GAL, 2006), which are directly executed on the hardware prototype.

### 1.3 SHARED-MEMORY FUNCTIONAL VERIFICATION GOALS

The focus of this thesis is on *test generation* for functional verification. The usual goals of functional design verification are to increase the probability of *bug discovery*, to raise *coverage*, and to reduce the *effort* required for finding errors or reaching proper coverage. This thesis addresses test generation towards meeting such usual goals, under the focus of an extra desirable feature: the *reusability* across distinct designs, different protocol variants, and distinct design environments.

### **1.3.1** Main approaches

To reach proper coverage with short tests, simulation-based functional verification relies on *directed* test generation, which appears under different approaches:

- 1. *Coverage-directed Random Test Generation (RTG)* targets the full system, and it is driven by metrics defined in test plans (FINE; ZIV, 2003; ADIR et al., 2004).

- 2. *Coherence-based test generation* targets the memory subsystem, and it is driven by the coverage of the full protocol space (QIN; MISHRA, 2012) or a decomposition of it (WAGNER; BERTACCO, 2008).

- 3. *Consistency-based test generation* targets memory consistency verification over the full system, and it can be driven by coverage metrics defined in test plans (ELVER; NA-GARAJAN, 2016).

### **1.3.2** Main engines and steps

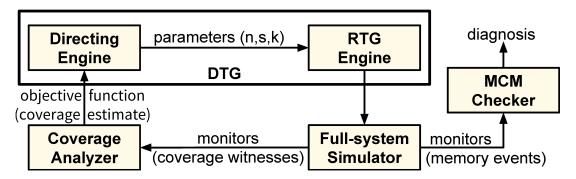

This thesis proposes novel techniques within a framework that relies on coveragedirected test generation for the functional verification of coherent shared memory. Figure 1 depicts the proposed framework. It includes a simulator for a full-system design representation of a multicore chip. The RTG engine relies on three parameters to constrain the building of a test program: the number of memory operations (n), the number of shared memory locations

Figure 1 – An overview of the proposed framework.

(s), and the number of distinct cache sets to which the locations can be mapped (k). While the simulator executes a test program, monitors observe memory events at relevant points of each core domain. A checker analyzes the monitored events at runtime according to the axioms of the target Memory Consistency Model (MCM) (GHARACHORLOO, 1995), and it issues a positive diagnosis as soon as it detects an inconsistency. Besides, other monitors observe events that serve as coverage witnesses from which an analyzer computes the cumulative coverage of all tests executed so far. The directing engine takes that coverage value into account before selecting the next setting of parameters for RTG.

## **1.3.3** Challenging problems tackled by this thesis

To help building the envisaged verification framework, this thesis addresses three challenging problems:

- 1. Given a program size and a number of shared locations as parameters, how to improve the quality of non-deterministic tests by means of constrained random test generation so as to reduce the effort, raise bug discovery, and increase coverage?

- 2. Given a *range* of program sizes and a *range* for the number of shared locations, how to dynamically select proper generation parameters for increasing coverage in less time?

- 3. Given a *space* of generation parameters, how to find a *subspace* that maximizes coverage in minimum?

# 1.4 CONTRIBUTIONS

This thesis describes three contributions to test generation for shared-memory verification, each solving one of the mentioned challenging problems.

1. The enforcement of non-conventional constraints for improving error discovery and coverage during random test generation. It consists of a conceptual re-elaboration on two techniques proposed in previous works (ANDRADE; GRAF; SANTOS, 2016; ANDRADE, 2017), along with a more extensive experimental re-evaluation. In such early works, the conceptual focus was on exploiting memory *consistency* properties for reducing the effort of finding design errors. Instead, in the scope of this thesis, the conceptual focus allowed a better comprehension of the impact of the techniques on coherent shared-memory verification, and it paved the way towards a *reusable* verification framework. Besides, it prompted the exploitation of techniques originally developed for improving the quality of *random* test generation for *directed* test generation. The first technique, called *chaining*, exploits canonical dependence chains for constraining the random generation of instruction sequences in such a way that the races induced at runtime are likely

to raise the coverage of state transitions due to collision events, i.e. due to memory operations colliding at a same location. The second technique, called *biasing*, exploits address space constraints for biasing random address assignment in such a way that the competition of distinct shared locations for a same cache set can be controlled for raising the coverage of state transitions due to cache eviction events. We built test generators relying on each of the proposed techniques, as well as on their combination, and we compared them to a conventional constrained random test generator for 8, 16, and 32-core architectures. Each of the four generators synthesized 1200 distinct test programs for verifying 10 faulty designs derived from each of the three architectures (144000 verification runs in total). For 32-core designs, the combination of the proposed techniques made at least 50% of the generation space capable of exposing errors, improved the median functional coverage by 44% and 83% at the two highest hierarchical levels, and reduced the average verification effort by one order of magnitude in many cases.

- 2. The exploitation of non-conventional constraints for increasing coverage faster during *directed* test generation. We propose a new mechanism that relies on a coverage model to improve the quality of non-deterministic tests. The technique dynamically exploits constraints capturing general properties of coherence protocols and cache memories for better control on transition coverage, which serves as a proxy for increasing the actual coverage metric adopted in a given verification environment. Being independent of coverage metric, coherence protocol, and cache parameters, the proposed technique is reusable across quite different designs and verification environments. As compared to a state-of-the-art generator of racy tests, the proposed technique reached a similar coverage much faster. For instance, when executing tests with 1K operations for verifying 32-core designs, the former reached 60% coverage around ten times faster than the latter. Besides, we identified challenging errors that could hardly be found by the latter within one hour, but were exposed by our technique in 5 to 30 minutes.

- 3. The exploration of the generation space for increasing coverage even faster during *directed* test generation. We propose a new approach that relies on a reformulation of directed test generation as a double-objective optimization problem. It explores neighborhoods without excluding optimal solutions from the search space while dynamically exploiting non-conventional constraints. This leads to a hybrid directed test generator that is not a simple combination of data-driven and model-based techniques. As compared to purely model-based and purely data-driven generators, the proposed technique leads to a better evolution of coverage with time. For instance, when targeting 32-core designs and a two-level MOESI protocol, the proposed approach was around 5 to 19 times faster to obtain the maximal coverage reached by a generator based on Genetic Programming, and it was 3 times faster to obtain the maximum coverage reached by generator based on Reinforcement Learning.

The second and the third contributions were reported in conference papers (ANDRADE et al., 2018; PFEIFER et al., 2020). The first and the third contributions were reported in journal articles (ANDRADE; GRAF; SANTOS, 2020; ANDRADE et al., 2020).

## 1.5 METHODOLOGY

For the experimental validation and evaluation of the proposed contributions, the following methodological steps were adopted: (1) use of pre-existing generators (capturing the state of the art) to serve as a basis for comparison; (2) building of a new generator for each of the proposed contributions; (3) synthesis of artificial design errors to challenge the generators; (4) simulation of the execution of the programs synthesized by each generator (pre-existing and new ones) for different design representions (with and without errors); (5) comparison of the generators in terms of effectivess (error discovery), coverage (fraction of all states or transitions visited), and effort (time for detecting errors or reaching proper coverage).

To serve as design representation, we adopted models for processor, memory, and interconnect (*O3*, *Ruby*, and *simple*, respectively) that are available in the gem5 simulation environment. The choice of such environment is due to pragmatic reasons, especially the availability (in the public domain) of a variety of complex coherence protocols, but also to allow the use of pre-existing checkers (locally available), whose role was crucial for making this work feasible in time. Simulations were performed for design representations with 8, 16, and 32 cores (each allowing out-of-order execution, as it is often the case for general-purpose applications) and for popular protocols such as 3-level MESI and 2-level MOESI. The effectiveness of the generators was evaluated with the injection of different archetypes of design errors, under different coverage metrics, and for a wide set of generation parameters.

To specify the distinct levels of cache, we adopted the terminology used in the gem5 environment, which does not always match the standard terminology used in computer architecture. To avoid confusion, Table 1 maps the relation between gem5's terminology and the standard one.

| Protocol      | gem5 | standard |

|---------------|------|----------|

|               | LO   | L1       |

| MESI 3-level  | L1   | L2       |

|               | L2   | L3       |

| MOESI 2-level | L1   | L1       |

| MOESI 2-level | L2   | L2       |

Table 1 – Relation between distinct terminologies for cache levels

Coherence protocols are functionally specified by Finite State Machines (FSMs). A transition between two states is launched by an input event, and it induces an output event. The hardware implementation of the FSM is subject to mistakes when a functional specification is translated into a Register Transfer Level (RTL) description, which is often performed manually.

Let us illustrate this by means of a simple example. When the write-back policy is adopted by a coherence protocol (say MESI), the update of shared memory occurs either when a modified block is about to be replaced in a private cache (similarly to what happens in a single core) or when a memory block becomes shared by the private caches of two cores (HENNESSY; PATTERSON, 2019). This second case is detected when some core owns a block and a second core requests the same block after a miss in its private cache. Assume that a designer uses the miss event as the criterion to launch the write-back update of a modified block into shared memory. Although this criterion is sufficient for launching write-back, it is not a necessary condition: a block becomes shared when one core writes to it and a second core reads it, but it is not shared when the second core writes to the block (before reading it), because the second one invalidates the block in the cache of the first core. Therefore, the necessary and sufficient condition for detecting the sharing of a block between two cores is a read miss of a modified block (and not any miss). As a result of the mistake, two distinct transitions of the specified FSM (one with write-back as output event and another without it) would appear to be the same transition in the implemented FSM. Therefore, both transitions of the specified FSM should be covered by the execution of a test program in order to expose that design error. That is why our methodology evaluates the coverage of FSM transitions, and it relies on wrong transitions (or wrong output events associated with transitions) to implement artificial design errors for challenging the generators and evaluate their impact on bug discovery.

## 1.6 ORGANIZATION OF THIS THESIS

The remainder of this thesis is organized as follows. Chapter 2 summarizes the sharedmemory concepts required for understanding the techniques proposed in later chapters. Chapter 3 describes the contribution to constrained random test generation (*chaining* and *biasing*). Chapter 4 reports the first contribution to directed test generation (*coverage-model-based test generation*). Chapter 5 describes the second contribution to directed test generation (*hybrid test generation*). Chapter 6 reports a comparison of model-based, data-driven, and hybrid approaches under the same level of constraint exploitation. Finally, Chapter 7 draws the overall conclusions and puts the work into perspective.

### 1.7 ACKNOWLEDGEMENTS

To implement the techniques described in this thesis and to perform the respective experiments, the author counted on the technical help and conceptual discussions with his fellow graduate students, especially Marleson Graf and Nícolas Pfeifer, which are co-authors of the publications that originally reported the contributions.

Thanks also to Eberle Rambo, Leandro Freitas, and Olav Henschel for the legacy infrastructure enabling this work.

## **2 FUNDAMENTAL CONCEPTS**

This chapter defines concepts required to understand the key aspects of the techniques proposed in Chapters 3 and 4. First, it introduces the order relations required to specify sharedmemory behavior. Then it presents two relations that can be exploited to improve the quality of directed test generation (Chapter 4). Finally, it reviews canonical multiprocessor dependence chains (GHARACHORLOO, 1995), which were originally proposed for specifying memory consistency, but are exploited as non-conventional constraints for improving the quality of test generation (Chapters 3 and 4).

## 2.1 SHARED-MEMORY BEHAVIOR

Let  $(O_j)_a^i$  denote a memory operation  $O_j$  issued by processor *i* that makes a reference to some memory location *a*. We replace *O* by *L* or *S* to specify that the operation is either a load or a store, respectively. As shorthand notation, we sometimes drop either a superscript or a subscript. Given two operations  $O_j$  and  $O_m$ , if the instruction inducing the first operation precedes the instruction inducing the second in some thread, they are in *program order*, written  $O_j \prec_{po} O_m$ . Two operations are in *execution order*, written  $O_j \leq O_m$ , if the first one ends execution before the second one starts executing.

A test program may induce many executions with distinct outcomes. An execution induces a memory *behavior*. Every valid behavior must satisfy a partial order  $\leq$  on the set of memory operations, which defines the cases in which the execution order is required to comply with the program order and with store serialization requirements. From the program order  $\prec_{po}$ , a Memory Consistency Model (MCM) specifies the allowed execution order  $\leq$ . The literature reports axioms formally defining  $\leq$  for distinct MCMs (MANOVIT; HANGAL, 2006; FREITAS; RAMBO; SANTOS, 2013; ROY et al., 2006).

#### 2.2 COLLISIONS AND CONFLICTS

We say that two memory operations *collide* if they make reference to the same memory location (ADIR et al., 2004). We say that two colliding operations *conflict* if at least one of them is a store (GHARACHORLOO, 1995). Formally,  $(L_j)_a^i \leq (S_m)_a^k$ ,  $(S_j)_a^i \leq (L_m)_a^k$ , and  $(S_j)_a^i \leq (S_m)_a^k$  denote colliding operations that conflict in execution order, while  $(L_j)_a^i \leq (L_m)_a^k$ denotes colliding operations that do not conflict. Colliding operations induce memory events that may trigger transitions of the Finite State Machine (FSM) specifying the behavior of a coherence protocol for a private cache controller. We say that a collision (or conflict) is *intraprocessor* or *inter-processor* when the operations involved are both issued by the *same* core (i = k) or by *distinct* cores  $(i \neq k)$ , respectively.

## 2.3 CANONICAL DEPENDENCE CHAINS

To formally define canonical chains, we adopted a description idiom where simple barriers are used for enforcing program order between operations to distinct locations. Despite the idiom's simplicity, chains can be built with more complex fences without loss of generality, as explained in Chapter 3.

**Definition 1.** Let MB be a memory barrier, i.e. a mechanism to restore program order between load and store operations whose order is relaxed by the memory model. We say that two operations are in significant program order, written  $O_j \prec_{spo} O_m$ , iff one of the following holds:  $(O_j)_a \prec_{po} (O_m)_{b=a}$  or  $(O_j)_a \prec_{po} MB \prec_{po} (O_m)_{b\neq a}$ .

**Definition 2.** We say that two operations are in conflict order, written  $O_j \leq_{co} O_m$ , if and only if  $(O_j)_a^i \leq (O_m)_{b=a}^k$  and at least one of them is a store.

**Definition 3.** We say that two operations are in significant conflict order, written  $O_j \leq_{sco} O_m$ , iff  $(L_j)_a^i \leq (S_m)_a^k \vee (S_j)_a^i \leq (L_m)_a^k \vee (S_j)_a^i \leq (S_m)_a^k \vee (L_j)_a^i \leq S_a^x \leq (L_m)_a^k$ .

**Definition 4.** A chain is a sequence  $X \prec U \prec \cdots \prec V \prec Y$  whose endpoints X and Y are memory operations, but  $U, \cdots, V$  may represent either memory operations or memory barriers. The relation  $\prec$  between two successive elements denotes one of the relations  $\prec_{po}, \prec_{spo}, \leq, \leq_{co}$ , or  $\leq_{sco}$ . Let  $\{A \prec B \prec\}_*$  denote zero or more pattern occurrences in the chain, and let  $\{A \prec B \prec\}_+$  denote one or more.

To specify chains, we use L, S, O to denote *types* of operations (respectively, load, store, any). We assume that distinct operation instances of each type will be used for building the chain. Gharachorloo (1995) specified a single category of uniprocessor chain and three categories of multiprocessor chains:

**Category 0**:  $O_a^i \prec_{po} \{O_a^i \prec_{po} O_a^i \prec_{po}\}_* O_a^i$ , where two successive elements cannot be of load type.

*Category 1*:  $S_a^i \leq L_a^j \prec_{po} L_a^j$  or  $S_a^i \leq L_a^j \prec_{po} S_a^j$ , where  $i, j \in \{1, \dots, p\}$  and  $i \neq j$ .

**Category 2:**  $O_a^i \prec_{spo} \{O_b^i \leq_{sco} O_b^j \prec_{spo}\}_+ O_a^j$ , where  $i, j \in \{1, \dots, p\}, i \neq j$  and b is arbitrary.

**Category 3:**  $S_a^i \leq_{sco} L_a^j \prec_{spo} \{O_b^j \leq_{sco} O_b^k \prec_{spo}\}_+ L_a^k$ , where  $i, j, k \in \{1, \dots, p\}, i \neq j$ ,  $j \neq k$  and b is arbitrary.

The next chapter gives examples of such chain categories.

# 3 RANDOM TEST GENERATION: ENFORCEMENT OF NON-CONVENTIONAL CONSTRAINTS

This chapter summarizes an early contribution to random test generation, which is a re-elaboration on previous work (ANDRADE, 2017; ANDRADE et al., 2018), as reported in a recently submitted article (ANDRADE; GRAF; SANTOS, 2020). It describes the key ideas to exploiting non-conventional constraints for building an efficient and effective random test generator to be used as the kernel of the coverage-directed test generators proposed in Chapters 4 and 5. The techniques described in this chapter are used to build an RTG Engine (for the framework depicted in Figure 1). For the detailed algorithms underlying the proposed random test generator, the reader is referred to previous work (ANDRADE, 2017; ANDRADE; GRAF; SANTOS, 2020).

This chapter is organized as follows. Section 3.1 summarizes related work. Section 3.2 gives an overview of the generation flow required to enforce non-conventional constraints on random test generation. Section 3.3 proposes a conceptual re-elaboration on the two techniques, *chaining* and *biasing* for the new focus on coherence verification. Section 3.4 reports an extensive re-evaluation of those techniques under the intended focus. Section 3.5 draws the chapter's conclusions.

## 3.1 RELATED WORK

Recall that a Memory Consistency Model (MCM) specifies rules defining not only the degree of program order relaxation, but also the extent of store atomicity (ADVE; GHARA-CHORLOO, 1996). There are two main shared-memory testing approaches that rely on MCMs: 1) the combination of litmus test generation with checking of valid execution witnesses; 2) the coupling of random test generation and memory-model checking.

The first approach exploits the MCM for automated generation of litmus tests (AL-GLAVE et al., 2010; ALGLAVE et al., 2015; LUSTIG et al., 2017), i.e. short concurrent programs designed to stress certain MCM behaviors. The MCM declares which test outcomes are legal and which are not (LUSTIG et al., 2017). Each test is run thousands of times to provoke the behavior that the test characterizes (ALGLAVE et al., 2015). Despite its success in uncovering subtle bugs when testing commercial architectures (ALGLAVE et al., 2010), it has been shown that this approach has limited coverage when applied at design time (ELVER; NAGARAJAN, 2016).

In the second approach, memory-model checkers exploit the MCM for reducing the coupling between testing and implementation details. The paper by Hangal, Vahia, and Manovit (HANGAL et al., 2004) inspired many post-silicon checkers, e.g. Manovit & Hangal (2006), Roy et al. (2006), Chen et al. (2009), Hu et al. (2012), which elaborated on their original idea. This allowed for more reusable checkers and extended post-silicon testing beyond race-free self-checking tests and towards more effective random tests with intensive data races. However,

the claims that post-silicon checkers could be efficiently reused (HANGAL et al., 2004; HU et al., 2012) for pre-silicon verification only hold for their best effort versions, but not for their complete versions (offering verification guarantees) (MANOVIT; HANGAL, 2006; HU et al., 2012), whose poor scalability with growing core counts severely limits their reuse at design time.

The literature reports two classes of pre-silicon *runtime* checkers based on memory models. A relaxed scoreboard (SHACHAM et al., 2008) was proposed for keeping multiple valid events per entry. It employs an update rule that stores a new event after each write and dynamically removes events that become invalid after each read until an entry narrows down to a single memory event. Since it never reconsiders a previous decision, the technique admittedly may raise false negatives for a given test program. In contrast, another work (FREITAS; RAMBO; SANTOS, 2013) proposes the use of multiple verification engines (one per core) and a single global checker to build an axiom-based runtime checker with proven guarantees.

Industrial environments have been relying on random generators for processor verification since the mid-1980's. For instance, Genesys-Pro (IBM's third-generation engine) casts random test generation into a constraint satisfaction problem (ADIR et al., 2004). It offers a unified framework for handling the whole system. Albeit not originally intended to handle nondeterministic behavior, the framework was extended to allow the random generation of collision scenarios (ADIR; SHUREK, 2002), because programs with intensive data races expose bugs faster (HANGAL et al., 2004; SHACHAM et al., 2008). Besides, this observation has also fostered random test generation techniques specifically targeting the memory subsystem through memory-model checking, either for post-silicon test (HANGAL et al., 2004; ROY et al., 2006; MANOVIT; HANGAL, 2006; HU et al., 2012) or pre-silicon verification (SHACHAM et al., 2008; FREITAS; RAMBO; SANTOS, 2013).

As opposed to post-silicon testing, verification cannot afford long tests to achieve coverage goals. To reach similar goals with shorter tests, directed-test generation has been advocated (WAGNER; BERTACCO, 2008; QIN; MISHRA, 2012; ELVER; NAGARAJAN, 2016). In face of the growing number of cores, one of the keys to scalability is the decomposition of the state space. In MCjammer (WAGNER; BERTACCO, 2008), each core is assigned an agent, which sees the coherence protocol in terms of a Dichotomic Finite State Machine (DFSM) (comprising only the states of the local node and the state of the environment). Cooperating agents formulate their coverage goals in terms of the DFSM, not the product FSM. Another technique (QIN; MISHRA, 2012) decomposes the state space into simpler structures such as hypercubes and cliques, which can be traversed (in an Euler tour) to avoid visiting the same transitions many times. It may allow full coverage with tests 50% shorter than a breadth-first traversal. In McVerSi (ELVER; NAGARAJAN, 2016), a genetic programming approach is used to progressively improve the quality of the test suite. It relies on a crossover function that prioritizes memory operations contributing to non-deterministic behavior.

Since directed-test generation often relies on some basic random generation engine, it can also benefit from improvements on constrained random test generation, as follows.

#### 3.2 THE PROPOSED GENERATION FLOW

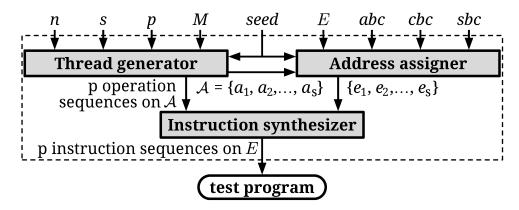

Figure 2 shows how the generation flow can be decomposed into interacting engines: thread generator, address assigner, and instruction synthesizer.

Figure 2 – Structure of the proposed random test generator.

Given the number of processors (p) of the architecture, the target numbers of memory operations (n) and shared locations (s) for the test program, a target mix of canonical dependence chains (M), and a random seed, the *thread generator* builds p random sequences (threads) containing each n/p operations with references to locations in the set  $\mathscr{A} = \{a_1, a_2, \dots, a_s\}$ . To build the sequences, the generator exploits canonical chains (GHARACHORLOO, 1995) to increase the probability of error exposure and to foster higher coverage.

Given the address space (*E*), the *address assigner* maps *locations*  $a_1, a_2, \dots, a_s$  to effective *addresses*  $e_1, e_2, \dots, e_s$ . The mapping relies on three types of biasing constraints to enforce desirable properties: 1) the *alignment biasing constraint* (*abc*) specifies the intended address stride, 2) the *sharing biasing constraint* (*sbc*) specifies whether true sharing must be enforced or not, 3) the *competition biasing constraint* (*cbc*) specifies how shared locations compete for cache sets.

The *instruction synthesizer* simply converts *p* sequences of memory *operations* referencing locations into *p* sequences of memory *instructions* referencing effective addresses. Besides, it also defines unique values to be written by store instructions, as required by most memory checkers (FREITAS; RAMBO; SANTOS, 2013; HANGAL et al., 2004; MANOVIT; HANGAL, 2006; HU et al., 2012).

# 3.3 A CONCEPTUAL RE-ELABORATION

This section informally address two previous contributions for improving the quality of random test generation:

1. A technique called *chaining* that exploits canonical multiprocessor dependence chains for constraining thread generation;

2. A technique called *biasing* that exploits a partitioning of the shared locations for constraining their effective addresses.

This section shows how and why chaining and biasing are likely to increase coverage and error detection.

## **3.3.1** Exploitation of chains for thread generation

The main idea behind thread generation is the exploitation of uniprocessor and multiprocessor dependence chains for stimulating as many distinct transitions as possible in the FSMs tracking the state of a block in multiple private caches. Let us illustrate that idea by means of examples. The examples assume that the program order between loads and stores to distinct locations can be relaxed, but it is certainly preserved when a memory barrier (MB) is inserted between them.

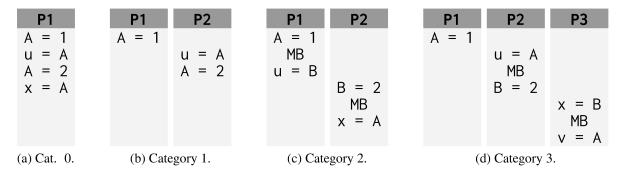

Let us first illustrate a few notions from Gharachorloo (1995), which are required for the examples. Two operations *conflict* if they collide at the same location and at least one of them is a store. Two operations from the same thread are in *significant program order* either if they conflict or if they are ordered by a memory barrier. Two operations from distinct threads are in *significant conflict order* either if they are in conflict order or if they are colliding loads with an intervening store in conflict order with them. Different *categories* of canonical chains can be defined by such significant orderings, as illustrated in Figure 3.

Figure 3 – Examples of chain categories 0, 1, 2 and 3. Upper case letters denote variables in memory; lowercase letters, variables in registers.

Figure 3a shows a uniprocessor dependence chain with all operations in significant program order. Since non-deterministic behavior is key to the exposure of shared-memory errors (HANGAL et al., 2004; SHACHAM et al., 2008; ELVER; NAGARAJAN, 2016), Figures 3b, 3c, and 3d illustrate multiprocessor dependence chains that form data races between threads, but where operations in a same thread must execute in significant program order. Races are formed when operations from distinct threads are in conflict order.

In Figure 3b, the chain constrains the first two operations and its endpoints to form data races for location A, and the last two operations to significant program ordering. In Figure

3c, the chain constrains the first two and the last two operations to be in significant program order (by exploiting memory barriers). In Figure 3d, if the value 1 is observed for A in P2 and the value 2 is observed for B in P3, then the value 1 must be observed for A also in P3. If a multiprocessor chain is formed in execution time (as shown), the outcome of the data race involving its endpoints is deterministic, otherwise it is non-deterministic. Since each scenario induces distinct state transitions, their exploitation in different test runs tends to benefit coverage. Chains from categories 1, 2, and 3 not only drive the generator to form data races, but they also favor significant orderings. Such orderings tend to reduce the number of valid execution witnesses that do *not* lead to coherence events while the races increase the chances of detecting invalid ones. Both concur to raise the probability of error exposure and to improve coverage. That is why we exploit a mix of such categories.

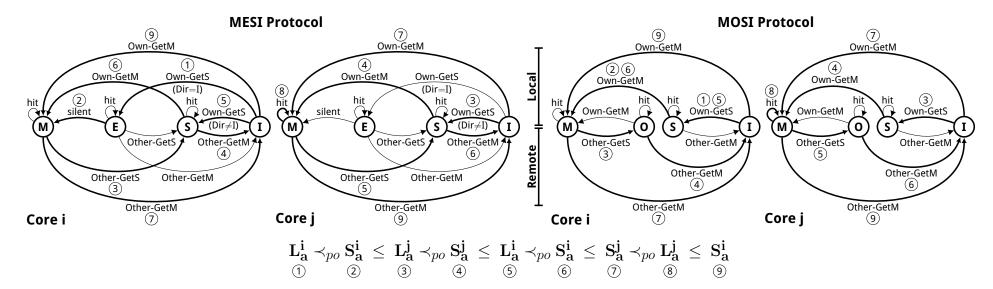

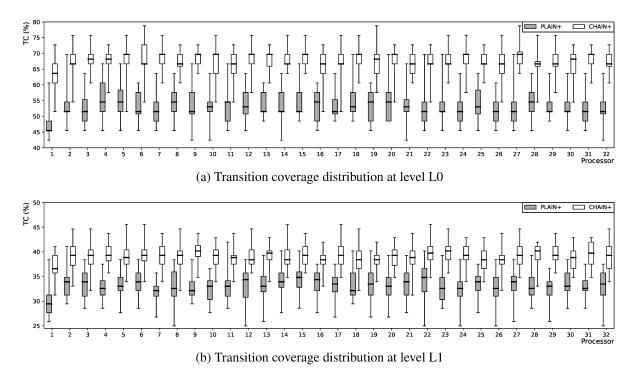

Our technique exploits canonical chains not for enforcing specific *consistency* rules, but for favoring proper *coherence* events instead. Figure 4 shows the conceptual connection between a canonical chain and coherence events for different protocols. Note that, as the operations in the chain are executed, an intra-core conflict leads to local requests that induce *distinct* transitions in the local Finite State Machine (FSM), while an inter-core conflict leads to local and remote requests that also induce *distinct* transitions. Thus, the chain's *alternation* between intra- and inter-core conflicts tends to induce different transitions, which favors transition coverage. Since distinct protocols have similar responses for the same coherence transactions (except for a few transitions and write-back actions), this general property of a canonical chain makes the impact of our technique largely *independent* of the protocol implemented in a given design.

Chaining assumes the relaxation of program order for accesses to distinct locations only when it builds a *given* chain. Its focus on coherence does not restrain its applicability for four reasons:

- the random selection of locations in distinct chains ensures that the stimulation of stronger orderings is not excluded from the generation space (albeit not favored in the scope of a given chain);

- 2. the checker is the guardian of memory model semantics (it may have to check orderings that are stronger than those relaxed for improving test quality);

- albeit the use of barriers does not improve coherence coverage, chaining preserves them for defining *general* significant orderings (instead of enforcing *stricter* conflict orderings, as in Figure 4), because they enable the detection of consistency errors not tied to coherence mechanisms;

- 4. when complex fences (as in ARMv8 and Power8) replace simple barriers in canonical chains, our technique can handle sophisticated MCMs.

Figure 4 – How a canonical chain improves the coverage of coherence events independently of the protocol implemented in a given design. For each protocol, it shows the FSMs of the private cache controllers of two cores *i* and *j*. The coherence events are classified as local (Own) and remote (Other), according to the origin of the request (same or distinct core). Finally, numbers match each operation with the transition it triggers. The example considers that no cache initially holds a valid copy of the block. For the MESI protocol, the example assumes that the directory controller keeps the aggregate state of a block in all private caches and knows whether some cache holds a valid copy of a block ( $Dir \neq I$ ) or none (Dir = I). For instance, the first operation in the chain ( $L_a^i$ ) induces a local event (Own-GetS) in core-*i*'s controller, and triggers a transition (I,S) for the MOSI protocol. For the MESI protocol, that local event triggers a transition (I,E), because no cache is initially holding a valid copy of the block. Note that the execution of that chain induces a sequence where transitions are rarely revisited (with the exception of transitions (I,S) and (S,M) for the MOSI protocol).

#### 3.3.2 Exploitation of constraints for address assignment

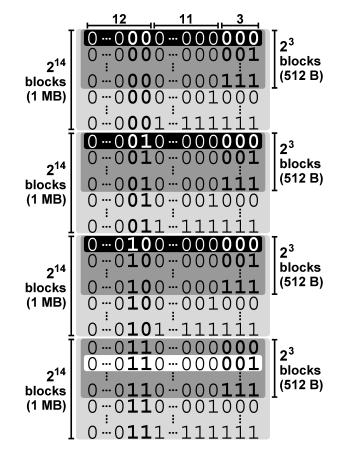

The main idea behind address assignment is the competition biasing constraint (cbc). Let us illustrate that idea by means of an example. Figure 5 shows a layout corresponding to a 32-bit address space, but where 26-bit block addresses are actually represented, because it assumes blocks with 64 bytes.

Figure 5 – An address assignment for four shared locations under address space constraints (assuming blocks with 64 bytes). A block address consists of a 12-bit tag and a 14-bit index where 11 bits are fixed but 3 may vary.

Suppose that the address range is limited to 4 MB, and it is partitioned into segments with 1MB each, as depicted by the light gray boxes. Suppose, however, that the address space to be exploited by the generator is constrained to only 2 KB in total, and it is uniformly distributed over the partitions in *useful* sub-ranges with 512 B each, as depicted by the dark gray boxes. Note that, due to the 1 MB partitioning, the block addresses can accommodate indices for identifying up to  $2^{14}$  distinct cache sets. In spite of that, the constraint imposed on useful sub-ranges leads to a bound of 8 for the number of different index identifiers. Besides, the constraint imposed on the amount of partitions of the full address range leads to a bound of four for the number of distinct tags identifiers. This way of restricting the address space into a few useful chunks (as depicted by the dark gray boxes inside the light gray ones) is sometimes exploited, e.g. Elver & Nagarajan (2016), as a static address space constraint for fostering replacement events.

Instead, we propose a biasing technique that dynamically exploits address space constraints to foster replacement events *without* the need for restricting addresses to useful subranges, as explained next. Consider the black and white boxes lying inside the dark gray boxes. They represent the assignment of effective addresses to four distinct shared locations. Such assignment can be seen as an instance of a general pattern such that three locations compete for the same cache set, and a single location that does not compete with the others, because it is mapped to a distinct cache set. Similar assignment instances could be induced by such same *competition pattern* within the useful address space.

For a given number of shared locations, a *competition biasing constraint cbc* =  $(\kappa, \chi)$  specifies competition patterns where all locations map to one out of  $\kappa$  cache sets, and at most  $\chi$  locations map to the same cache set. For instance, the address assignment illustrated in Figure 5 was induced by cbc = (2,3).

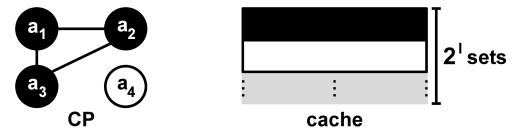

For a given *cbc*, there are different ways in which locations may compete for cache blocks, and they can be seen as patterns, each representing distinct ways of partitioning the set of locations, as follows. Let  $set(a_i, a_j)$  denote that  $a_i$  and  $a_j$  compete for the same cache set. Let *C* be the set of locations competing for a same cache set, i.e.  $C = \{(a_i, a_j) : a_i, a_j \in \mathscr{A} \land set(a_i, a_j)\}$ . Since *C* is an equivalence relation, a *competition pattern* is a collection  $CP = \{A_x\}$  forming a partition of the set  $\mathscr{A}$  where each set  $A_x$  is an equivalent class induced by C.

Figure 6 illustrates the notion of Competition Pattern (CP) for a scenario with four locations and a cache with  $2^{I}$  sets. For convenience of illustration, each equivalent class is represented as a clique of an undirected graph. Therefore, given a  $cbc = (\kappa, \chi)$  inducing a CP,  $\kappa$  and  $\chi$  could be seen as clique cover and chromatic numbers, respectively.

Figure 6 – Meaning of a competition pattern induced by cbc = (2,3).

For a given number *s* of locations, a same *cbc* may induce a collection of CPs. Thus, to avoid limiting the verification space, the address assigner must be able to randomly select one among them. Notice, however, that not all pairs ( $\kappa, \chi$ ) represent feasible constraints. Fortunately, the collection of all feasible pairs for a given *s* can be easily precomputed.

Note that *cbc* constraints can be exploited for inducing cache evictions. Given an *n*-way cache, a block is evicted iff n + 1 distinct and successive addresses compete for the same set; therefore,  $\chi \ge n + 1$  is a necessary condition for cache eviction. Besides,  $\kappa$  defines the number of distinct cache sets accessed by a test program.

Another desirable property of an address assignment is specified by the *sharing biasing constraint* (*sbc*). The address assignment in Figure 5 can be used to illustrate this notion. Note

that the locations competing for the same cache set have distinct block addresses: despite the same index, their tags are all different. Since unrelated shared variables are not stored in the same memory block, such assignment precludes false sharing. Actually, the *sbc* is a Boolean value specifying if true sharing must be enforced or not.

Yet another desirable property is specified by the *alignment biasing constraint (abc)*. The *abc* is a natural number specifying that all effective addresses must be aligned to  $2^{abc}$ -byte boundaries. For instance, if we enforce the alignment to  $2^6$  bytes, the six offset bits implicit in Figure 5 must be zero for all effective addresses to be exploited by the generator.

The motivation for mapping locations to effective addresses lies in the control of replacement events. For instance, the alternation between *cbcs* enabling and disabling block replacement tends to avoid revisiting the same state transition, which favors coverage and the probability of exposing design errors.

When multiple data races for distinct locations do not interfere with each other, the state transitions induced by each of them are quite similar. However, when they are coupled due to address space constraints (e.g. if two distinct locations are allocated in the same memory block or if they map to the same cache set), the induced state transitions tend to be rather different. That is why the combination of chaining and biasing is likely to lead to higher coverage than the application of each technique alone, as reported next.

# 3.4 EXPERIMENTAL EVALUATION