# UNIVERSIDADE FEDERAL DE SANTA CATARINA CTC - CENTRO TECNOLÓGICO DA UFSC PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Rodrigo Casanova dos Santos Wrege

ISFETs in standard CMOS technology: design and test

| Rodrigo Casanova dos Santos Wrege                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

| ISFETs in standard CMOS technology: design and test                                                                                                                                                                   |

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

| Tese submetida ao Programa de Pós Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do título de Doutor em Engenharia Elétrica.  Orientador: Prof. Dr. Carlos Galup-Montoro. |

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                       |

| Florianópolis                                                                                                                                                                                                         |

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Wrege, Rodrigo Casanova dos Santos

ISFETs in standard CMOS technology : design and test /

Rodrigo Casanova dos Santos Wrege ; orientador, Carlos

Galup-Montoro, 2022.

139 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2022.

Inclui referências.

1. Engenharia Elétrica. 2. ISFET. 3. Sensor de pH. 4. Modelagem do ISFET. 5. Caracterrização do ISFET. I. Galup Montoro, Carlos. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

# Rodrigo Casanova dos Santos Wrege

# ISFETs in standard CMOS technology: design and test

O presente trabalho em nível de doutorado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. André Avelino Pasa, Dr. Universidade Federal de Santa Catarina

Prof. Carlos Renato Rambo, Dr Universidade Federal de Santa Catarina

Profa. Daniela Ota Hisayasu Suzuki, Dra. Universidade Federal de Santa Catarina

Eng. William Prodanov, Dr. Chipus Microeletrônica S. A.

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de doutor em Engenharia Elétrica.

Prof. Telles Brunelli Lazzarin, Dr. Coordenação do Programa de Pós-Graduação

Prof. Carlos Galup-Montoro, Dr. Orientador

Florianópolis, 2022.

#### **ACKNOWLEDGMENTS**

I would like to thank my mother Gislaine Wrege, my father João Alberto Wrege (in memoriam), my sister Raquel Wrege, my cousin Luciana Rassier, other family members and friends for the help and support during these years of study, Professors Dr. Carlos Galup-Montoro and Dr. Marcio Cherem Schneider from LCI/UFSC, for sharing the knowledge and time required for this research. Thank you to Eliete Aguiar, for all her support and kindness.

I would also like to thank CEO Murilo Pessatti, Dr. William Prodanov and other technical staff from Chipus for numerous technical discussions, Celso Peter, Samuel Maraschin and Ariadna Schuck from ITT Chip for the epoxy chamber development, Prof. Dr. André Pasa from UFSC and Prof. Dr. Marcelo Carreno from USP for post processing advice, Prof. Dr. Carlos Rambo and MsC Bruno Weling from Lamate/UFSC for sputtering, Dr. Lucas Blanes, Mateus Stracke, Viviane de Oliveira and Geovani Mendonça from Laboratório de Prototipagem/Fiocruz-PR for the support during wet tests, Prof. Dr. Rodrigo Munoz from UFU for electrochemical advices, Profa. Dra. Janaina Guimarães from UFSC, Profa Dra Daniela Suzuki from UFSC, members of LCI/UFSC and others who contributed to this research.

Finally, thanks to PPGEEL/UFSC and the Brazilian governmental agency Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPQ) for granting me with a scholarship and for funding this study.

#### **RESUMO**

Transistores de efeito de campo sensível a íons (ISFETs) são sensores de íons baseados em transistores de efeito de campo metal-óxido-semicondutor (MOSFETs) e são aplicados em diversas áreas, incluindo detecção de vírus e sequenciamento de DNA. ISFETs implementados em tecnologia CMOS (complementary metal-oxide semiconductor) padrão adotam a típica passivação de Si<sub>3</sub>N<sub>4</sub> como camada sensitiva e se beneficiam de alto níveis de integração sem a necessidade de etapas de pós-fabricação. Porém, esta implementação é associada a não-idealidades, como offsets aleatórios na tensão de limiar devido a cargas presas na passivação, que necessitam de maior compreensão e caracterização. Para a análise de parâmetros elétricos sem os efeitos eletroquímicos das medições convencionais, esta tese propõe um teste a seco, no qual uma fina camada de metal substitui a solução e o eletrodo de referência. A estrutura do sensor foi analisada e foi desenvolvido um modelo físico para ISFETs em contato com líquidos e com metais. Esta tese apresenta o projeto de dois chipsteste projetados no software Virtuoso® e enviados para fabricação em tecnologias CMOS comerciais de 0.18- e 0.35-um. ISFETs fabricados na tecnologia de 0.18 um foram encapsulados com uma câmara de epoxy, metalizados com uma camada de ouro e caracterizados. Resultados de testes a seco, analisados com o modelo físico, mostraram que n-ISFETs e p-ISFETs tiveram, em média, offsets devido a cargas presas similares quando estão no mesmo chip, e uma larga variação entre chips. A dispersão da tensão de limiar medida com o teste a seco está de acordo com as dispersões reportadas na literatura para testes com líquidos. Sensibilidades ao pH medidas de um n-ISFET e de um p-ISFET presentes em chips não-metalizados produzidos no processo de 0.18 µm foram próximas ao valor previsto pelo modelo simulado no MATLAB® (~45 mV/pH). Esta tese também propõe uma topologia de circuito que permite leituras diferenciais e não-diferenciais e apresenta a análise do circuito e simulações. A caracterização de ISFETs fabricados mostrou que o teste a seco pode ser útil como uma ferramenta complementar ao teste com líquidos para análises de ISFETs. A fabricação dos chips foi custeada pela empresa Chipus Microeletrônica S.A. O encapsulamento, a metalização e o teste com líquidos foram concedidos pelo Itt Chip/UNISINOS, LAMATE/UFSC e Laboratório de Prototipagem/FIOCRUZ-PR, respectivamente.

Palavras-chave: ISFET. Sensor de pH. Modelagem do ISFET. Caracterização elétrica. Teste a seco.

#### RESUMO EXPANDIDO

# Introdução

Transistor de efeito de campo sensível a íons (ISFET) é um micro sensor baseado em transistor de efeito de campo metal-óxido-semicondutor (MOSFET) e é capaz de medir concentrações iônicas, geralmente pH. O ISFET vem sendo usado em diversas áreas, incluindo análise de alimentos [1], mapeamento iônico [2], detecção de bactérias [3] e de vírus [4], sequenciamento de DNA [5] e detecção de estágios iniciais de câncer [6]. O conceito de ISFET surgiu em 1970 [7] mas somente em 1999 foi proposta uma técnica para implementar ISFETs em tecnologia CMOS (complementary metal-oxide semiconductor) padrão [8]. Apesar do crescente uso dos ISFET em diversas áreas e dos benefícios em se usar o processo CMOS padrão, a implementação destes sensores apresenta certas não-idealidades. Algumas destas não-idealidades possuem valores imprevisíveis, como as cargas presas na passivação, e necessitam de uma melhor compreensão e caracterização. Frente a isso, esta tese foca no projeto, modelagem e medição de ISFETs fabricados em tecnologia CMOS padrão. Este trabalho aborda os desafios gerados pelas não-idealidades e propõe um teste a seco, no qual a solução e o eletrodo de referência são substituídos por uma fina camada de metal. Desta forma, o teste a seco permite a medição de parâmetros elétricos do sensor, tais como atenuação capacitiva e cargas presas na passivação, sem as interferências eletroquímicas dos testes convencionais. Este teste é proposto como uma ferramenta complementar ao teste com líquidos na análise de ISFETs. Um modelo físico é proposto tanto para ISFETs em contato com líquidos como em contato com metais. Além disso, uma topologia de circuito para leituras diferencias e não-diferenciais também é apresentada neste trabalho.

# **Objetivos**

ISFET são comumente caracterizados utilizando líquidos (geralmente com pH 7) e um eletrodo de referência (geralmente Ag/AgCl) cujas características eletroquímicas afetam na medição. Além da sensibilidade ao pH, outros parâmetros elétricos dos ISFETs precisam ser caracterizados para se desenvolver um projeto apropriado. Desta forma, esta tese propõe um teste a seco para uma caracterização puramente elétrica de parâmetros dos ISFETs, sem influências eletroquímicas. Neste teste, a solução e o eletrodo são substituídos por uma fina camada de metal. O teste a seco remove efeitos degradantes das medições convencionais, tais como as correntes de fuga do eletrodo de referência que afetam a deriva temporal [9] e a degradação da camada de passivação causada por longos períodos de contato com o liquido [10]. A estrutura do ISFET em contato com líquidos e com a camada de metal é analisada e é proposto um modelo físico para as condições liquidas e metalizadas. O modelo é utilizado juntamente com as medidas para a análise dos sensores projetados durante esta tese e fabricados em tecnologia CMOS comercial. Além disso, este trabalho propõe o projeto de um chip teste CMOS optimizado para medidas diferenciais e apresenta uma topologia de circuito que permite tanto medidas diferenciais quanto não-diferenciais.

#### Metodologia

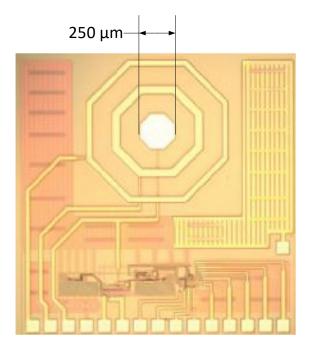

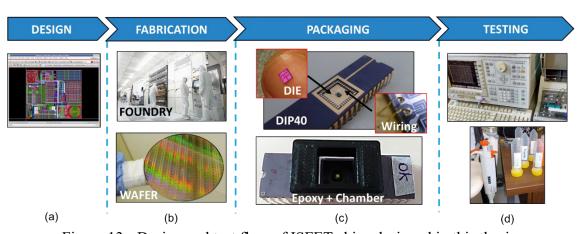

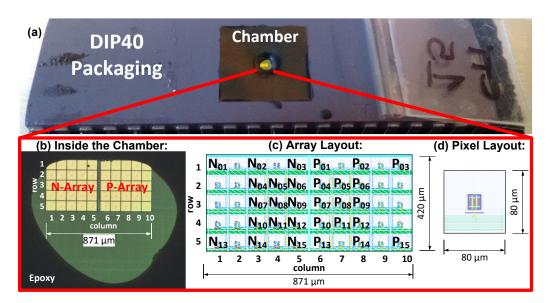

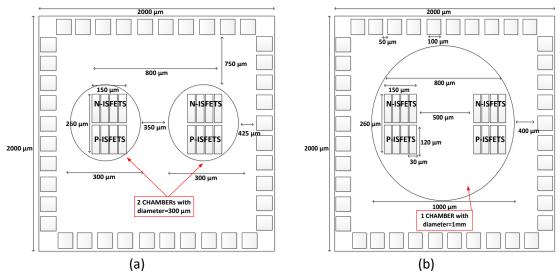

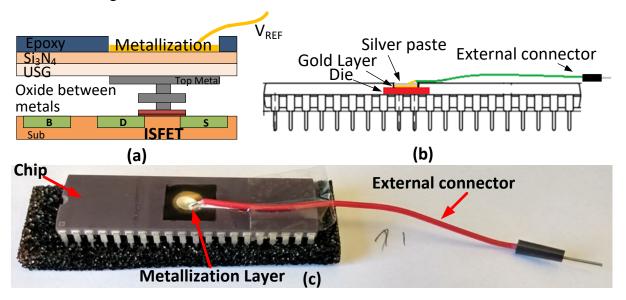

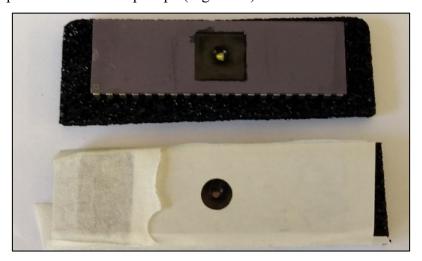

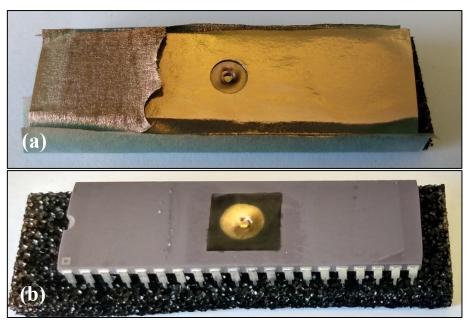

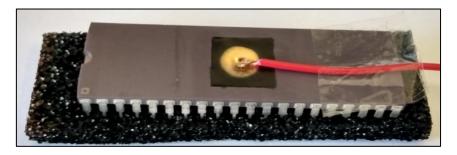

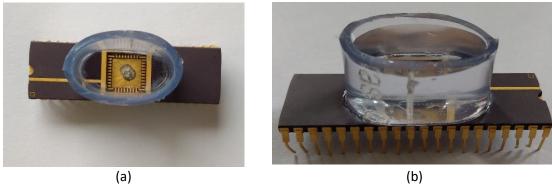

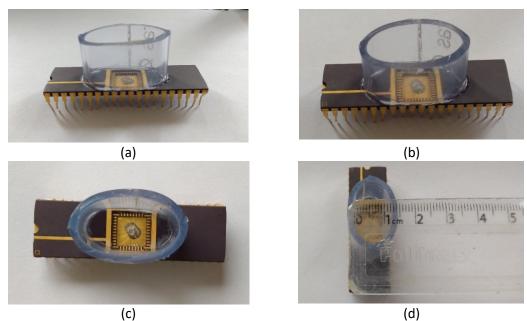

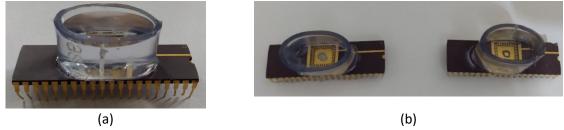

Esta tese apresenta o projeto de dois chips enviados para fabricação em tecnologias CMOS comerciais. Ambos os chips foram projetados na ferramenta Virtuoso® e tiveram suas fabricações custeadas pela empresa Chipus Microeletrônica S.A (Florianópolis/SC, site: [11]). O primeiro chip foi projetado em 2018 e fabricado em tecnologia CMOS 0.18 μm (Malaysia). Este chip possui matrizes de 15 n-ISFETs e 15 p-ISFETs e foi encapsulado em DIP40 com uma câmara de epoxy com dimensões aproximadas de 1 mm de diâmetro e 0.5 mm de altura, a qual cobriu *pads* e *wire bonding*, deixando exposta somente a área dos sensores. Esta câmara foi desenvolvida e aplicada pelo ITT Chip (São Leopoldo/RS, site: [12]). O segundo chip foi enviado para fabricação em 2021 em uma tecnologia CMOS 0.35 μm. Este chip

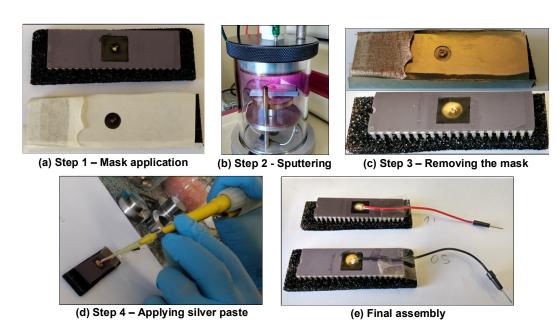

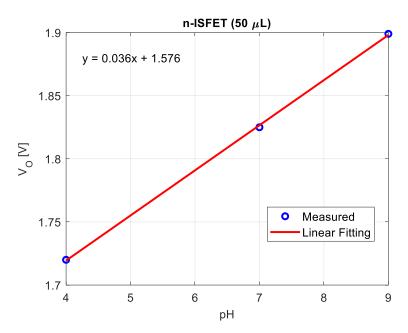

contém matrizes de 8 n-ISFETs e 8 p-ISFETs distribuídas para facilitar a aplicação de duas micro câmaras sobre o chip, para se realizar medidas diferenciais. O teste a seco, proposto neste trabalho, foi realizado através da deposição de uma camada de ouro sobre o chip fabricado na tecnologia de 0.18 µm, utilizando-se a técnica de DC *sputtering*. O procedimento de metalização foi realizado no laboratório LAMATE/UFSC, sob coordenação do Prof. Dr. Carlos Rambo. A sensibilidade ao pH foi medida depositando-se buffers de pH 4, 7 e 9 sobre chips não metalizados da tecnologia de 0.18 µm e polarizados com um eletrodo padrão Ag/AgCl. Os testes com líquidos foram realizados no laboratório Friocruz/PR, sobre coordenação do Dr. Lucas Blanes. As simulações do modelo e dos circuitos foram realizadas nos programas computacionais MATLAB®, LTSPICE® e Virtuoso® e o projeto da PCB para testes com líquidos no programa Proteus®.

#### Resultados e Discussão

Os ISFETs fabricados no processo de 0.18 µm foram caracterizados em bancada. Resultados da caracterização a seco de quatro chips metalizados foram analisados e comparados com o modelo desenvolvidas nesta tese. Mediu-se os parâmetros elétricos de cerca de 100 ISFETs, incluindo tipos n- e p-. Utilizando-se o modelo proposto e o teste a seco, estimou-se as cargas presas na passivação, que são responsáveis por grandes variações na tensão de limiar dos dispositivos. Em resumo, n-ISFETs e p-ISFETs do mesmo die apresentaram, em média, offsets similares, porém apresentaram grandes variações entre chips. A dispersão da tensão de limiar medida com o teste a seco está de acordo com as dispersões reportadas na literatura para testes com líquidos. As sensibilidades ao pH medidas de um n-ISFET e de um p-ISFET de chips não-metalizados foram próximas ao valor previsto pelo modelo teórico (cerca de 45 mV/pH). A topologia de um circuito para medidas diferenciais e não diferenciais foi proposta e simulada. Resultados de simulação estão de acordo com a análise teórica, e a topologia permitiria a compensação de certas não-idealidades do sensor.

#### **Considerações Finais**

Este trabalho mostrou a possibilidade de se utilizar um teste a seco para a determinação de parâmetros puramente elétricos dos ISFETs sem influências eletroquímicas da solução e do eletrodo de referência. A modelagem do ISFET metalizado permitiu a estimativa de cargas presas na passivação. Trabalhos futuros podem aprimorar a técnica de metalização para aplica-la em dispositivos não-encapsulados, permitindo uma caracterização mais barata e mais rápida. O teste a seco pode ser usado para uma análise separada das contribuições químicas e elétricas de efeitos como ruido e temperatura nas características dos ISFETs. Durante os testes com líquidos, percebeu-se a necessidade de se aplicar uma técnica de limpeza mais robusta para a reutilização dos chips, devido a instabilidades após algumas horas de teste. A câmara de epoxy poderia ser aprimorada para permitir a aplicação de duas câmaras sobre um chip, o que permitiria realizar medidas diferenciais entre ISFETs do mesmo chip. Com uma análise mais profunda dos parâmetros, os sensores poderão ser aplicados na análise de amostras biológicas e serem integrados juntamente com o circuito de leitura e com um pseu-eletrodo para formar um sistema portátil, adequado para aplicações *lab-on-a-chip*.

**Palavras-chave**: ISFET. Sensor de pH. Modelagem do ISFET. Caracterização elétrica. Teste a seco.

#### **ABSTRACT**

Ion-sensitive field-effect transistors (ISFETs) are ion sensors based on metal-oxidesemiconductor field-effect transistors (MOSFETs) and are used in various applications, including virus detection and DNA sequencing. ISFETs implemented using standard complementary metal-oxide semiconductor (CMOS) technology adopt the inherent Si<sub>3</sub>N<sub>4</sub> passivation as the sensing layer and benefit from high integration levels with no need for postprocessing steps. However, this implementation is associated with nonidealities, such as random offsets in the threshold voltage due to charges trapped in the passivation, that still need better understanding and characterization. For the analysis of electrical parameters without the electrochemical effect from conventional measurements, this thesis proposes a dry test wherein a thin metal film replaces the solution and reference electrode. The sensor structure was analyzed, and a physical model of ISFETs in contact with electrolytes and metals was developed. This thesis presents the project of two test chips designed using the software Virtuoso® and sent for fabrication in 0.18- and 0.35-µm commercial CMOS technologies. ISFETs fabricated using the 0.18 µm technology were packaged with an epoxy chamber, metallized with a gold film and characterized. Dry test measurements, conducted using the physical model, showed that n-ISFETs and p-ISFETs had, on average, similar intradie offsets due to trapped charges and high die-to-die variations. The dispersion of threshold voltage measured using the dry test was in accordance with the dispersions reported in the literature for wet tests. The measured pH sensitivities of an n-ISFET and a p-ISFET from nonmetalized chips produced in the 0.18 µm process were close to the value predicted by the model simulated in MATLAB® (~45 mV/pH). This thesis also proposes a circuit topology that allows both differential and single-ended measurements and presents the circuit analysis and simulation. The characterization of the fabricated ISFETs showed that the dry test could be useful as a complementary tool to the wet test for ISFET analysis. The fabrication of the chips was funded by Chipus Microeletrônica S.A. The packaging, metallization, and wet measurements were supported by Itt Chip/UNISINOS, LAMATE/UFSC and Laboratório de Prototipagem/FIOCRUZ-PR, respectively.

**Keywords:** ISFET. pH sensor. ISFET modelling. Electrical characterization. Dry testing.

# LIST OF FIGURES

| Figure 1 - Comparation of an ISFET-based handheld device, antigen tests and PCR                                |

|----------------------------------------------------------------------------------------------------------------|

| instruments for detection of infectious diseases [13]                                                          |

| Figure 2 – (a) Illustration of the ISFET cross-section in standard CMOS technology.                            |

| (b) Simplified ISFET capacitive model (adapted from [15]). (c) The ISFET symbol (B, S, D,                      |

| and G are the bulk, source, drain and floating gate terminals, respectively.)26                                |

| Figure 3 - Main ISFET nonidealities: (a) trapped charges offset and capacitive                                 |

| attenuation, (b) temporal drift, (c) temperature effect, and (d) noise [10], [18]31                            |

| Figure 4 - Ag/AgCl reference electrode [40]                                                                    |

| Figure 5 - A built-in Au qRE [42]34                                                                            |

| Figure 6 – Single-ended readout circuits: (a) source follower [44], (b) CVCC [1], and                          |

| (c) current mode [30]                                                                                          |

| Figure 7 - Example of chambers for (a) single-ended [31], and (b) differential                                 |

| measurements [23]                                                                                              |

| Figure 8 - Differential measurements: (a) voltage [49], and (b) current mode [23]37                            |

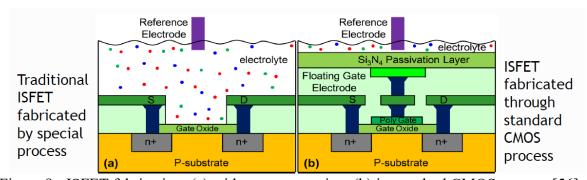

| Figure 9 - ISFET fabrication: (a) with post-processing, (b) in standard CMOS                                   |

| process [56]                                                                                                   |

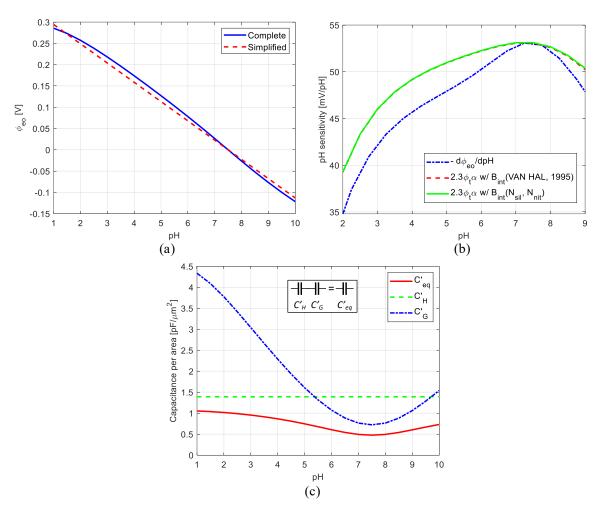

| Figure 10 - Simulations of (a) $\phi_{eo}$ using the complete and the simplified expressions,                  |

| (b) pH sensitivity simulated with - $d\phi_{eo}/dpH$ , and with $\beta_{int}$ from [16] and from eq. (20), and |

| (c) electrochemical capacitances as a function of pH                                                           |

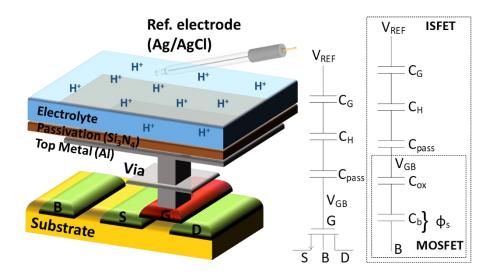

| Figure 11 - Cross-section illustration, schematic showing the MOSFET and the                                   |

| capacitive model of an ISFET with electrolytes                                                                 |

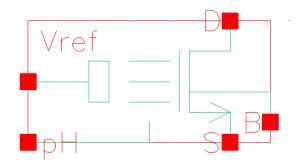

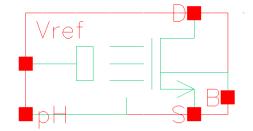

| Figure 12 - n-ISFET symbol implemented on Cadence                                                              |

| Figure 13 - Design and test flow of ISFET chips designed in this thesis58                                      |

| Figure 14 - Chip SilTerra: (a) the chip encapsulated in DIP40, (b) details of the                              |

| epoxy chamber, (c) array layout with identification of devices, and (d) pixel layout60                         |

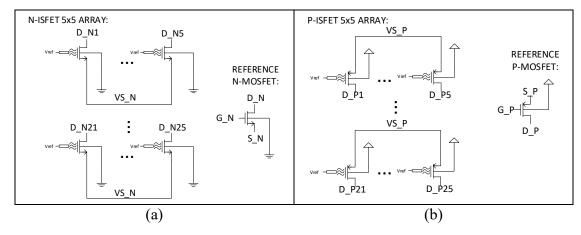

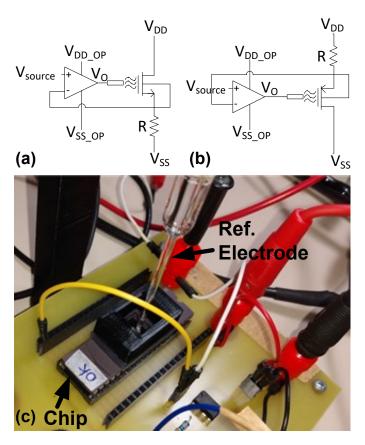

| Figure 15 - Electrical connections of the (a) n-channel and (b) p-channel devices                              |

| [83]61                                                                                                         |

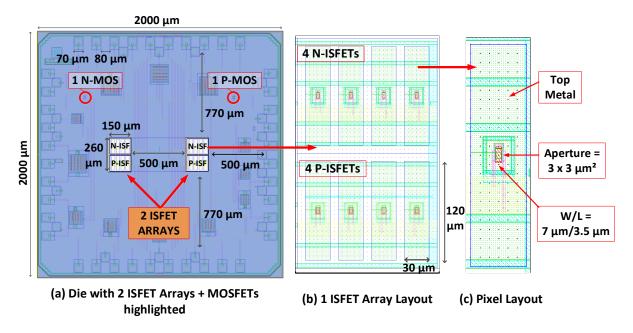

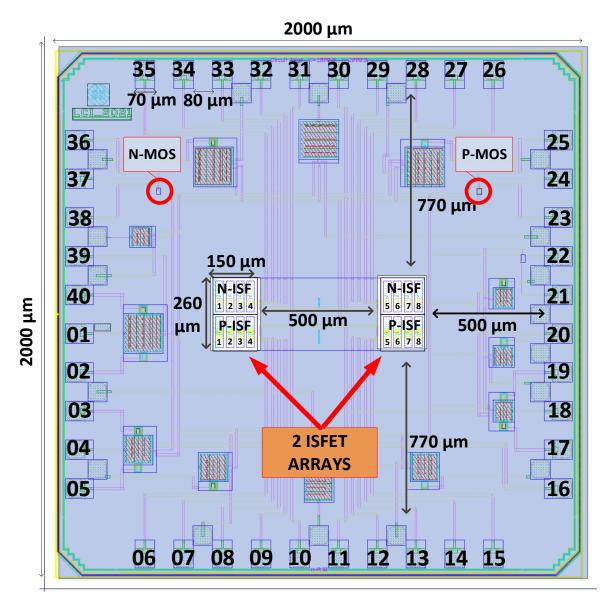

| Figure 16 - Chip Onsemi: (a) die with 2 ISFETs arrays and MOSFETs highlighted,                                 |

| (b) array layout formed by 4 n-ISFETs and 4 p-ISFETs, and (c) pixel layout                                     |

| Figure 17 - Chip Onsemi: illustrations of the die with (a) 2 chambers for differential                         |

| measurements, and (b) 1 chamber for single-ended measurements                                                  |

| Figure 18 - (a) Cross-section of a metallized ISFET; (b) diagram of the die                                           |

|-----------------------------------------------------------------------------------------------------------------------|

| encapsulated in DIP40 package, and (c) encapsulated chip                                                              |

| Figure 19 - Steps of the Au metallization process                                                                     |

| Figure 20 - Cross-section illustration, schematic showing MOSFET and the                                              |

| capacitive model of an ISFET with a metallization layer                                                               |

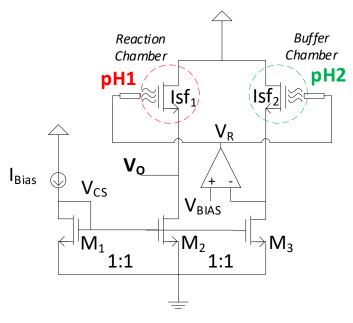

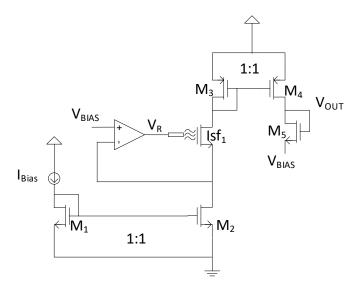

| Figure 21 - Differential circuit (bulk terminals are connected to ground)72                                           |

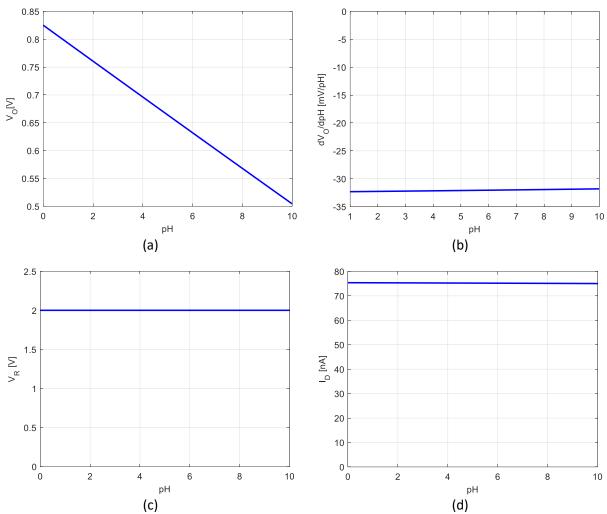

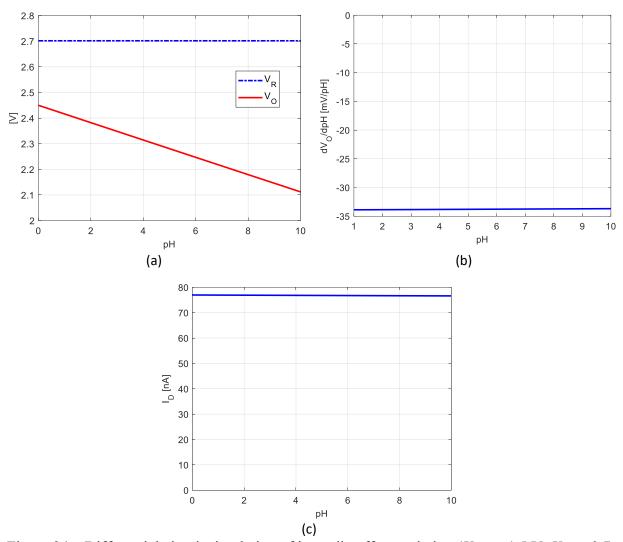

| Figure 22 - Differential circuit simulation for pH from 0 to 10: (a) $V_O$ , (b) $V_O$ pH                             |

| sensitivity, (c) $V_R$ , and (d) ISFET1 drain current                                                                 |

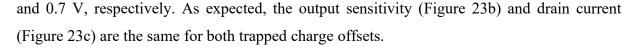

| Figure 23 – Differential circuit simulation with both ISFETs with the same $V_{tc}$ of -1.5                           |

| V and 0.7 V and pH from 0 to 10: (a) $V_R$ and $V_O$ , (b), $V_O$ pH sensitivity, and (c) ISFET1 drain                |

| current                                                                                                               |

| Figure 24 – Differential circuit simulation of intra-die offset variation ( $V_{tc1} = -1.5 \text{ V}$ ,              |

| $V_{tc2} = 0.7 \text{ V}$ ) and pH from 0 to 10: (a) $V_O$ and $V_R$ , (b) $V_O$ pH sensitivity, and (c) ISFET1 drain |

| current                                                                                                               |

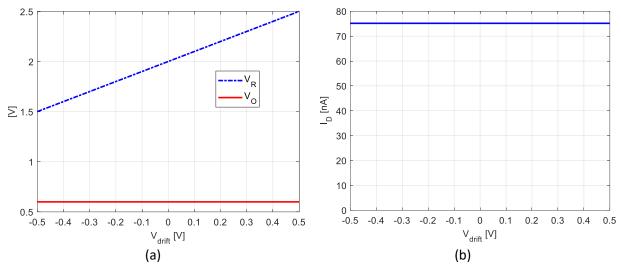

| Figure 25 - Differential circuit simulation with a common-mode voltage variation                                      |

| $V_{drift}$ : (a) $V_O$ and $V_R$ , and (b) ISFET1 drain current.                                                     |

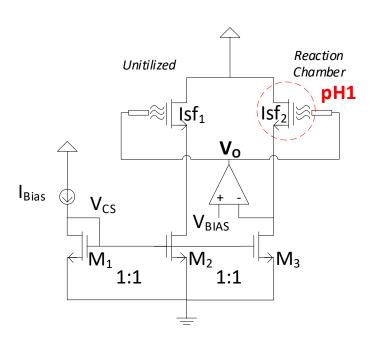

| Figure 26 - Single-ended configuration (bulk terminals are connected to ground) 80                                    |

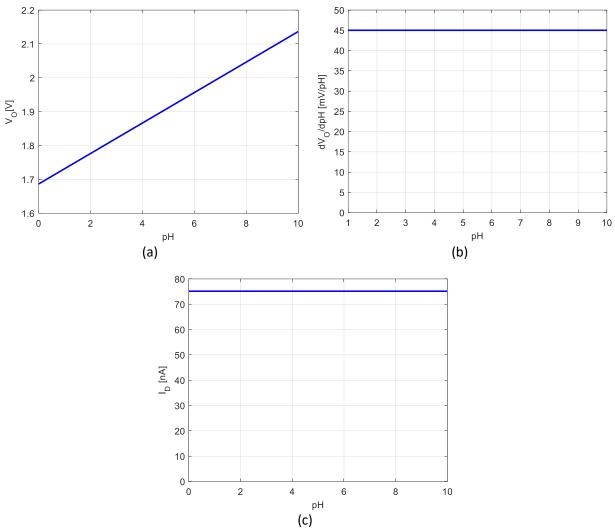

| Figure 27 – Single-ended circuit simulation for pH from 0 to 10: (a) $V_O$ , (b) $V_O$ pH                             |

| sensitivity, and (c) ISFET drain current.                                                                             |

| Figure 28 - Test setup (test fixture was closed during the measurements)83                                            |

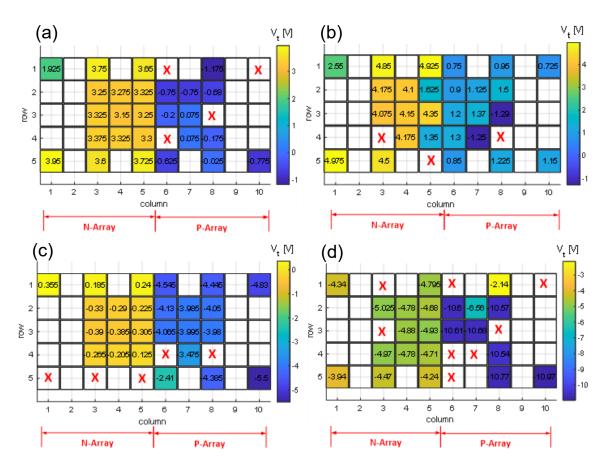

| Figure 29 - Spatial variation of ISFETs threshold voltage across the array after the                                  |

| dry characterization of four chips: (a) Chip11, (b) Chip05, (c) Chip03 and (d) Chip16. ("X"                           |

| indicates a failed device; empty spaces are dummy elements)                                                           |

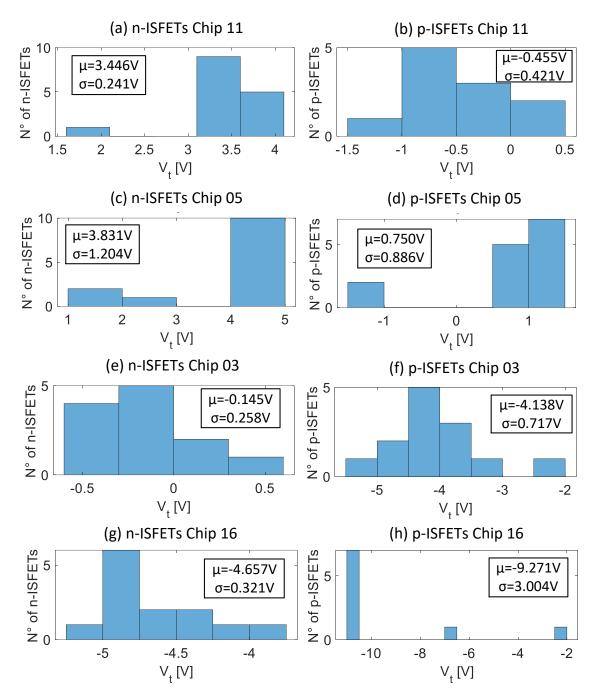

| Figure 30 - Histograms of the threshold voltages measured on the n-ISFET and p-                                       |

| ISFET arrays of the four metallized chips                                                                             |

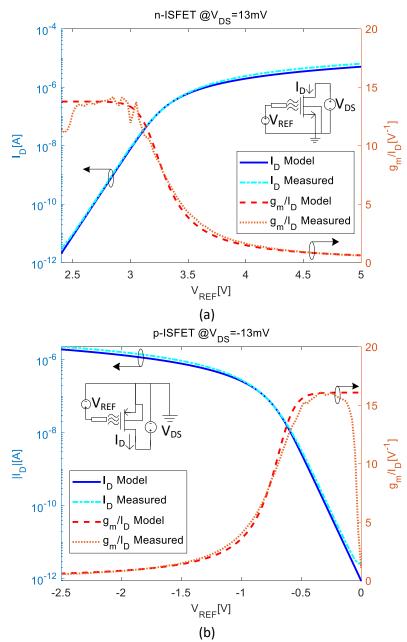

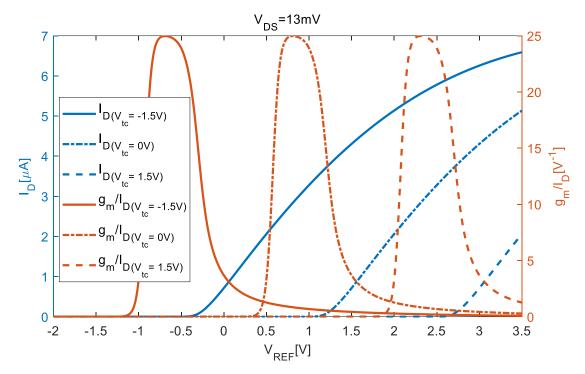

| Figure 31 - $I_D$ vs $V_{REF}$ and $g_m/I_D$ vs $V_{REF}$ of the model and measurements for (a) n-                    |

| ISFET 06 and (b) p-ISFET 05 from Chip 1186                                                                            |

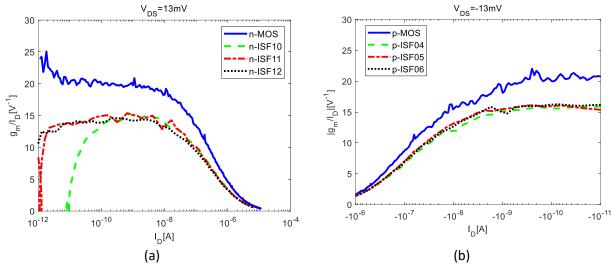

| Figure 32 - Measured $g_m/I_D$ vs $I_D$ curves of a MOSFET from Chip 20 and ISFETs                                    |

| from Chip 11 for (a) n-type and (b) p-type                                                                            |

| Figure 33 - Readout circuit used to measure pH sensitivity: (a) n-ISFET schematic,                                    |

| (b) p-ISFET schematic, and (c) implementation                                                                         |

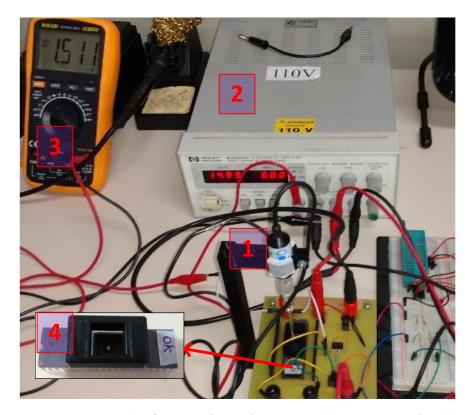

| Figure 34 - Wet test setup: (1) reference electrode support, (2) power supply, (3)                                    |

| multimeter, and (4) 3D chamber92                                                                                      |

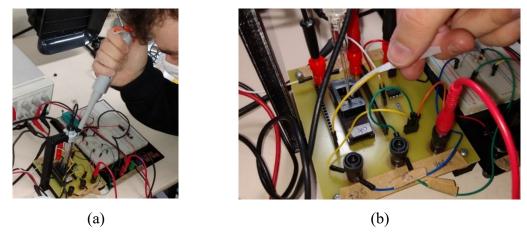

|         | Figure 35 - (a) A micro pipette was used to fill and remove the buffer solut                                     | ion. (b)              |

|---------|------------------------------------------------------------------------------------------------------------------|-----------------------|

| Drying  | with a wiper                                                                                                     | 92                    |

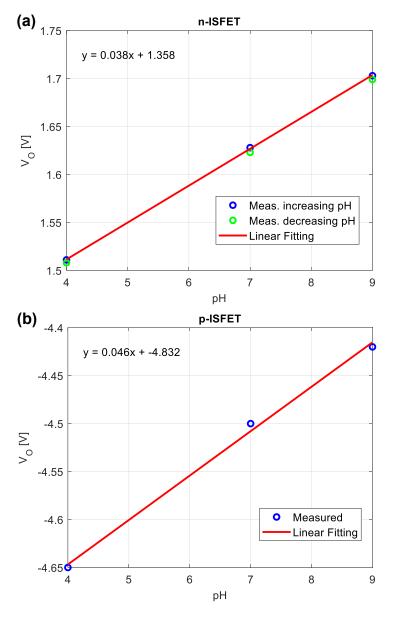

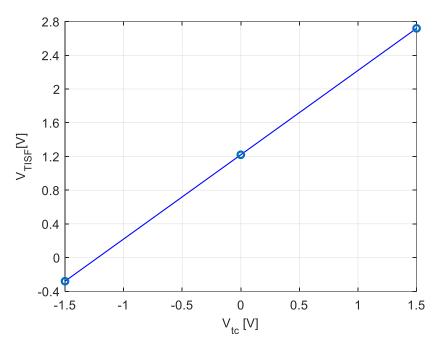

|         | Figure 36 - pH sensitivity at 650 $\mu$ L: (a) n-ISFET 09 from chip 08 (21/09/20                                 | 20), (b)              |

| p-ISFE  | T 15 from chip 14 (24/09/2020)                                                                                   | 93                    |

|         | Figure 37 - ISFET sensitivity to pH, 22/09/2020, at 50 μL (n-ISFET 09 from                                       | om chip               |

| 08)     |                                                                                                                  | 94                    |

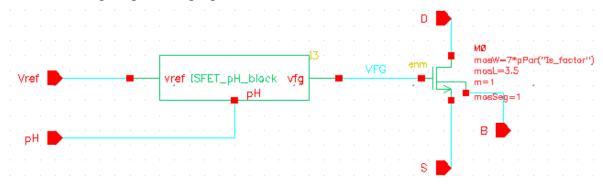

|         | Figure 38 – n-ISFET model symbol.                                                                                | 107                   |

|         | Figure 39 - ISFET model schematic on Virtuoso.                                                                   | 107                   |

|         | Figure 40 - Verilog-A code of the wet interface block.                                                           | 108                   |

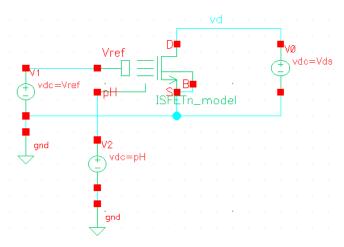

|         | Figure 41 - Testbench schematic applied to the n-ISFET for the                                                   | $g_m/I_D$             |

| charact | erization                                                                                                        | 111                   |

|         | Figure 42 – DC simulation: n-ISFET @ pH = pH <sub>pzc</sub> vs n-MOSFET                                          | 112                   |

|         | Figure 43 – n-ISFET simulation results of $g_m/I_D$ vs $V_{REF}$ and $I_D$ vs $V_{REF}$ for pH                   | from 1                |

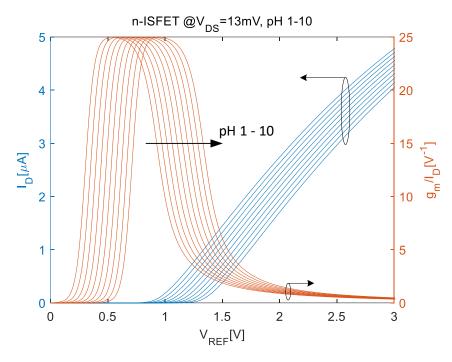

| to 10   |                                                                                                                  | 113                   |

|         | Figure 44 – n-ISFET simulation: (a): $V_{TISF}$ vs pH, and (b) $V_{FG}$ vs $V_{REF}$ @pH =                       | = pH <sub>pzc</sub> . |

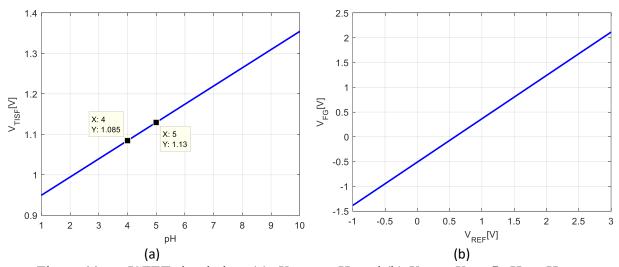

|         |                                                                                                                  | 113                   |

|         | Figure 45 - ISFET $g_m/I_D$ vs $V_{REF}$ and $I_D$ vs $V_{REF}$ for different $V_{tc}$ @pH = pH <sub>pzc</sub> . | 114                   |

|         | Figure 46 - ISFET threshold voltage for different $V_{tc}$ @pH = pH <sub>pzc</sub>                               | 115                   |

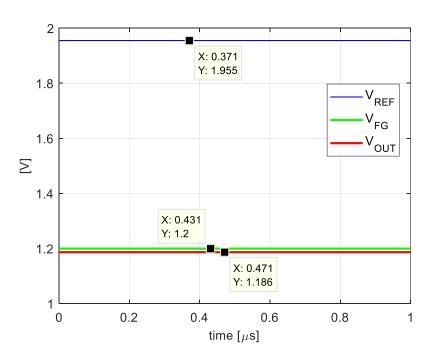

|         | Figure 47 – ISFET floating gate readout.                                                                         | 116                   |

|         | Figure 48 - ISFET floating gate readout simulation                                                               | 116                   |

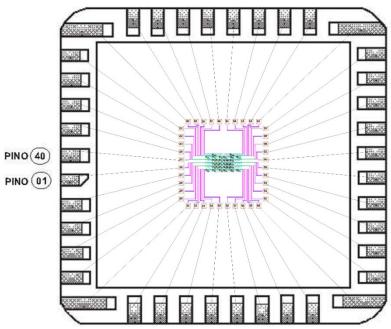

|         | Figure 49 - Die of the chip Onsemi.                                                                              | 121                   |

|         | Figure 50 - A chip before and another chip after the mask application                                            | 123                   |

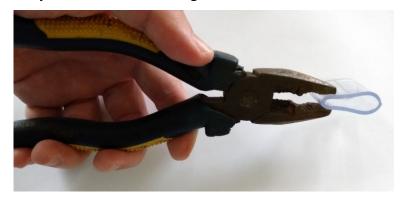

|         | Figure 51 - (a) Sputtering process. (b) Details of the chip on the chamber                                       | 124                   |

|         | Figure 52 - Chip (a) before and (b) after the removing of the mask                                               | 125                   |

|         | Figure 53 - Connector placed for conductive paste application.                                                   | 126                   |

|         | Figure 54 - Silver paste application.                                                                            | 126                   |

|         | Figure 55 - Chip final assembly after metallization.                                                             | 126                   |

|         | Figure 56 - Readout circuit for n-ISFET.                                                                         | 131                   |

|         | Figure 57 – LTSPICE simulation: (a) circuit schematic, and (b) result                                            | 133                   |

|         | Figure 58 - Chip schematic.                                                                                      | 134                   |

|         | Figure 59 - Circuit schematic in the Proteus software.                                                           | 134                   |

|         | Figure 60 - PCB project (a), (b), (c) and implementation (d), (e) and (f)                                        | 135                   |

|         | Figure 61 - Chip with the home-made chamber: (a) top view, and (b) chamber f | illed |

|---------|------------------------------------------------------------------------------|-------|

| with wa | nter                                                                         | 136   |

|         | Figure 62 - Cutting the chamber.                                             | .137  |

|         | Figure 63 - Reshaping the chamber to an elliptical format.                   | .137  |

|         | Figure 64 - Applying glue to the chamber.                                    | .137  |

|         | Figure 65 - Chamber glued to the chip.                                       | .138  |

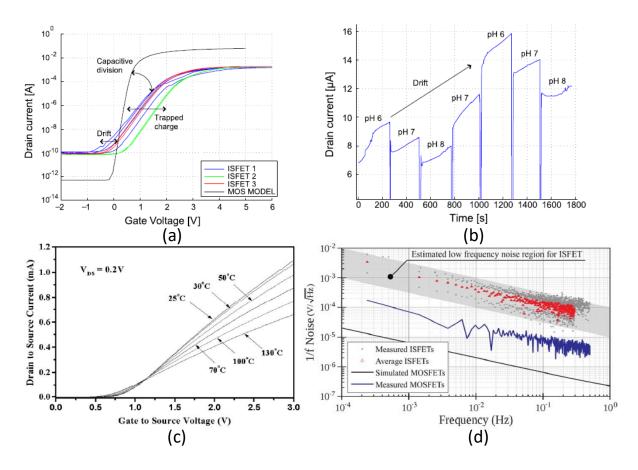

|         | Figure 66 - (a) Close view of a chip filled with water. (b) Two chips filled | with  |

| water   |                                                                              | .138  |

|         | Figure 67 - Sealing test in two chips: 07/09/2020 at (a) 10:22; (b) 16:47    | .139  |

|         |                                                                              |       |

# LIST OF TABLES

| Table 1 - Compensation techniqu      | es for ISFETs in commercial technologies (adapted           |

|--------------------------------------|-------------------------------------------------------------|

| from [10])                           | 38                                                          |

| Table 2 - Electrochemical and MO     | OS parameter values56                                       |

| Table 3 - ISFET threshold voltage    | e expressions presented in different papers57               |

| Table 4 - Chip SilTerra: fabrication | on schedule61                                               |

| Table 5 - Chip Onsemi: simulated     | electrical characteristics (typical conditions)63           |

| Table 6 - Deposition parameters f    | or Au66                                                     |

| Table 7 - Mean and standard devi     | ation of the measured MOSFETs parameters83                  |

| Table 8 - Estimation of the of       | ffset in threshold voltage due trapped charge at            |

| passivation.                         | 87                                                          |

| Table 9 - ISFET threshold volta      | ge dispersion compared with previously published            |

| values                               | 88                                                          |

| Table 10 - Mean measured and the     | eoretical slope factors and $(g_m/I_D)_{max}$ for ISFETs of |

| the 3 × 3 central array in four dies | 89                                                          |

| Table 11 – Mean measured and t       | heoretical specific currents for ISFETs of the $3 \times 3$ |

| central array in four dies           | 89                                                          |

| Table 12 - User defined parameter    | rs of the ISFET DC model on Virtuoso108                     |

| Table 13 - MOSFET vs ISFET sin       | mulated parameters using $g_m/I_D$ extraction112            |

| Table 14 – X-ray images of chips     | with epoxy chamber118                                       |

| Table 15 – PADs connectivity of      | the Chip ONSEMI122                                          |

| Table 16 - Deposition parameters     | for Au                                                      |

| Table 17 – CHIP11: ISFETs dry o      | characterization using the method $g_m/I_D$ (08/11/2019)    |

| at room temperature).                | 127                                                         |

| Table 18 - Samples mean and star     | ndard deviation                                             |

| Table 19 – CHIP05: ISFETs dry o      | characterization using the method $g_m/I_D$ (08/11/2019)    |

| at room temperature).                | 128                                                         |

| Table 20 - Samples mean and star     | ndard deviation                                             |

| Table 21 – CHIP03: ISFETs dry o      | characterization using the method $g_m/I_D$ (11/12/2019)    |

| at room temperature).                | 129                                                         |

| Table 22 - Samples mean and star     | ndard deviation 129                                         |

| Table 23 – CHIP16: ISFETs dry characterization using the method $g_m/I_D$ (30/01/2020 |

|---------------------------------------------------------------------------------------|

| room temperature)                                                                     |

| Table 24 - Samples mean and standard deviation                                        |

| Table 25 – Discrete readout circuit components values                                 |

#### **ABBREVIATIONS**

ACM - Advanced Compact MOSFET

BSIM - Berkeley Short-Channel Insulated gate field-effect transistor Model

CDS - Correlated double sampling

CMOS – Complementary Metal Oxide Semiconductor

CVCC - Constant-Voltage, Constant-Current

DIL - Dual in line

DNA – deoxyribonucleic acid

FPN - Fixed-pattern noise

GCS - Gouy-Chapman-Stern

HV - High Voltage

ISFET - Ion Sensitive Field Effect Transistor

IUPAC - International Union of Pure and Applied Chemistry

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

n-ISFET – n-channel ISFET

n-MOSFET – n-channel MOSFET

OHP - Outer Helmholtz plane

PCB - Printed circuit board

PCR - Polymerase chain reaction

PDK - Process design kit

pH - Concentration of hydrogen ions in a substance

$pH_{\text{pzc}}$  - pH at which the oxide surface is electrically neutral (point of zero charge)

p-ISFET – p-channel ISFET

p-MOSFET – p-channel MOSFET

qRE - Quasi Reference Electrode

REFET - Reference FET

RNA - Ribonucleic acid

SHE – Standard Hydrogen Electrode

SPICE - Simulation Program with Integrated Circuits Emphasis

TSMC - Taiwan Semiconductor Manufacturing Company

UICM - Unified current-control model

USG - Undoped Silicate Glass

# **SYMBOLS**

| $A_{mos}$ - Gate area                                                   |

|-------------------------------------------------------------------------|

| $A_{pass}$ - Top metal area                                             |

| C - Electrolyte concentration in mol/m³                                 |

| $C'_{eq}$ – Series equivalent of $C'_{G}$ and $C'_{H}$                  |

| $C'_G$ – Gouy-Chapman capacitance per unit area                         |

| C' <sub>H</sub> – Helmholtz capacitance per unit area                   |

| C'ox - Oxide capacitance per unit area                                  |

| $C_b$ - Depletion capacitance                                           |

| $C_d$ – Differential capacitance                                        |

| $C_{eff}$ - Equivalent series capacitance of $C_{ox}$ and $C_{pass}$ :  |

| $C_{ox}$ – Oxide capacitance                                            |

| $C_{pass}$ – Passivation capacitance                                    |

| $C_{SiN}$ – Si <sub>3</sub> N <sub>4</sub> layer capacitance            |

| C <sub>USG</sub> –USG layer capacitance                                 |

| $E_{ref}$ – Absolute electrode potential                                |

| $g_m$ – Transconductance                                                |

| $H_b$ - Ion concentration in the solution                               |

| $H_s$ - Proton concentration in the insulator surface                   |

| $I_D$ – Drain current                                                   |

| <i>i<sub>f</sub></i> – Forward inversion level                          |

| $i_r$ – Reverse inversion level                                         |

| $I_S$ – Specific (normalization) current of the MOSFET                  |

| $I_{SISF}$ – Specific current of the ISFET in contact with electrolytes |

| $I_{SISF\_met}$ – Specific current of the metal-gate ISFET              |

| $K_{-}$ - Negative dissociation constant of the passivation             |

| k -Boltzmann constant                                                   |

$K_+$  - Positive dissociation constant of the passivation

$n^{\theta}$  - Concentration of ions in the bulk solution

L - Transistor length

$K_n$  - Amine sites dissociation constants of the passivation layer

Na - Avogadro's constant

$n_{ISF}$  – Slope factor of the ISFET in contact with electrolytes

$n_{ISF\ met}$  – Slope factor of the metal-gate ISFET

$n_{mos}$  – MOSFET slope factor

$N_{nit}$  - Primary amine sites per area

N<sub>sil</sub> - Number of silanol (SiH<sub>3</sub>OH) sites per area

q – Electron charge

$Q_b$  - Charge trapped at the silicon

$Q_{ox}$  – Charge at the interface oxide/semiconductor

$Q_{pass}$  – Charge at the passivation layer

T – Absolute temperature

$t_{ox}$  – Gate oxide thickness

*t*<sub>pass</sub> - Passivation thickness

$V_{BIAS}$  – Bias voltage

$V_{chem}$  – Potentials due to electrochemical contributions

$V_D$  – Drain voltage

$V_{DD}$  – Positive supply voltage

$V_{DS}$  – Drain-source voltage

$V_{DSsat}$  - Saturation voltage between drain and source terminals

$V_{FB,ISF}$  – ISFET flat-band voltage

$V_{GB}$  – Gate-Bulk voltage

$V_{GS}$  – Gate-source voltage

$V_O$  – Output voltage

$V_P$  – Pinch-off voltage

$V_{REF}$  - Reference electrode voltage

$V_S$  – Source voltage

$V_{SS}$  – Negative supply voltage

$V_{tc}$  - Offset in threshold voltage due to trapped charges

$V_{TISF}$  – Threshold voltage of the ISFET in contact with electrolytes

*V*<sub>TISF met</sub> – Threshold voltage of the metal-gate ISFET

$V_{Tmos}$  – MOSFET threshold voltage

W – Transistor width

$x_2$  - OHP distance from electrode

$X_{sol}$  - Potential due to dipoles in the insulator interface

z - Magnitude of the ionic charge

$\alpha$  – ISFETs sensitivity parameter

$\alpha_{att}$  – Capacitive attenuation constant

$\beta_{int}$  – Intrinsic buffer capacity

γ - MOSFET body-effect factor

$\gamma_{chem}$  – Sum of electrochemical potentials

$\varepsilon_0$  - Permittivity of free space

$\varepsilon_r$  - Relative dielectric constant of the medium

$\varepsilon_{rox}$  - Relative dielectric constant of the gate oxide

$\varepsilon_{rpass}$  - Relative dielectric constant of the passivation

$\varepsilon_s$  – Permittivity of silicon

$\kappa_T$  – Technological depended constant of ISFET threshold voltage

$\mu$  - Carrier mobility

$\rho$  – Charge density

$\sigma_d$  - Charge density at the diffuse layer

$\sigma_{mos}$  – Charge density at the semiconductor

$\sigma_o$  - Charge density at electrolyte/insulator interface

$\phi_2$  - Potential in the OHP

$\phi_{Au}$  - Work function per electron charge of gold

$\phi_{eo}$  - Electrolyte/insulator interface potential

$\phi_{f}$  Fermi potential

$\phi_{lj}$  - Liquid junction potential between electrode and solution

$\phi_{met}$  - Work function per electron charge of aluminum

$\phi_{poly}$  - Work function per electron charge of the polysilicon gate

$\phi_s$  – Semiconductor surface potential

$\phi_{sc}$  - Work function per electron charge of the semiconductor

$\phi_t$  – Thermal voltage

# **CONTENTS**

| 1       | INTRODUCTION                       | 25 |

|---------|------------------------------------|----|

| 1.1     | THESIS OBJECTIVES                  | 27 |

| 1.1.1   | General Objectives                 | 27 |

| 1.1.2   | Specific Objectives                | 28 |

| 1.2     | THESIS STRUCTURE                   | 28 |

| 2       | LITERATURE REVIEW                  | 29 |

| 2.1     | ISFET NONIDIEALITIES               | 29 |

| 2.1.1   | Trapped charges                    | 29 |

| 2.1.2   | Temporal Drift                     | 29 |

| 2.1.3   | Capacitive attenuation             | 30 |

| 2.1.4   | Temperature effects                | 30 |

| 2.1.5   | Noise                              | 30 |

| 2.2     | ISFETS READOUT                     | 31 |

| 2.2.1   | Reference electrode                | 32 |

| 2.2.1.1 | Ag/AgCl electrode                  | 32 |

| 2.2.1.2 | Quasi-reference electrodes         | 33 |

| 2.2.2   | Single-ended readout               | 34 |

| 2.2.2.1 | Source follower                    | 34 |

| 2.2.2.2 | Source and drain follower          | 34 |

| 2.2.2.3 | Current mode                       | 35 |

| 2.2.2.4 | Other techniques                   | 35 |

| 2.2.3   | Differential readout               | 36 |

| 2.2.3.1 | ISFET-REFET pair                   | 36 |

| 2.2.3.2 | ISFET-ISFET Chemical Gilbert Cell  | 37 |

| 2.3     | SUMMARY OF COMPENSATION TECHNIQUES | 37 |

| 3       | ISFET MODELLING                                           | 41 |

|---------|-----------------------------------------------------------|----|

| 3.1     | CURRENT-VOLTAGE RELATIONSHIP IN THE ISFET TERMINALS       | 41 |

| 3.2     | THRESHOLD VOLTAGE                                         | 42 |

| 3.2.1   | The ISFET Flat-Band Voltage                               | 43 |

| 3.2.1.1 | The electrolyte/insulator interface potential $\phi_{eo}$ | 44 |

| 3.2.1.2 | A simplified expression for $\phi_{eo}$                   | 47 |

| 3.2.1.3 | Estimation of the pH sensitivity at $pH = pH_{pzc}$       | 49 |

| 3.2.2   | The ISFET threshold voltage formulation                   | 50 |

| 3.3     | SLOPE FACTOR                                              | 52 |

| 3.4     | SPECIFIC CURRENT                                          | 54 |

| 3.5     | ISFET MODEL IN VIRTUOSO                                   | 55 |

| 4       | THE DESIGNED CHIPS                                        | 58 |

| 4.1     | DESIGN-TO-SILICON FLOW                                    | 58 |

| 4.2     | CHIP SILTERRA                                             | 59 |

| 4.2.1   | Chip Design                                               | 59 |

| 4.2.2   | Chip Packaging                                            | 60 |

| 4.3     | CHIP ONSEMI                                               | 61 |

| 4.3.1   | Chip Design                                               | 61 |

| 4.3.2   | Chip Packaging                                            | 63 |

| 5       | A DRY TEST FOR ISFETS                                     | 65 |

| 5.1     | METAL LAYER DEPOSITION                                    | 65 |

| 5.2     | MODELLING OF METALLIZED ISFETS                            | 66 |

| 5.2.1   | Threshold voltage                                         | 67 |

| 5.2.2   | Slope factor                                              | 69 |

| 5.2.3   | Specific current                                          | 70 |

| 6       | A DIFFERENTIAL/SINGLE-ENDED READOUT CIRCUIT               | 71 |

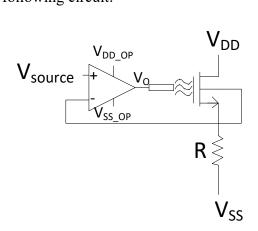

| 6.1     | DIFFERENTIAL CIRCUIT                                      | 72 |

| 6.1.1   | DC analysis                                               | 73 |

|         |                                                           |    |

| 6.1.2   | Simulations                                                  | 76  |

|---------|--------------------------------------------------------------|-----|

| 6.1.2.1 | pH variations in the reaction chamber                        | 76  |

| 6.1.2.2 | Both ISFETs with same V <sub>tc</sub>                        | 77  |

| 6.1.2.3 | ISFETs with different $V_{tc}$                               | 78  |

| 6.1.2.4 | Common-mode voltage variation                                | 79  |

| 6.2     | SINGLE-ENDED CONFIGURATION                                   | 80  |

| 6.2.1   | DC analysis                                                  | 81  |

| 6.2.2   | Simulations                                                  | 81  |

| 7       | EXPERIMENTAL RESULTS                                         | 83  |

| 7.1     | CHIP SILTERRA                                                | 83  |

| 7.1.1   | MOSFETs Measurements                                         | 83  |

| 7.1.2   | ISFETs Dry Characterization                                  | 83  |

| 7.1.3   | ISFETs Wet Tests                                             | 90  |

| 7.1.3.1 | Wet Test Procedure                                           | 90  |

| 7.1.3.2 | Wet Test Results                                             | 93  |

| 8       | CONCLUSIONS                                                  | 96  |

| 8.1     | SUMMARY OF THE THESIS                                        | 96  |

| 8.2     | MAIN CHALLENGES                                              | 96  |

| 8.3     | FUTURE WORK                                                  | 97  |

| 8.4     | PUBLICATIONS                                                 | 98  |

|         | REFERENCES                                                   | 99  |

|         | APPENDIX A – MATLAB algorithms                               | 105 |

|         | APPENDIX B - ISFET DC model implemented on Virtuoso          | 107 |

|         | APPENDIX C - Chip Silterra: pin mapping                      | 117 |

|         | APPENDIX D - Chip Silterra: x-ray verification               | 118 |

|         | APPENDIX E - Chip Onsemi: PADs connectivity                  | 121 |

|         | APPENDIX F - Gold metallization with sputtering for dry test | 123 |

| APPENDIX G - Chip SilTerra: results of the dry parameters extraction127 |

|-------------------------------------------------------------------------|

| APPENDIX H - Discrete readout circuit project for wet tests131          |

| APPENDIX I - Homemade chamber implementing a PVC tubing                 |

#### 1 INTRODUCTION

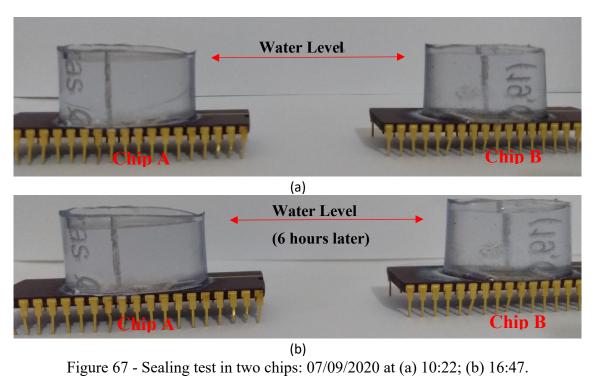

The ion-sensitive field-effect transistor (ISFET) is a microsensor based on the metal oxide semiconductor field-effect transistor (MOSFET) capable of measuring the ionic concentration of a solution, such as pH. The ISFET has been used in different fields, including food analysis [1], ion imaging [2], detection of bacteria [3] and viruses [4], DNA sequencing [5] and early detection of DNA methylation for cancer screening [6]. As Figure 1 shows, an ISFET-based handheld device for detection of infectious diseases (called Lacewing [13]) can be portable and cheap as an antigen test and precise as a PCR instrument.

Figure 1 – Comparation of an ISFET-based handheld device, antigen tests and PCR instruments for detection of infectious diseases [13].

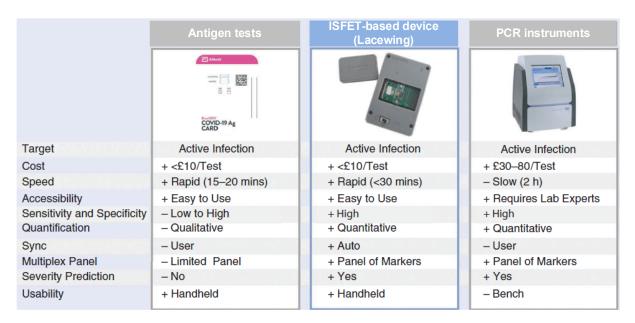

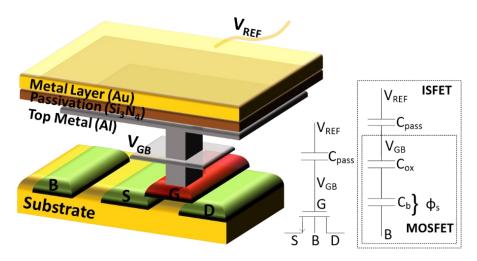

In 1970, Bergveld introduced the basic idea behind ISFET [7]. During the early years of research, additional fabrication steps were required to convert the MOSFETs into ionsensitive sensors. In 1999, almost three decades after the advent of ISFETs, Bausells proposed a technique to implement ISFETs in standard complementary metal-oxide semiconductor (CMOS) technology, without additional fabrication steps [8]. The extended-gate technique is used to connect the transistor gate to the top metal, which is in contact with the passivation layer, usually Si<sub>3</sub>N<sub>4</sub>, as shown in Figure 2a. The extended-gate technique eliminated the post-processing steps required in the early fabrication methods, reduced fabrication costs and time, and expanded the sensor application to lab-on-chip platforms, allowing the integration of

high-density arrays with more than 1000 sensors per chip [14], with small dimensions, mass production at low cost, and the coexistence of the sensor, readout, and bias circuitry on the same chip.

Figure 2 – (a) Illustration of the ISFET cross-section in standard CMOS technology. (b) Simplified ISFET capacitive model (adapted from [15]). (c) The ISFET symbol (B, S, D), and G are the bulk, source, drain and floating gate terminals, respectively.).

In the extended-gate technique, the floating-gate terminal is covered with a passivation layer, which is in contact with a solution polarized by a reference electrode (usually Ag/AgCl). Consequently, the ISFET threshold voltage changes according to the ion concentration of the solution. Theoretically, a maximum sensitivity of  $2.3\phi_t$  (59 mV/pH at 25°C) is expected [16], where  $\phi_t$  is the thermal voltage. The sensitivity depends on the material used as the sensing membrane. Practical results are lower than this value, mainly because of imperfections in the material used as the sensing membrane [1]. The deposition of selective polymer membranes above the passivation layer allows the detection of different ionic species, such as sodium and potassium, rather than pH [17].

Despite the increasing use of ISFETs in different areas and the benefits of using a standard CMOS process, the implementation of these sensors presents some non-ideal behavior. Some nonidealities have unpredictable values, such as trapped charge offsets, and need to be better understood and characterized.

This PhD thesis focuses on the design, modelling, and measurement techniques of ISFETs in commercial CMOS technologies. This work addresses some of the ISFET non-ideality challenges by proposing a dry test in which a thin metal film replaces the solution and

reference electrode. The dry test allows measurement of electrical parameters, such as threshold voltage, capacitive attenuation, and estimation of trapped charges, without electrochemical influences. This test is supposed to be a complementary tool for ISFET analysis, given that the conventional wet test is still required for full sensor characterization. For better device design and analysis of measurements, this research proposes a model for ISFETs in contact with electrolytes and with a metal layer, presenting mathematical expressions for the main electrical parameters. A circuit topology aimed at single-ended and differential measurements is also presented.

#### 1.1 THESIS OBJECTIVES

# 1.1.1 General Objectives

ISFETs are commonly characterized by a wet setup, using solutions (usually with pH 7) and a reference electrode (usually Ag/AgCl), whose chemical characteristics affect measurements. In addition to ion sensitivity, other important ISFET parameters must be characterized for an appropriate design, such as the slope factor, threshold voltage dispersion, capacitive attenuation, and specific current. However, some of the above-mentioned parameter's values are difficult to predict, such as the threshold voltage, which is affected by fluctuations of trapped charges in the passivation layer.

Therefore, to characterize the electrical parameters of ISFETs without electrochemical interaction, this thesis proposes a dry test in which a metal film replaces the reference electrode and solution. The proposed dry test removes some deleterious effects from measurements, such as the leakage current of the reference electrode, which affects the output temporal drift [9] and the passivation degradation due to the long-term contact with the solution [10]. The dry test is supposed to be a complementary tool to the wet test for ISFET analysis and characterization.

This thesis analysis the ISFET structure in contact with electrolytes and with a metal layer and proposes a physical model for both wet and dry conditions. The physical model is used together with the measured results for the analysis of the sensors designed in this thesis and fabricated using a commercial CMOS technology.

A CMOS test chip optimized for differential measurements is proposed, considering the benefits of this type of measurement, such as the reduction of common-mode effects and the possibility of using compact quasi-reference electrodes for portable applications. This thesis also proposes a circuit topology that allows for both single-ended and differential measurements.

# 1.1.2 Specific Objectives

The specific objectives of this thesis are:

- 1. Propose a dry test for the measurement of the electrical parameters of ISFETs without electrochemical effects from conventional wet measurements.

- 2. Characterize ISFETs implemented in standard CMOS technology through a conventional wet test and the proposed dry test.

- 3. Model the main ISFET electrical parameters for wet and dry tests.

- 4. Design a chip optimized for differential measurements and suitable for the implementation of two chambers on the chip.

- 5. Propose a topology for a readout circuit capable of addressing the main ISFET nonidealities.

#### 1.2 THESIS STRUCTURE

The remainder of this paper is organized as follows: Section 2 presents a literature review. In Section 3, an ISFETs model for the conventional wet test is presented. Section 4 presents details of the designed chips. The methodology and modelling of the dry test are presented in Section 5. A readout topology that allows for both differential and single-ended measurements is proposed in Section 6. The measurement results are presented in Section 7, and the conclusions and future work are presented in Section 8. Complementary materials are presented in the appendices.

#### 2 LITERATURE REVIEW

This chapter summarizes the main nonidealities of ISFETs fabricated using standard CMOS technology and presents some techniques to reduce the effects of these nonidealities and some readout circuit architectures.

#### 2.1 ISFET NONIDIEALITIES

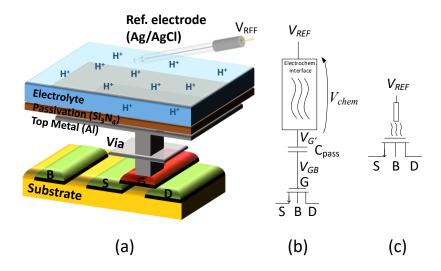

# 2.1.1 Trapped charges

Charges are trapped in the floating gate and passivation layer of the ISFET owing to the fabrication process. These charges induce random offsets in the threshold voltage, causing large mismatches between the devices (Figure 3a). For example, threshold voltages ranging from -14 V to +8 V have been reported for ISFETs implemented using 0.35 µm CMOS technology [18]. The removal of the top layers from the passivation showed that charges are trapped mainly at the interface of the layers [19].

To reduce the effects of trapped charges, different techniques have been proposed: exposure of the sensor to ultraviolet (UV) radiation for a prolonged time to remove trapped charges [20], hot-electron injection using a high source-drain voltage [21], and electron tunneling through a high voltage coupled to the floating gate by a capacitor [22]. In addition, linear and interdigitated structures present different threshold voltages [8].

# 2.1.2 Temporal Drift

The threshold voltage of ISFETs suffers from a temporal drift that is influenced by different factors, including the electrolyte pH, sensitive membrane material, device dimensions, and leakage in the reference electrode [10], [9]. This effect is illustrated in Figure 3b and is more relevant for long-term measurements. Drifts between 1.5 and 8.5 mV/h have been reported [18]. To reduce the drift effects, differential sensing between an ISFET and a non-pH-sensitive FET (REFET), an ISFET/ISFET pair, or ISFET/MOSFET can be used [23], [24], [25]. Software processing that implements a mathematical model to reduce its effects on data processing was also used [26].

### 2.1.3 Capacitive attenuation

Using standard CMOS technology, the ISFET floating gate voltage, which corresponds to the MOSFET gate voltage ( $V_{GB}$ ), is attenuated with respect to the reference electrode ( $V_{REF}$ ) as shown in Figure 3a, owing to the capacitive division formed by the passivation layers (usually Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>) and MOSFET capacitances. This can be concluded from eq. (1) [10]:

$$V_{GB} = V_{G'} \frac{C_{pass}}{C_{pass} + (C_{ox}C_b)/(C_{ox} + C_b)} = \alpha_{att}V_{G'}$$

(1)

where  $V_{G'}$  corresponds to  $V_{REF} - V_{chem}$  in Figure 2b,  $C_{b}$ ,  $C_{pass}$ ,  $C_{ox}$  are the depletion, passivation, and gate oxide capacitances, respectively, and  $\alpha_{att}$  is the capacitive attenuation constant. A complete analysis of the ISFET structure is presented in this thesis.

Capacitor mismatches cause variations in the attenuation factor of ISFETs in an array, affecting, for example, the gain of the sensors [27]. The passivation layer can be modified to reduce the attenuation factor and/or the mismatch. For example, Xu *et al.* [28] exposed the top metal layer of an ISFET letting a natural Al<sub>2</sub>O<sub>3</sub> oxidation layer with a thickness of 5 nm grow. Architectures that automatically compensate for the gain of each sensor [27] or are more robust to the attenuation factor [29] are also used.

#### 2.1.4 Temperature effects

The effects of temperature in ISFETs are comparable to those in MOSFETs, but with the additional influence of the electrolyte, reference electrode, and sensitivity membrane. This nonideality is shown in Figure 3c. The influence of temperature is comparable with a variation of 1 pH for each 7 K variation at room temperature [10]. These effects can be reduced by using differential measurements.

#### 2.1.5 Noise

This nonideality reduces sensor resolution. ISFETs present both chemical and MOSFET noise (Figure 3d) [18]. The excess 1/f noise can be reduced by averaging sensors in an array [30], [31].

Figure 3 - Main ISFET nonidealities: (a) trapped charges offset and capacitive attenuation, (b) temporal drift, (c) temperature effect, and (d) noise [10], [18].

#### 2.2 ISFETS READOUT

The ISFET readout circuit provides appropriate voltages and/or currents to ensure that the sensor works with optimized electrical characteristics (such as low power consumption), resulting in an electrical output that varies with the pH (such as voltage, current, and frequency of a signal). The readout circuit can be implemented using discrete components (off-chip) or can be integrated into the same chip as the sensor, resulting in a more compact and usually low-power device. The readout can also be performed using a single-ended method, in which a single sensor is used, or a differential method, in which two sensors, or a combination of a sensor with other device, are used to reduce common-mode signals (reducing effects of temperature and temporal output drift [10]).

The readout circuit must address the nonidealities of the sensor and be optimized for the intended application. For example, for long-term tests (of the order of tens of minutes [4], [32]), the temporal drift of the ISFET output voltage may be critical. There are also highfrequency applications, such as the use of ISFETs as ion image sensors, with sample rates higher than thousand frames per second [33], in which the readout circuit must work at the desired sample rate. Simple and small-area readout circuits may be preferred for dense arrays composed of thousands of ISFETs [10]. Detection of small pH variations (such as 0.045 pH caused by Escherichia coli bacteria in food safety screening [34]) requires a low-noise implementation. The readout circuit must also address large variations in the threshold voltage between sensors in the same or different dies caused by trapped charges.

Therefore, readout circuits for ISFETs implement different topologies. The following sections will present more details about the reference electrode, an important component in the readout of ISFETs, and some of the integrated circuit topologies used in the literature for both single and differential measurements.

#### 2.2.1 Reference electrode

The reference electrode polarizes the solution in contact with the ISFET. Therefore, this element affects the performance of the ISFET, influencing linearity, sensitivity, and noise [35].

For an ideal electrode, the voltage between the electrode and solution does not vary with the solution composition, owing to the electrochemical equilibrium maintained with the solution [36]. Other desirable characteristics of an ideal electrode are reproducibility, chemical and thermodynamic reversibility, low-temperature coefficient, low hysteresis, and easy preparation and handling [37]. Electrodes made of silver-silver chloride (Ag/AgCl) and calomel (Hg<sub>2</sub>Cl<sub>2</sub>) are commonly used [38].

# 2.2.1.1 Ag/AgCl electrode

Many ISFET applications use an Ag/AgCl reference electrode. This electrode is composed of an Ag wire covered with AgCl immersed in a saturated inner filling solution containing Cl<sup>-</sup> (such as KCl) inside a glass tube with a porous membrane separating it from the test solution [35], as illustrated in Figure 4.

The potential of the Ag/AgCl electrode, relative to the standard hydrogen electrode (SHE), is 0.19 V [5]. At 25°C, the absolute potential of SHE is  $(4.44 \pm 0.02)$  V [39].

Figure 4 - Ag/AgCl reference electrode [40].

Despite its good electrochemical characteristics, due to its large dimensions, the standard Ag/AgCl electrode is difficult to implement in small volumes, on the order of tens of microliters, or in portable devices. For example, common commercial electrode models have tip diameters of 12 mm and lengths greater than 10 cm [41]. This diameter is close to the cavity width of the chip package used in this study, resulting in a tight fit. As a result, an appropriate standard electrode model must be selected based on the chip chamber dimensions and sample volume, for example.

Smaller alternatives to the standard Ag/AgCl electrode include microfabricated reference electrodes, which have complex construction and a short lifetime [35]. Another option is to use a quasi-reference electrode (qRE).

#### 2.2.1.2 Quasi-reference electrodes

Quasi-reference electrodes are composed of a metal pad or wire in direct contact with the test solution. Figure 5 shows an example of an on-chip Au qRE implemented in a TSCM 0.35 µm technology post-processed with gold [42].

Despite its simplicity and compactness, qRE does not provide a stable potential, presenting variations in the electrode/solution potential according to the solution composition. Therefore, qRE is usually implemented in differential measurements [36], [43]. For example, Scaff [37] compared the pH response of ISFETs using an Ag/AgCl standard electrode and quasi-reference electrodes composed of Pt, Ag, and Au wires. According to measurements, the Au qRE presented the most linear response among the tested quasi-reference electrodes (close to Ag/AgCl linearity), but resulted in a lower pH sensitivity (approximately 34 mV/pH) than the standard Ag/AgCl electrode (approximately 50 mV/pH) [37].

Figure 5 - A built-in Au qRE [42].

# 2.2.2 Single-ended readout

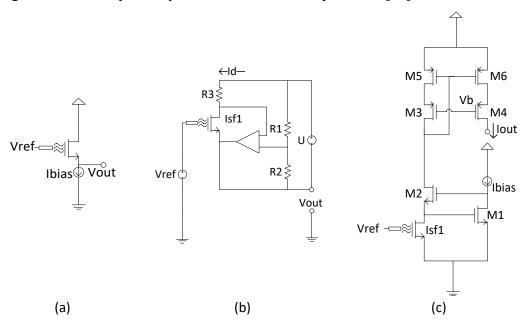

# 2.2.2.1 Source follower

The source follower is a commonly used technique (Figure 6a), in which the source voltage is read while the drain current ( $I_D$ ) and other terminal potentials are kept constant, resulting in changes in the source voltage according to threshold voltage variations with pH [33], [44], [45], [46]. Despite its simplicity, which is suitable for large arrays, the device can alternate between saturation and linear operation because the drain-source voltage ( $V_{DS}$ ) is not constant [47].

#### 2.2.2.2 Source and drain follower

Other technique used is the source and drain follower, also known as *Constant-Voltage and Constant-Current* (CVCC) (Figure 6b) [20, 33, 48]. In this case, the ISFET is polarized with a constant  $I_D$  and constant  $V_{DS}$ , so the device does not change the region of operation. The changes in the pH can be read in the source voltage.

#### 2.2.2.3 Current mode

In the current-mode readout, the ISFET drain current  $I_D$  is read while the terminals have a constant voltage (Figure 6c). Thus, pH variations are translated into variations in the current  $I_D$ . This method benefits from the easier operations in current than in voltage, such as averaging and better compatibility with weak inversion operations [10].

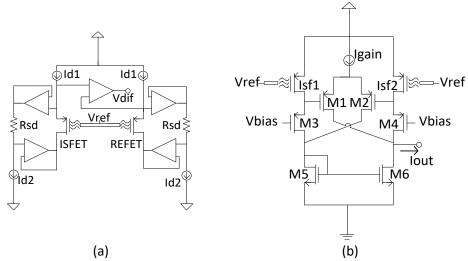

Figure 6 – Single-ended readout circuits: (a) source follower [44], (b) CVCC [1], and (c) current mode [30].

# 2.2.2.4 Other techniques

Other readout techniques are being developed based on the circuits mentioned in previous sections. For example, there is an active pixel sensor (APS) that originates from image sensors and topologies that convert pH to other domains, such as time or frequency (in order to increase the signal-to-noise ratio) [10]. It is important to mention the benefits of polarizing ISFETs near the threshold or subthreshold voltage, given that in this case, the  $g_m/I_D$  ratio is increased and the capacitance due to inverted channel charges is reduced [28].

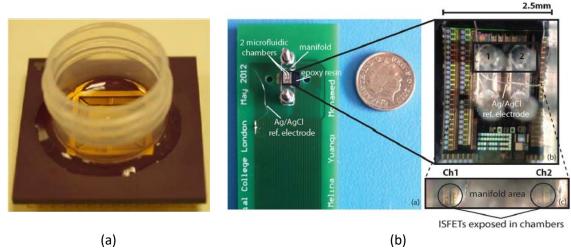

#### 2.2.3 Differential readout

As mentioned previously, differential measurements can compensate for several nonidealities, such as temperature effects and temporal drift, and allow the use of quasi-reference electrodes. This method can be applied between an ISFET and a non-pH-sensitive FET (called REFET), or an ISFET/ISFET pair, or ISFET/MOSFET [23], [24], [25]. Despite the benefits, differential sensing implementing two ISFETs requires two chambers (one chamber for each ISFET), which are more difficult to implement than the one chamber used in single-ended measurements (Figure 7). When two chambers are used, each ISFET measures different solutions: one is the reference solution (usually pH 7), and the other is the solution in which the pH must be monitored. Another challenge with differential measurements is threshold voltage mismatch between devices [10].

Figure 7 - Example of chambers for (a) single-ended [31], and (b) differential measurements [23].

# 2.2.3.1 ISFET-REFET pair

Milgrew *et al.* [49] implemented a pair of ISFET/REFET polarized with a quasireference electrode (Figure 8a). The output is the difference between the drain voltages of the devices as obtained using an instrumentation amplifier.

#### 2.2.3.2 ISFET-ISFET Chemical Gilbert Cell

Figure 8b shows a circuit that operates under differential currents. In this case, an ISFET/ISFET pair was implemented in a Gilbert cell, in which the output current is the difference between the drain current of each ISFET [23].

Figure 8 - Differential measurements: (a) voltage [49], and (b) current mode [23].

### 2.3 SUMMARY OF COMPENSATION TECHNIQUES

The techniques applied to overcome ISFET nonidealities can be distinguished into two categories: sensor/device adaptation, in which compensation methods are applied to the sensor, and system-level compensation, in which the output signal is processed to compensate for the nonidealities [10].

Table 1 summarizes the main device- and system-level compensation techniques used to overcome trapped charge offsets, temporal drift, capacitive attenuation, temperature, and noise of ISFETs implemented in commercial technologies. Procedures to improve the sensor performance by modifying the passivation layer, such as the removal of the passivation top layers [19] or the replacement of the passivation layer with other materials [28], are not shown. Further details are discussed in [10].

Table 1 - Compensation techniques for ISFETs in commercial technologies (adapted from [10])

|                |        | Method.                                                  | Description.                                                                      | Advantages.                                                                                 | Disadvantages.                                                                                                                                    |

|----------------|--------|----------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                |        | UV exposure                                              | Exposure to UV for hours.                                                         | No need of extra circuits.                                                                  | Post-processing technique.                                                                                                                        |

|                | Device | Programmable-Gate<br>(PG) ISFET                          | A capacitor is added to the floating gate (FG) of ISFET with a bias voltage.      | Allows calibration algorithms or feedback to the FG.                                        | Reduction on sensor sensitivity.  Extra circuit components.  External bias voltage or lookup table.  Phases of operation increase the complexity. |

|                |        | Hot-electron injection                                   | Removal of electrons from the FG using large $V_{DS}$ .                           | No need of extra circuits.                                                                  | Requires high voltage. It is unidirectional.                                                                                                      |

| harge          |        | Bidirectional electron tunnelling                        | Addition or removal of electrons from the FG.                                     | Lower current levels than hot-electron injection. Allows to inject or remove electrons.     | Uses high voltages. Leakage current. Slow compensation process.                                                                                   |

| Trapped Charge |        | Reset switch on the FG<br>Source voltage<br>compensation | Switch at the FG for offset reset.<br>Modulation of the ISFET source<br>voltage.  | Simple circuit.  No need to access the FG.  No need of extra components or post-processing. | Leakage current reduces the measurement time. Limited compensation range. Specific to certain topologies.                                         |

|                |        | Technology with high quality dielectric [43]             | Controlled fabrication applying anneals in a hafnium dielectric.                  | No need to access the FG. No need of extra circuits.                                        | Requires a specific commercial process, not commonly available (ex. TSMC SOI 180 nm).                                                             |

|                | System | Baseline frame calibration                               | Subtraction of the mean of a number of baseline frames before measure the output. | Elimination of Fixed-pattern noise (FPN).                                                   | Averaging is computational and requires software processing.  Post-readout compensation.                                                          |

|                |        | Correlated Double<br>Sampling (CDS)                      | Typical CDS amplifier readout.                                                    | On-chip implementation.                                                                     | Uses a high frequency clock. Post-readout compensation.                                                                                           |

|                | Device | Offset calibration                                       | Reset to the FG or PG-ISFET.                                                      | Simple implementation. Direct feedback to the FG.                                           | Leakage current.                                                                                                                                  |

|                |        | Cycling of electric fields                               | Drift reset with an on-chip ring oscillator driving $V_{REF.}$                    | On-chip implementation.                                                                     | Oscillation of $V_{REF}$ can be restraining.                                                                                                      |

| ff.            | System | Differential measurement                                 | Subtract the output from a REFET or an ISFET in a ref. solution.                  | Eliminates common-mode voltages.                                                            | Requires 2 sensors. The 2 ISFETs must have same behavior.                                                                                         |

| Drift          |        | External signal processing                               | Based on sampling and differentiating of the output voltage.                      | Robustness.                                                                                 | Off-chip data processing. Assumes a negligible drift compared to pH changes.                                                                      |

|                |        | Correlated Double<br>Sampling (CDS)                      | Uses an OPAMP with switched-capacitor feedback.                                   | On-chip implementation.                                                                     | Needs a clock period higher than the drift time.<br>Post-readout compensation.                                                                    |

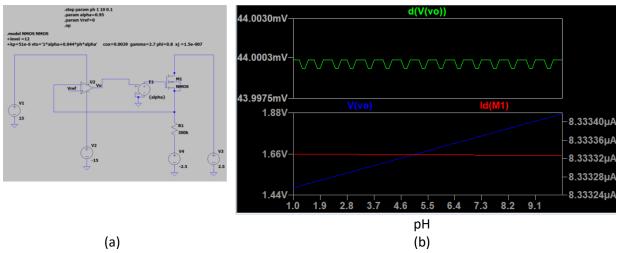

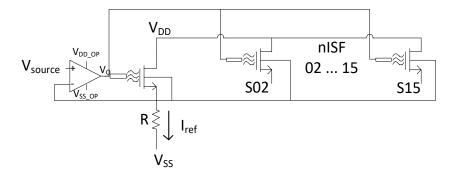

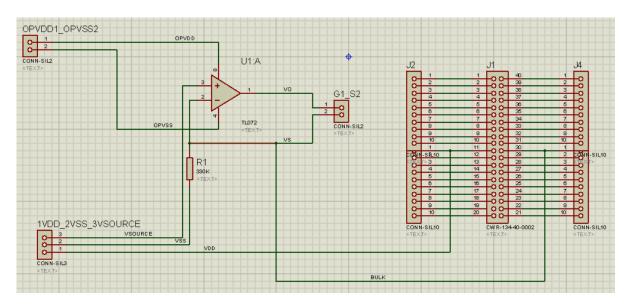

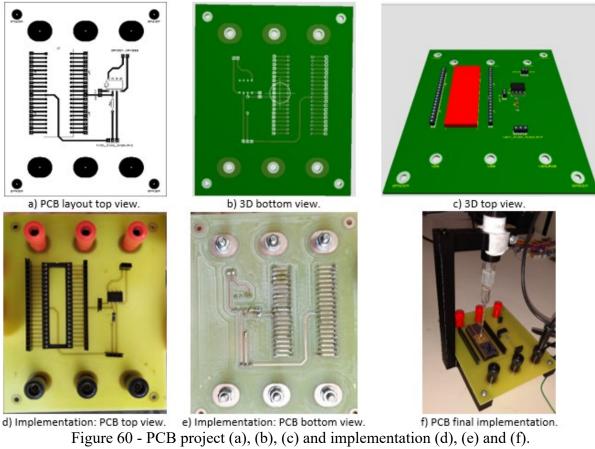

|                |        |                                                          |                                                                                   |                                                                                             |                                                                                                                                                   |