Julio Cesar Dias

# UNIDIRECTIONAL CONVERTERS WITH SWITCHED-CAPACITORS AND MULTISTATE SWITCHING CELLS

Florianópolis 2022

Julio Cesar Dias

# UNIDIRECTIONAL CONVERTERS WITH SWITCHED-CAPACITORS AND MULTISTATE SWITCHING CELLS

Tese submetida ao Programa de Pós-graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do Grau de Doutor em Engenharia Elétrica. Orientador: Prof. Telles Brunelli Lazzarin, Dr.

> Florianópolis 2022

Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

```

Dias, Julio Cesar

Unidirectional Converters with Switched-Capacitors and

Multistate Switching Cells / Julio Cesar Dias ;

orientador, Telles Brunelli Lazzarin, 2023.

203 p.

Tese (doutorado) - Universidade Federal de Santa

Catarina, Centro Tecnológico, Programa de Pós-Graduação em

Engenharia Elétrica, Florianópolis, 2023.

Inclui referências.

1. Engenharia Elétrica. 2. Eletrônica de Potência. 3.

Capacitor chaveado. 4. Conversores unidirecionais. 5.

Célula de comutação multiestados. I. Brunelli Lazzarin,

Telles. II. Universidade Federal de Santa Catarina.

Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

```

Julio Cesar Dias

**Título:** Unidirectional Converters with Switched-Capacitors and Multistate Switching Cells

O presente trabalho em nível de doutorado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

> Prof. René Pastor Torrico-Bascopé, Dr. Universidade Federal do Ceará

Prof. Levy Ferreira Costa, Ph. D.Eindhoven University of Technology

Prof. Romeu Hausmann, Dr. Universidade Regional de Blumenau

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de doutor em Engenharia Elétrica.

> Prof. Telles Brunelli Lazzarin, Dr. Coordenador do Programa de Pós-Graduação

\_\_\_\_\_

Prof. Telles Brunelli Lazzarin, Dr. Orientador(a)

Florianópolis, 2023.

À minha família, que me apoi<br/>ou durante todo o processo de desenvolvimento acadêmico e pessoal.

#### AKNOWLEDGEMENT

Primeiramente, agradeço à minha família, meu pai Nilton, minha saudosa mãe Lourdes, aos meus irmãos Renato, Roberto e à Liliane. O doutorado não é somente fruto desses anos de trabalho, mas também de toda a vida, de todos os bons exemplos, apoio e condições que minha família proporcionou para que eu chegasse nessa etapa. Agradeço também aos familiares que sempre me incentivaram a investir na minha paixão por eletrônica, pela ciência e pelo conhecimento. Entre eles, gostaria de destacar meu agradecimento aos meus tios Acires e Fátima, que me apoiaram na mudança para Florianópolis, ao Geovane e Luciane pelo apoio quando perceberam meu interesse por eletrônica, e aos demais parentes não citados que sempre me apoiaram durante meu desenvolvimento pessoal e profissional. Gostaria também de agradecer não somente à minha família de sangue, mas também à dona Mara e sua família, que me ofereceram estadia durante bons anos do mestrado e doutorado. Sua generosidade e apoio tornaram o processo muito mais fácil e confortável.

Agradeço imensamente ao meu orientador, Telles Brunelli Lazzarin. Mesmo com maior parte da orientação sendo remota durante esse período, o professor Telles sempre se mostrou disponível e prestativo. Sem sua excelente didática e metodologia, esse trabalho não teria os mesmos resultados. Durante um trabalho de longa duração e muita pesquisa é muito fácil se perder nas inúmeras ideias que surgem, mas o professor Telles sempre me ajudou a me guiar, encontrar um foco e determinar as metas para a conclusão do trabalho.

Quero agradecer a todos os colegas de laboratório, professores e demais pessoas que fizeram parte da minha vida acadêmica e com quem compartilhei experiências e aprendi muito durante o doutorado, entre eles o Victor, Luiz, Matheus, Behr e Lennon, com quem compartilhei experiências na LUG que me ajudaram a crescer como profissional. Aos demais colegas do INEP com quem compartilhei o laboratório, tive conversas no corredor e que me ajudaram em diversas tarefas, Marcelo Guepfrih que me fez companhia durante ensaios, aos Eduardos, que durante a pandemia deram um suporte no laboratório quase deserto, assim como demais colegas do INEP pela parceria. Também devo agradecer aos colaboradores do INEP, Diogo, Pacheco e Coelho, que foram facilitadores de todo esse processo. Agradeço aos colegas e professores da graduação na FURB. Durante minha graduação houve um período que pensei em desistir do curso por não ver nenhuma perspectiva. A iniciação científica me ajudou a redescobrir a paixão pela área e me motivou a seguir na academia, por isso agradeço imensamente ao Julcemar Capellaro e ao professor Romeu Hausmann pela oportunidade que tive de aprender na prática com pesquisa científica. Também devo agradecer aos colegas de laboratório, Roni Facchi, André Schlingmann, Roberto Burger, Alex Amaro, Adilson Stankiewieckz, e aos vários parceiros com quem compartilhei diversas conversas e tornaram a experiência mais divertida. Quero agradecer também aos demais professores que, apesar de não terem me orientado formalmente, eram presentes no laboratório e me proporcionaram bastante aprendizado, entre eles os professores Luiz Koehler e Adriano Péres.

Por fim, agradeço a todos os amigos não mencionados, que talvez não tenham participado dessa jornada profissional, mas sempre me deram apoio.

$Perfection\ itself\ is\ imperfection.$

(Vladimir Horowitz)

#### ABSTRACT

This work proposes new rectifier topologies with high voltage gain, low input harmonic content and reduced voltage and current stress in the semiconductor devices. The structures proposed in this work integrate switched-capacitor cells and multistate switching cells to achieve higher voltage gains and higher output power. Switched-capacitor cells use switches to associate capacitors in series and parallel in different stages, providing high voltage gain, modularity, divided voltage across the capacitors and switches and self-balanced capacitor voltages. Multistate switching cells use intercell transformers to divide the total input current between the converter legs, thus reducing the current stress across the switches. They also have a multilevel input characteristic, which reduces the input current harmonic content and the size of input filters. The use of these techniques can increase the power levels without affecting the control complexity of the system. They also allow the use of devices with lower costs by dividing the voltage and current in the components and providing a multilevel voltage characteristic in the input. This work presents a dc-dc converter to introduce the concept and then expands it into single-phase and three-phase converters that integrate multistate switching cells with switched-capacitor cells. The steady-state and dynamic analysis of the three topologies are performed and supported by simulation results and experimental results performed on converters that use the integration of three-state switching cells and symmetrical ladder switched-capacitor cells. The converters were experimentally validated with modular prototypes. The dc-dc module was build in a way that made it possible to add more modules to test the ac-dc single-phase and the three-phase prototype. In the dc-dc converter it was possible to convert 100 V to 1200 V with a 1 kW output power. It was possible to test the ac-dc topology by adding a diode bridge in the module input and electrolytic capacitors in its output. The single-phase rectifier converted a 127 V input to a 1200 V output with a 1.3 kW output power. By replacing the boost diodes in the modules by MOSFETs and associating the modules in parallel, it was possible to test the three-phase rectifier with a 220 V input voltage, 1200 V output and 4 kW. All prototypes achieved a 1200 V output with reduced voltage stress on the devices and shared currents in the intercell transformer windings. The dc-dc and the three-phase converters achieved efficiency levels in the range of 97%, whereas the single-phase efficiency was lower than 96% due to the power losses on the diode bridge. In the dc-dc and three-phase converter, most of the losses were MOS-FET switching losses. The proposed concept was validated by the experiments, but the experiments also show in which aspects the proposed concept can be improved in future works. The proposed concept can be suitable for high-voltage gain applications, such as renewable energy systems due to its gain profile and shared voltage and current in the devices.

**Keywords:** High voltage gain. Switched capacitor. Multistate switching cell. Power factor correction. Unidirectional converters.

#### RESUMO

Este trabalho propõe novas topologias de retificadores com elevado ganho em tensão, corrente de entrada com baixo conteúdo harmônico e esforços de tensão e corrente reduzidos nos dispositivos semicondutores. As estruturas propostas neste trabalho integram células de capacitor chaveado e células de comutação multiestados com o fim de obter maiores ganhos de tensão e capacidade de potência. Células de capacitor chaveado usam interruptores para associar capacitores em série e em paralelo em diferentes estágios, assim fornecendo elevado ganho em tensão, modularidade, divisão da tensão nos capacitores e interruptores e, por fim, capacitores com tensões naturalmente equilibradas. Células de comutação multiestados usam um transformador de interfase para dividir a corrente total de entrada entre os braços do conversor, assim reduzindo os esforços de corrente nos interruptores. Também apresentam uma característica de entrada multinível, que reduz o conteúdo harmônico da corrente de entrada e o tamanho dos filtros. Este trabalho propõe topologias geradas a partir desses princípios e realiza a análise de um conversor CC-CC, um retificador monofásico e um trifásico propostos baseados no conceito introduzido. As análises estática e dinâmica das três topologias são realizadas e resultados de simulação e experimentais são usados para validar o estudo teórico. Os conversores foram validados experimentalmente com protótipos modulares. O módulo CC-CC foi construído de forma que possibilitou a adição de mósulos para realizar os testes como conversor CA-CC monofásico e trifásico. No conversor CC-CC foi possível converter uma entrada de 100 V em 1200 V processando 1 kW. Foi prossível testar o retificador monofásico ao adicionar uma ponte de diodos na entrada do módulo e capacitores eletrolíticos na saída. O retificador monofásico foi projetado para uma entrada de 127 V e uma saída de 1200 V, processando 1.3 kW. Ao trocar os diodos do boost por interruptores ativos e associando os módulos em paralelo, foi possível testar o retificador trifásico com uma entrada de 220 V, saída de 1200 V e 4 kW. Todos os protótipos atingiram o valor de 1200 V de tensão de saída com esforços de tensão reduzidos nos dispositivos e correntes divididas nos enrolamentos do transformador intercélulas. Os conversores CC-CC e o trifásico atingiram rendimentos na faixa de 97%, enquanto o rendimento do monofásico foi abaixo de 96% devido às perdas na ponte de diodos. Nos conversores CC-CC e trifásico a maior parte das perdas é na comutação dos MOSFETs. O conceito proposto foi validado nos experimentos, mas esses experimentos também serviram para mostrar pontos de aprimoramento para trabalhos futuros. O conceito proposto demonstra possibilidade de uso em aplicações renováveis devido à sua característica de ganho com possibilidade de compartilhamento de tensão e corrente nos dispositivos.

**Palavras-chave:** Alto ganho em tensão. Capacitor chaveado. Célula de comutação multiestados. Correção de fator de potência. Conversores unidirecionais.

### **RESUMO EXPANDIDO**

### Introdução

Diversas aplicações cotidianas requerem o uso de conversores de elevado ganho, como acionamento de máquinas, aplicações renováveis, armazenamento de energia, entre outros. A conversão de energia em alto ganho possui diversos desafios relacionados a limitações existentes na tecnologia de componentes eletrônicos. Dispositivos semicondutores dimensionados para valores de tensão ou corrente elevados tendem a ser caros e possuem elementos parasitas que prejudicam o rendimento e volume dos conversores. As elevadas impedâncias parasitas de dispositivos semicondutores de alta potência aumentam as perdas no circuito, o que influencia não somente no seu rendimento, mas também no volume e custo por muitas vezes necessitar de sistemas de arrefecimento mais robustos. As características dinâmicas lentas de dispositivos para elevados valores de tensão também prejudicam o rendimento com o aumento das perdas de comutação, e influenciam no volume devido à necessidade de filtros maiores para atenuar o conteúdo harmônico de baixa frequência. Tendo em vista esses problemas, este trabalho propõe como alternativa a integração de células de capacitor chaveado em conversores com células de comutação multiestados. Células de comutação multiestados utilizam transformadores intercélulas para dividir corrente entre dispositivos e multiplicar a frequência que será filtrada a partir de pulsos defasados nos dispositivos da célula de comutação. Essa célula reduz o tamanho dos filtros e também reduz as perdas nos dispositivos semicondutores ao dividir a corrente entre eles. A célula de capacitor chaveado é utilizada para dividir o nível de tensão de saída entre os dispositivos e dividir a tensão entre os capacitores de saída de forma equilibrada, além da possibilidade de modularização para aumentar o ganho de tensão do circuito sem afetar os níveis de tensão nos dispositivos semicondutores. Foram propostas três topologias para a validação da proposta, um conversor CC-CC, um CA-CC monofásico e um CA-CC trifásico.

### Objetivos

Este trabalho tem como objetivo propor novas topologias de conversores com ganho de tensão elevado, potência elevada e redução de esforços de tensão e corrente nos dispositivos semicondutores.

### Metodologia

Foi realizada uma revisão bibliográfica para analisar o estado da arte de topologias de alto ganho em tensão e potência, e também realizado um estudo em células de capacitor chaveado e células de comutação multiestados. A partir desse estudo, foram propostas formas de integrar esses dois conceitos para gerar novas topologias. Esses dois conceitos foram aplicados na topologia *boost* para a concepção de topologias CC-CC e CA-CC com correção de fator de potência. Foi realizada a análise teórica dessas topologias a fim de realizar os cálculos de dimensionamento dos dispositivos e estratégia de controle. Após a análise teórica

estática e dinâmica dos conversores, foram realizadas simulações para validar os resultados teóricos e, por fim, foram confeccionados módulos de potência para a validação experimental das topologias propostas.

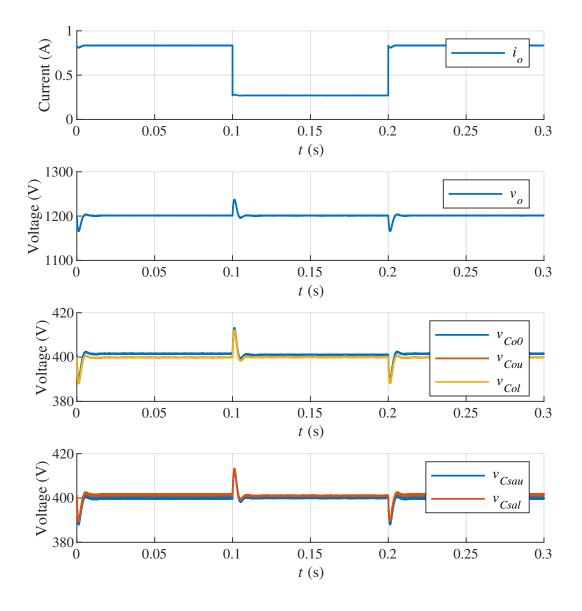

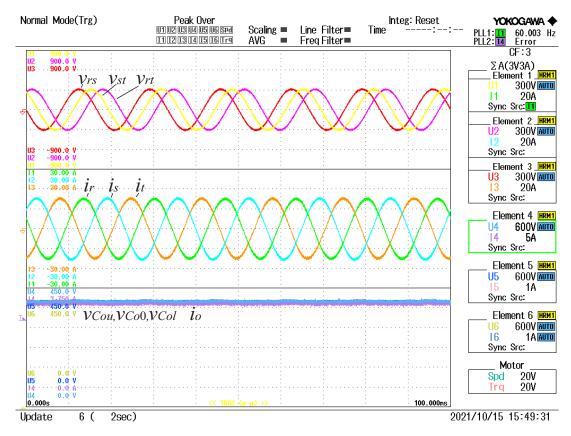

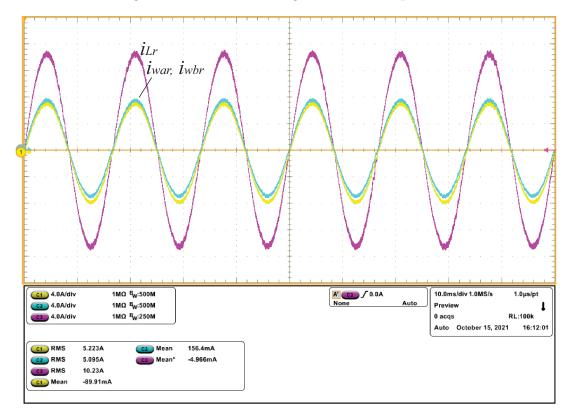

## Resultados e Discussão

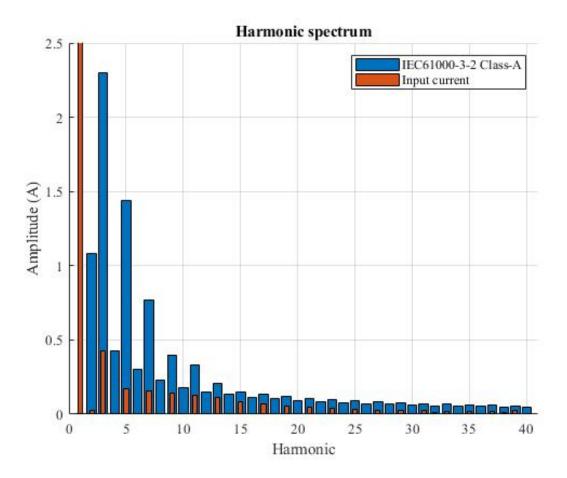

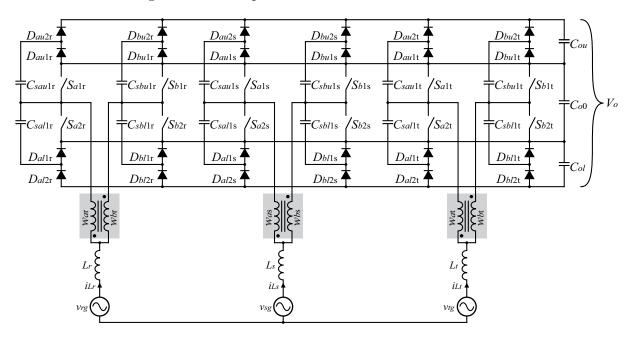

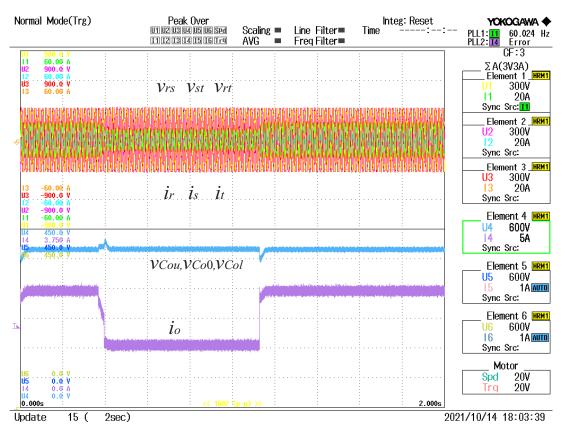

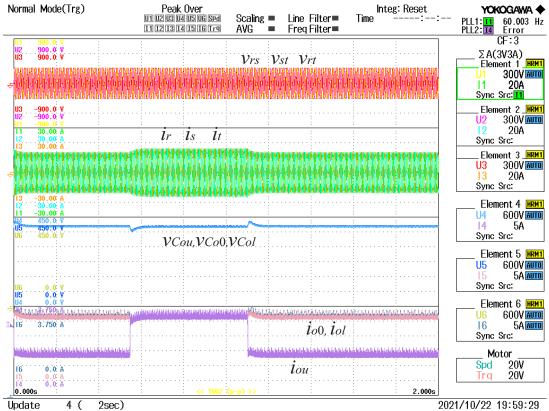

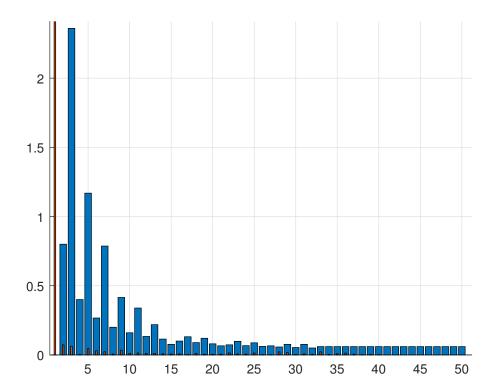

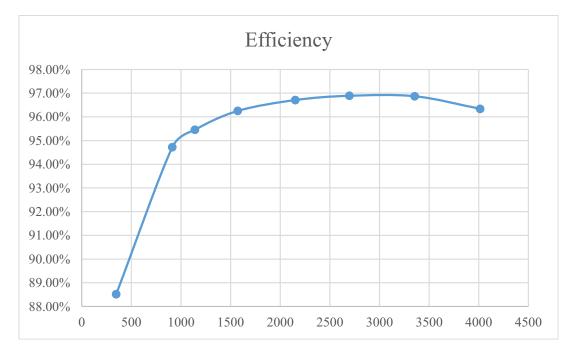

Para validar o conceito, implementou-se na prática três conversores, um conversor CC-CC com 100 V de entrada, 1200 V de saída e potência de saída de 1 kW; um retificador monofásico com 127 V de entrada, 1200 V de saída e 1300 W de potência de saída; e um retificador trifásico com 220 V de entrada, 1200 V de saída e 4 kW. Todos eles foram implementados com células de comutação de três estados e duas células *ladder* em cada braço da célula de comutação. Todos os conversores realizaram a conversão com a tensão nos capacitores equilibrada, assim conseguindo dividir a tensão nos interruptores e alcançando uma saída de 1200 V com 400 V em cada dispositivo semicondutor. A célula de comutação multiestados foi capaz de multiplicar a componente da frequência de comutação, além de dividir a corrente de entrada no transformador de interfase. O equilíbrio das correntes foi obtido de forma natural, sem técnicas ativas de controle, ao utilizar gate drivers com características muito similares no projeto. Os retificadores operaram com fator de potência acima de 0.99 e apresentaram conteúdo harmônico condizente com os limites da norma IEC 61000-3-2 e IEC 61000-3-4. O conversor CC-CC atingiu rendimento de 97%, mas ao aumentar a tensão de entrada e potência de saída foi possível atingir rendimento na faixa de 98%. O rendimento no retificador monofásico caiu abaixo de 96% devido à inserção de uma ponte de diodos na entrada. No retificador trifásico foi possível obter rendimento na faixa de 97%.

## Considerações Finais

Foi proposta a integração de células de capacitor chaveado com células de comutação multiestados a fim de conceber topologias de conversores estáticos com ganho de tensão elevado e elevado processamento de corrente, mas mantendo esforços baixos de tensão e corrente nos dispositivos semicondutores. Os conversores utilizados para validar a proposta foram capazes de realizar o processamento de potência de acordo com a proposta, apresentaram esforços reduzidos de tensão e corrente nos dispositivos e regulação na tensão de saída e corrente de entrada. Ainda é possível em trabalhos futuros aprimorar o desempenho dos conversores a partir de otimização no dimensionamento de componentes, uso de ponte síncrona no retificador monofásico e utilização de técnicas para redução das perdas de comutação nos conversores, entre outros.

**Palavras-chave:** Alto ganho em tensão. Capacitor chaveado. Célula de comutação multiestados. Correção de fator de potência. Conversores unidirecionais.

# LIST OF FIGURES

| Figure 1                  | Boost PFC rectifier                                                                                                                                  | 34  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2                  | Typical control strategy of PFC rectifiers                                                                                                           | 34  |

| Figure 3                  | Three-phase boost rectifiers with diode bridge [29]: (a) inductor on the dc                                                                          | 35  |

| Figure 4                  | ductors on the ac side<br>Three-phase bidirectional boost rectifier [29]                                                                             |     |

| Figure 5                  | 18-pulse series-type rectifiers [34]: (a) diode bridge, (b) SCR bridge                                                                               |     |

| Figure 6                  | Multilevel three-phase rectifier topologies [36]: (a) Unidirectional five-level                                                                      | 57  |

| 0                         | b) Five-level diode clamped rectifier, (c) Five-level flying-capacitor rectifier.                                                                    | 38  |

| Figure 7                  | Current sharing techniques: (a) interleaved converter, (b) 3SSC, (c) MSSC.                                                                           |     |

| Figure 8                  | Single-phase PFC rectifiers with MSC [48]: (a) 3SSC, (b) 4SSC, (c) 5SSC                                                                              |     |

| 0                         | ded interphase transformers.                                                                                                                         | 40  |

| Figure 9                  | Single-phase bridgeless boost rectifier with 3SSC [50]                                                                                               | 40  |

| Figure 10                 | Single-phase T-type rectifier with 3SSC [51]                                                                                                         | 41  |

| Figure 11                 | Three-level MSSC rectifiers [52]                                                                                                                     | 41  |

| Figure 12                 | Single-phase boost NPC rectifier with 3SSC [54]                                                                                                      | 41  |

| Figure 13                 | Three-phase inverter with 4SSC [53]                                                                                                                  | 42  |

| Figure 14                 | Three-phase NPC inverter with 4SSC [53]                                                                                                              | 42  |

| Figure 15                 | Three-phase unidirectional multilevel rectifier with MSSC [60]                                                                                       | 43  |

| Figure 16                 | Boost converter with 3SSC and voltage multiplier [64]                                                                                                | 43  |

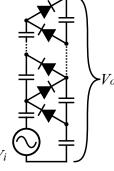

| Figure 17                 | Greinacher/CW voltage multiplier [71].                                                                                                               | 44  |

| Figure 18                 | SC cells [78]: (a) Ladder, (b) Dickson, (c) Fibonacci, (d) Series-Parallel,                                                                          |     |

| (e) Double                | r                                                                                                                                                    | 45  |

| Figure 19                 | Generalization of interleaved boost converter with voltage multiplier cells                                                                          |     |

| [80]                      |                                                                                                                                                      | 46  |

| Figure 20<br>flyback stru | Boost-flyback converter with CW SC cell [82]: (a) Conventional boost-<br>ucture, (b) Input power sharing                                             | 46  |

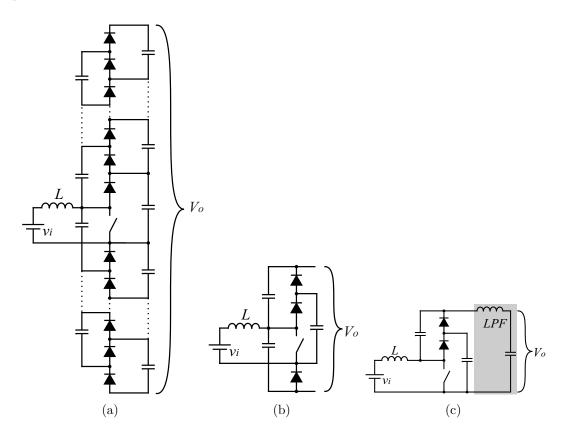

| Figure 21                 | Hybrid boost converter with ladder SC cell [83]: (a) 'M' voltage multiplier                                                                          |     |

| cells, (b) $C$            | Output capacitor integration into the cell                                                                                                           | 47  |

| •                         | HBC [87]: (a) Generalization, (b) Symmetric configuration, (c) Output                                                                                | . – |

| -                         | ass filter                                                                                                                                           | 47  |

| Figure 23                 | Hybrid interleaved boost converter with ladder SC cell [88]                                                                                          | 48  |

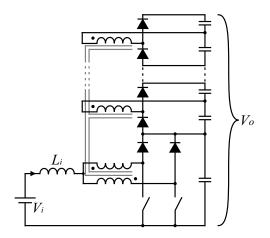

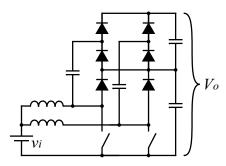

| Figure 24                 | HBR [99]                                                                                                                                             | 48  |

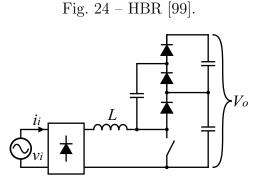

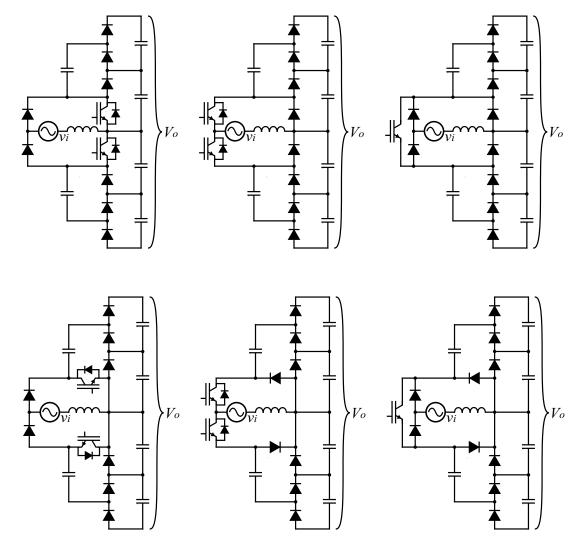

| Figure 25                 | Three-level single-phase HBR with different switching cells [101]                                                                                    | 49  |

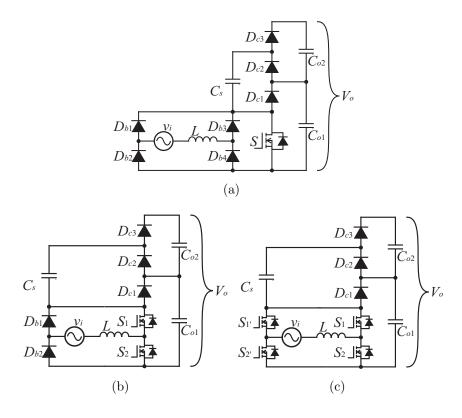

| Figure 26                 | HBR with inductor on AC side [102]: (a) HBR with diode bridge, (b)                                                                                   | 50  |

|                           | HBR with two switches, (c) Bridgeless HBR with four switches                                                                                         | 50  |

| Figure 27                 | Bridgeless HBR with CW cell [105]                                                                                                                    | 50  |

| Figure 28                 | Hybrid SEPIC rectifier [106].                                                                                                                        | 51  |

| Figure 29 phase mat       | Hybrid matrix converters: (a) CW rectifier with a three-phase-to-single-<br>rix input [107], (b) HBC in the intermediary stage of an indirect matrix |     |

| converter [     | 94]                                                                          | 52 |

|-----------------|------------------------------------------------------------------------------|----|

| Figure 30       | Hybrid multilevel three-phase rectifier [108]                                | 53 |

| Figure 31       | Hybrid three-phase inverter [109]                                            | 53 |

| Figure 32       | Hybrid three-phase SEPIC rectifier [110]                                     | 54 |

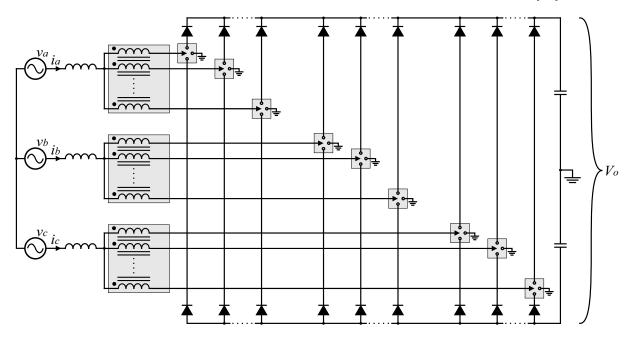

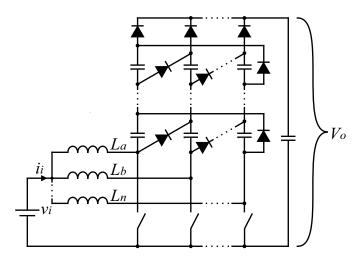

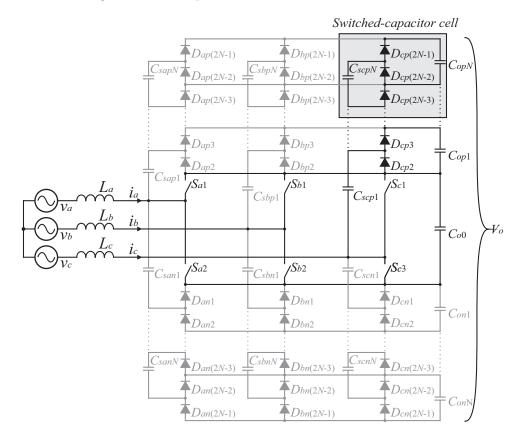

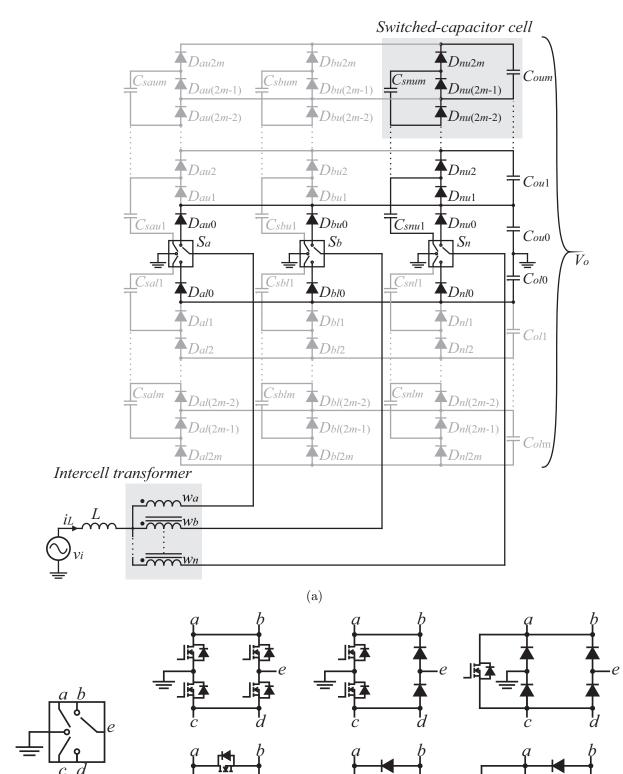

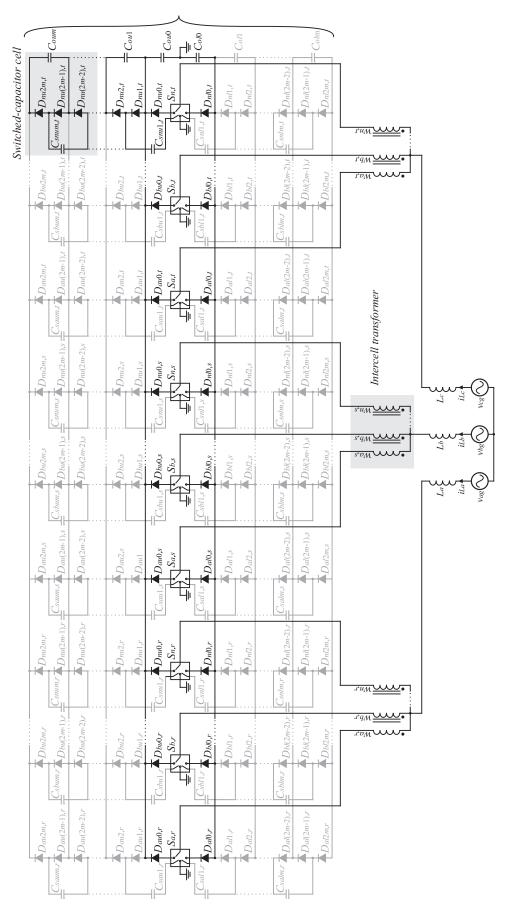

| Figure 33       | Hybrid modular three-phase boost rectifier                                   | 55 |

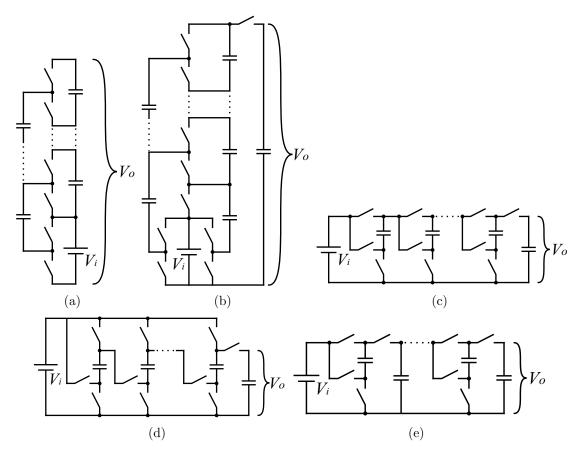

| Figure 34       | Single-phase rectifiers and configurations: (a) Generalized structure, (b)   |    |

| Common-se       | ource, (c) Totem-pole, (d) Full-bridge                                       | 56 |

| Figure 35       | Three-phase HBR - Generalized structure                                      | 58 |

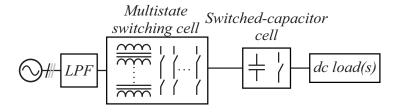

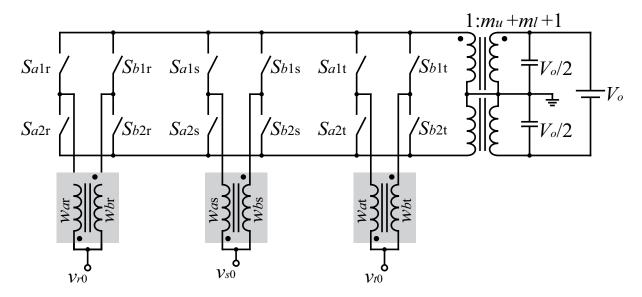

| Figure 36       | Generalization of the proposed concept                                       | 58 |

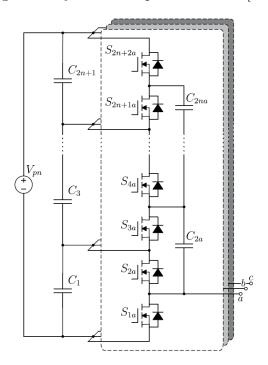

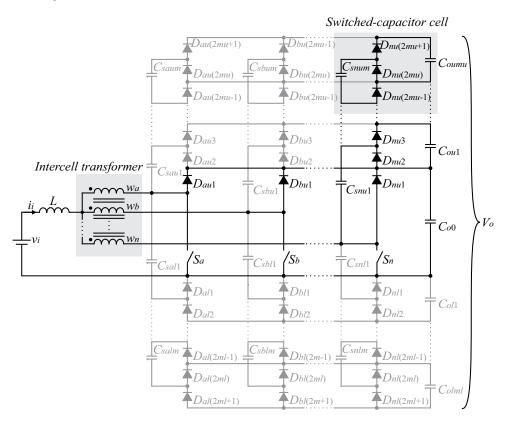

| Figure 37       | HBC with MSSC and SC cell - Generalized structure                            | 59 |

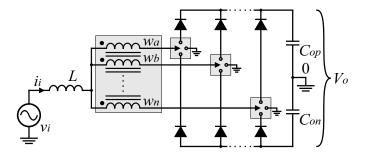

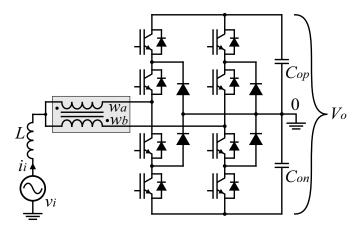

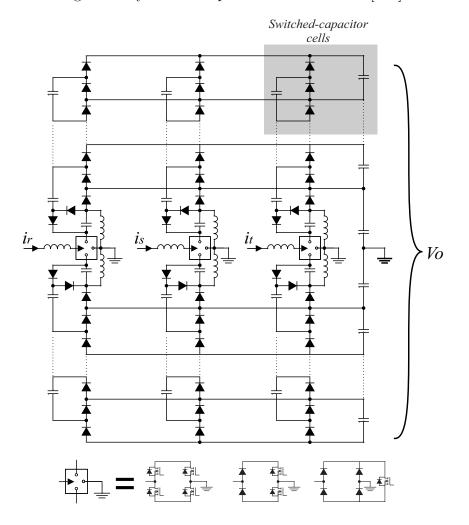

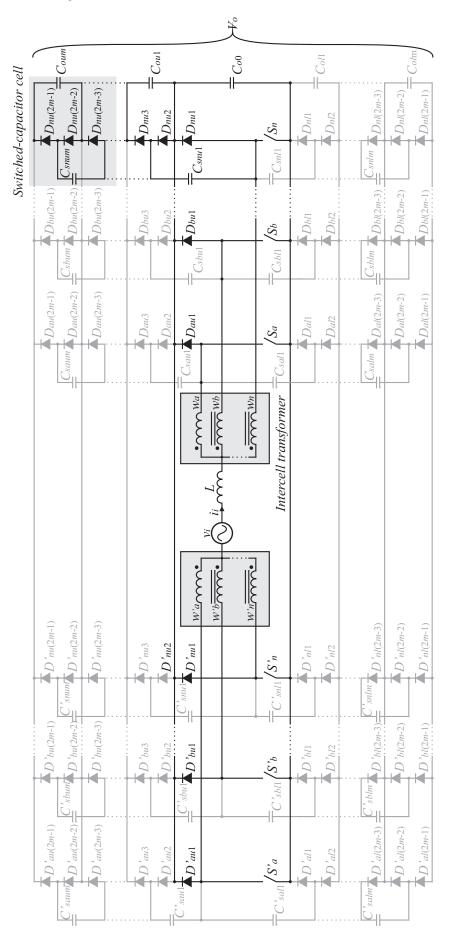

| Figure 38       | Single-phase HBR with MSSC and SC cell - Generalized structure               | 59 |

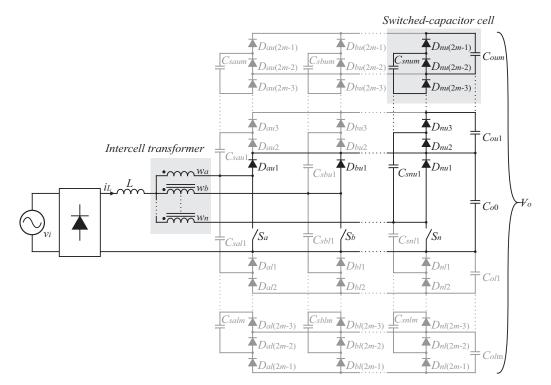

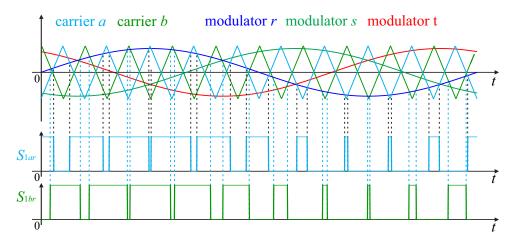

| Figure 39       | Bridgeless HBR with MSSC and SC cell - Generalized structure                 | 61 |

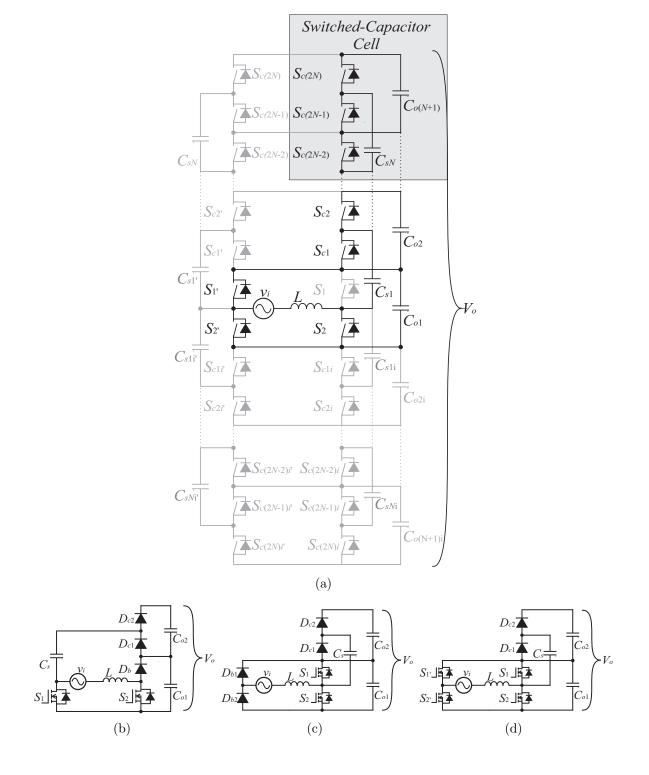

| Figure 40       | Multilevel HBR with MSSC and SC cell: (a) Generalized structure, (b)         |    |

| Switching-o     | cell configurations                                                          | 62 |

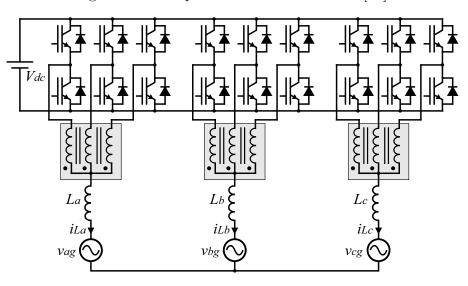

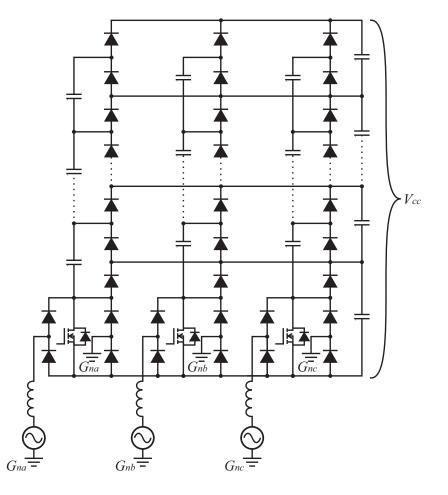

| Figure 41       | Three-phase HBR with MSSC and SC cell - Generalized structure                | 63 |

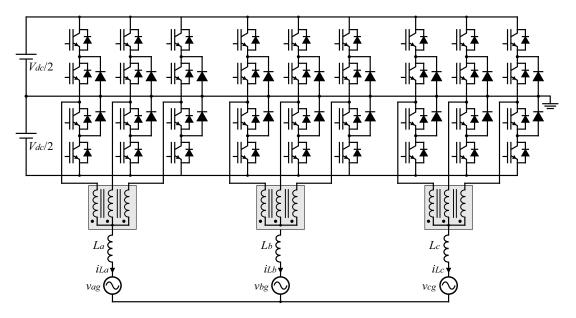

| Figure 42       | Multilevel Three-phase HBR with MSSC and SC cell - Generalized struc-        |    |

|                 |                                                                              | 64 |

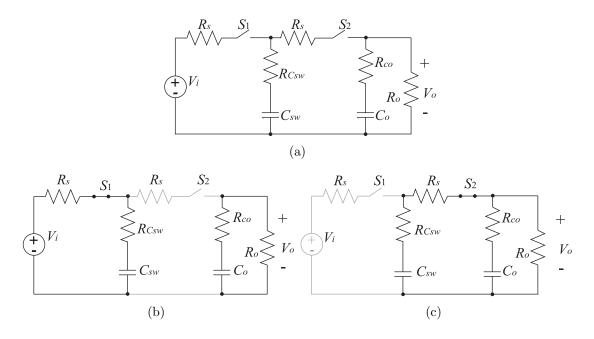

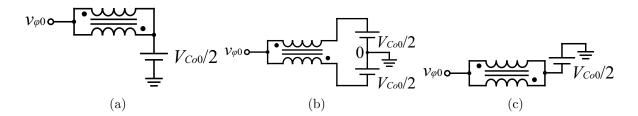

|                 | Unity gain SC converter: (a) topology, (b) capacitor charging, (c) capacitor | co |

| 0 0             | $g_{1}$                                                                      | 68 |

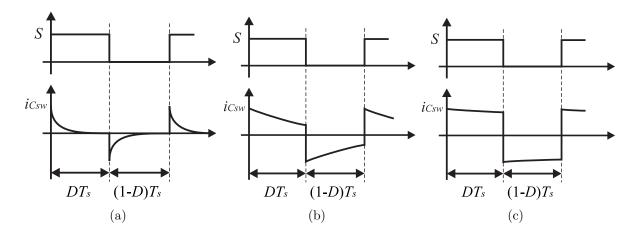

| Figure 44       | SC charge modes: (a) complete charge (CC), (b) partial charge (PC), (c) (NC) | 68 |

| Figure 45       | Equivalent circuit of SC converters                                          | 69 |

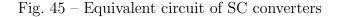

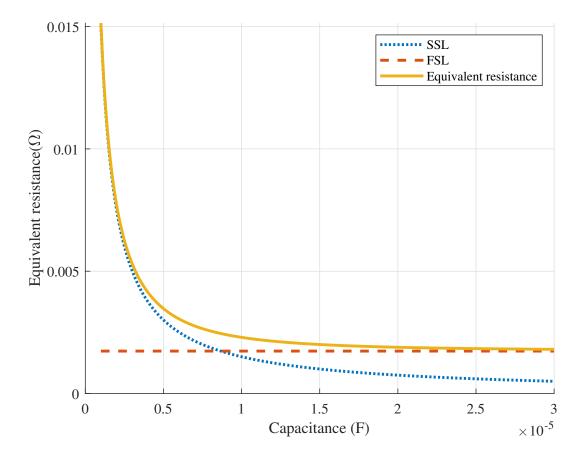

| Figure 46       | Equivalent resistance and asymptotic limits [78]                             | 70 |

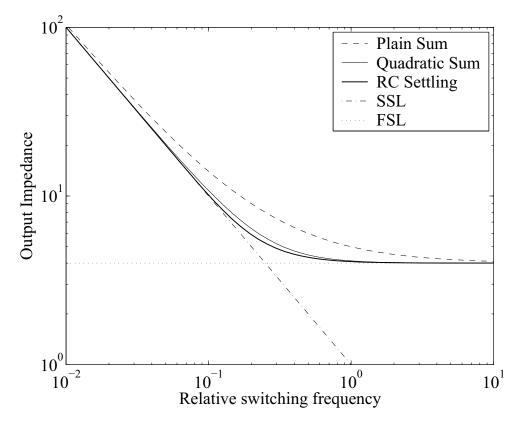

| Figure 47       | Equivalent circuit of parallel connected SC converters                       | 71 |

| Figure 48       |                                                                              | 71 |

| Figure 49       | Ladder SC cell topological states and charge flow: (a) upper SC storage      | 11 |

| 0               |                                                                              | 72 |

| Figure 50       | Equivalent resistance as a function of the switching frequency.              | 75 |

| Figure 51       | Equivalent resistance as a function of the duty cycle                        | 76 |

| Figure 52       | Equivalent resistance as a function of the capacitance $C_s$                 | 77 |

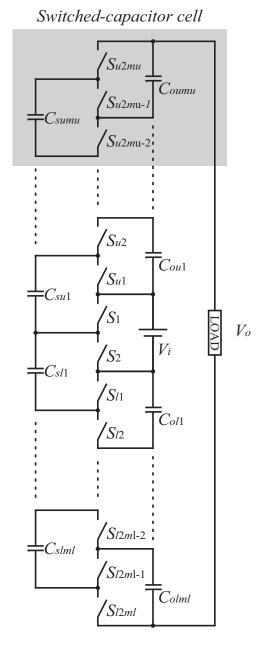

| Figure 53       | Generalization of the symmetrical ladder SC cell.                            | 78 |

| Figure 54       | Generalized symmetrical SC cell topological states and charge flow: (a)      |    |

| 0               | storage and lower SC transfer stage, (b) upper SC transfer and lower SC      |    |

| storage sta     | ge                                                                           | 79 |

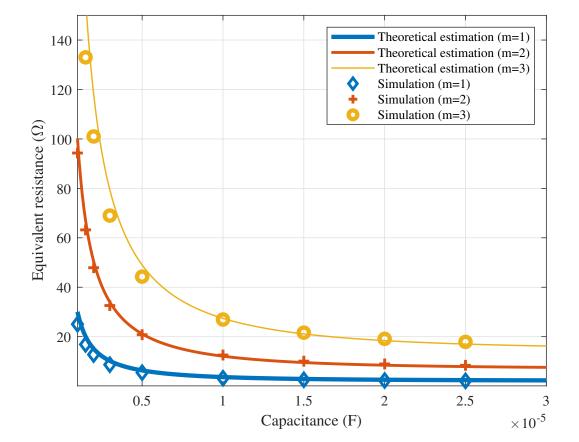

| Figure 55       | Theoretically estimated and simulated equivalent resistance                  | 82 |

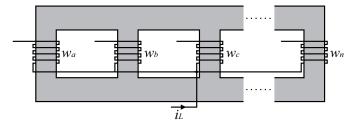

| Figure 56       | Implementation of the multiphase ICT                                         | 85 |

| Figure 57       | MSSC configurations: (a) 3SSC, (b) single transformer MSSC, (c) MSSC         |    |

| single-phas     | e transformers and (d) MSSC with multiphase transformers                     | 86 |

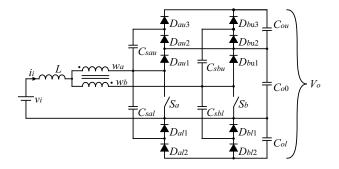

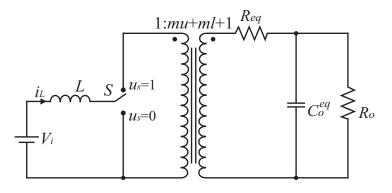

| Figure 58       | Boost converter with 3SSC and SC cells                                       | 86 |

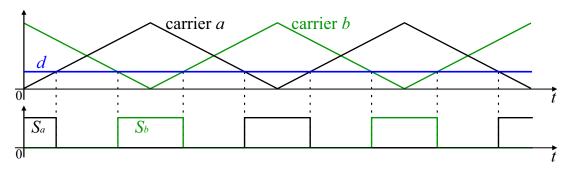

| Figure 59       | Modulation scheme in region A.                                               | 87 |

| Figure 60       | Hybrid boost converter with MSSC and SC - Operational states in region       |    |

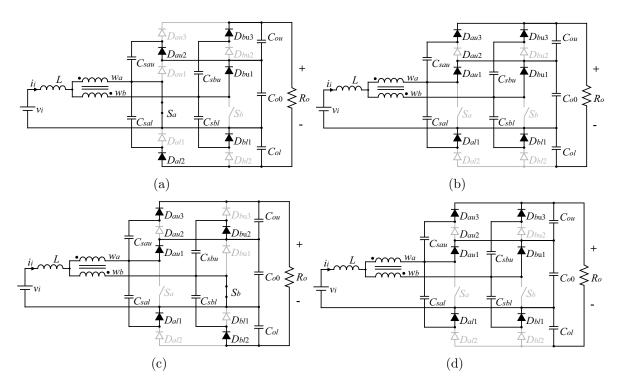

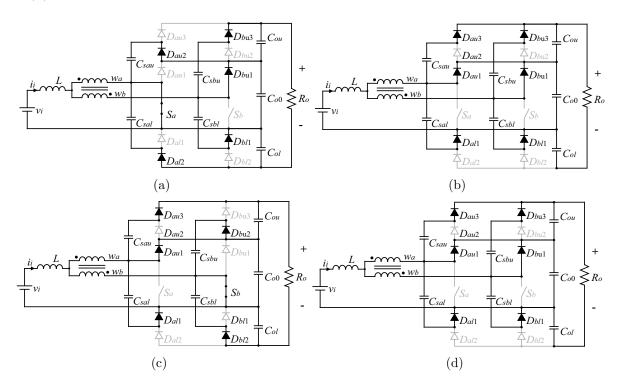

| A: (a) to $(a)$ | d) represent the stages 1 to 4                                               | 88 |

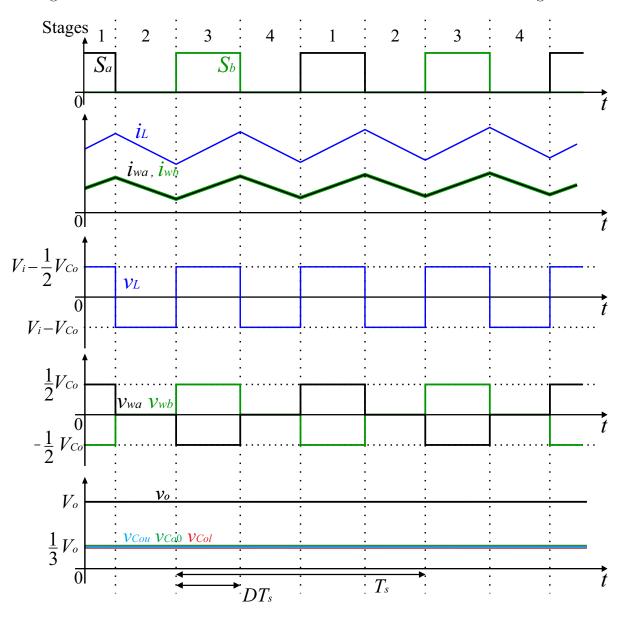

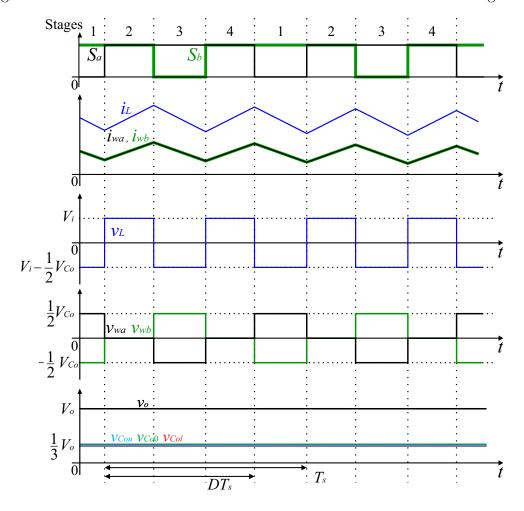

| Figure 61         | Main waveforms of the boost converter with 3SSC and SC in region A $89$          |

|-------------------|----------------------------------------------------------------------------------|

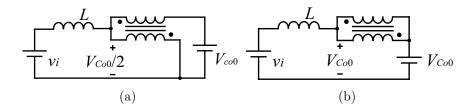

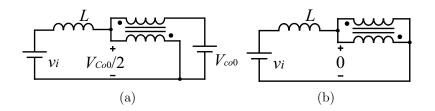

| Figure 62         | Equivalent circuits in region A: (a) stages 1 and 3, (b) stages 2 and 4 90       |

| Figure 63         | Modulation scheme for region B 91                                                |

| Figure 64         | Hybrid boost converter with MSSC and SC - Operational states in region           |

| B: (a) to (c      | l) refer to stages 1 to $4$                                                      |

| Figure 65         | Main waveforms of the boost converter with 3SSC and SC in region B 93 $$         |

| Figure 66         | Equivalent circuits in region B: (a) stages 1 and 3, (b) stages 2 and 4 93       |

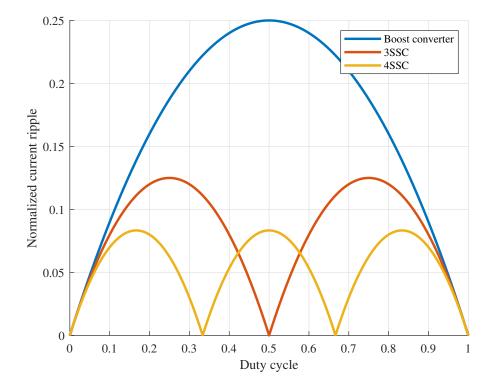

| Figure 67         | Normalized current ripple                                                        |

| Figure 68         | Equivalent circuit for dynamic analysis                                          |

| Figure 69         | Averaged equivalent circuit                                                      |

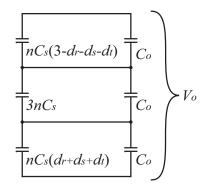

| Figure 70         | Equivalent output capacitance 100                                                |

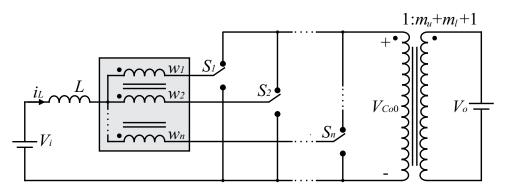

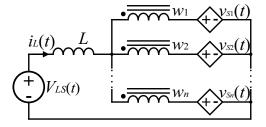

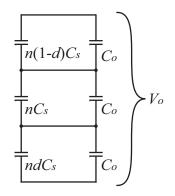

| Figure 71         | Equivalent DC-DC converter                                                       |

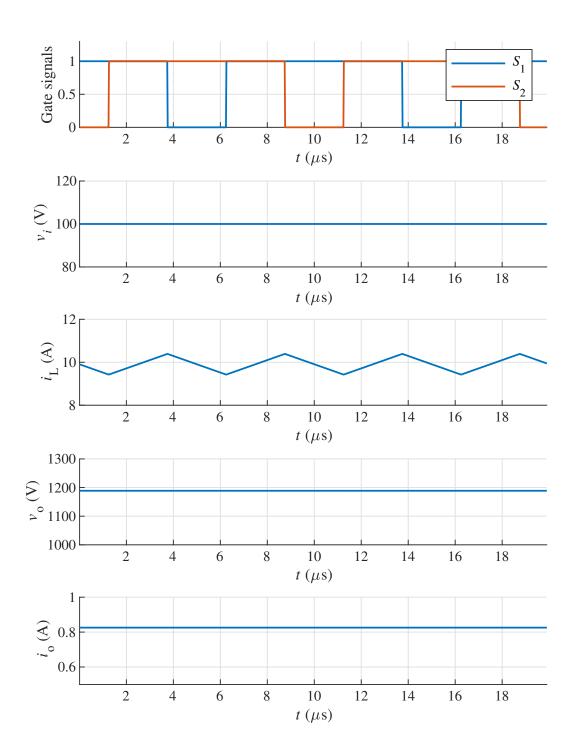

| Figure 72         | Simulation of the DC-DC topology - Rated power                                   |

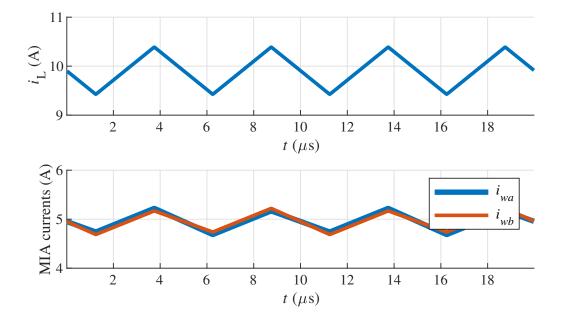

| Figure 73         | Simulation of the DC-DC topology - Current in the inductor and ICT 104           |

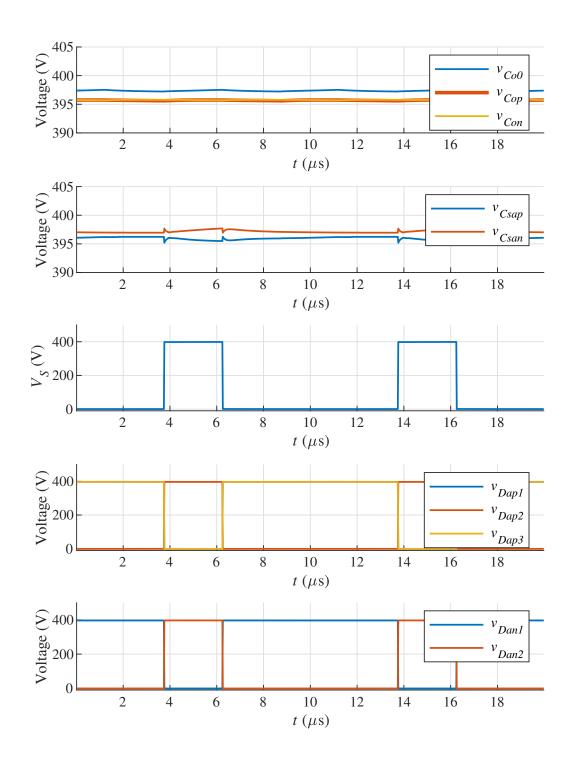

| Figure 74         | Simulation of the DC-DC topology - Voltage stress across the switch,             |

| diodes and        | capacitors of leg $a$                                                            |

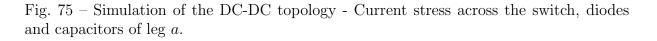

| Figure 75         | Simulation of the DC-DC topology - Current stress across the switch,             |

| diodes and        | capacitors of leg $a$                                                            |

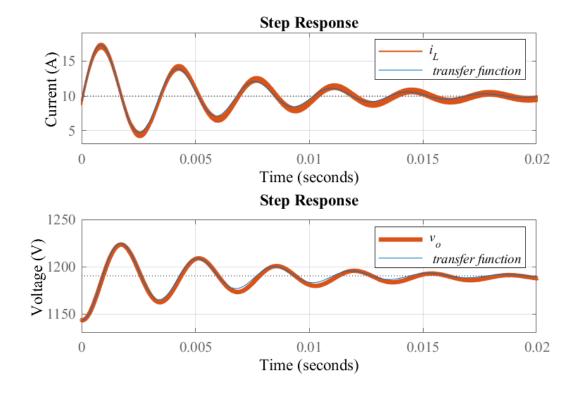

| Figure 76         | Simulation of the DC-DC topology - Duty cycle step 107                           |

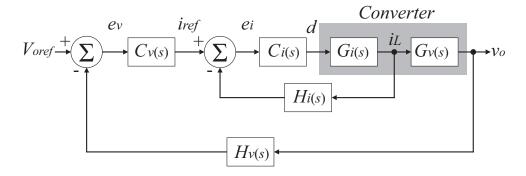

| Figure 77         | Controlled system block diagram107                                               |

| Figure 78         | Simulation of the DC-DC topology - Output load step disturbance 108              |

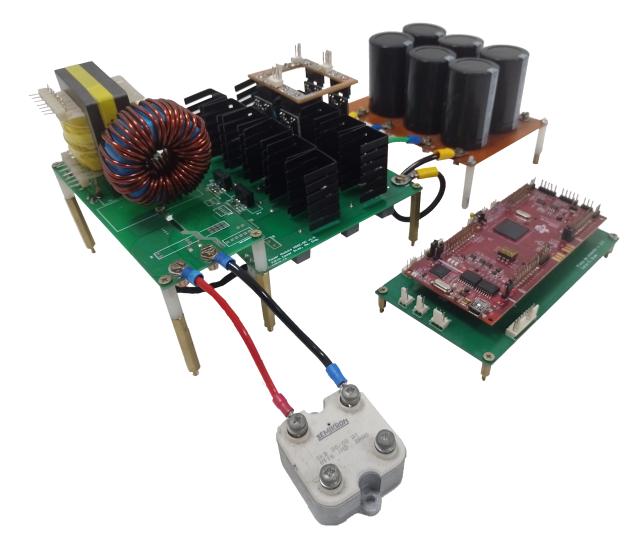

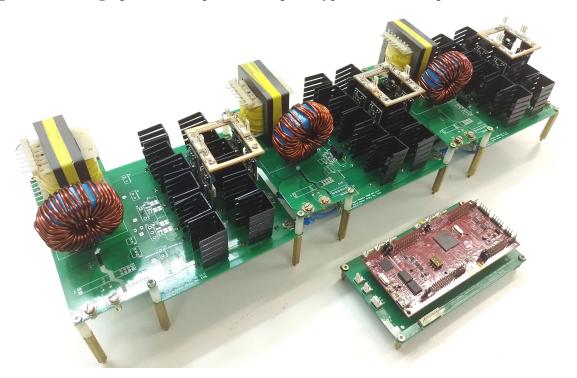

| Figure 79         | Picture of the proposed dc-dc converter                                          |

| Figure 80         | Experimental results for the dc-dc converter - Rated power operation110          |

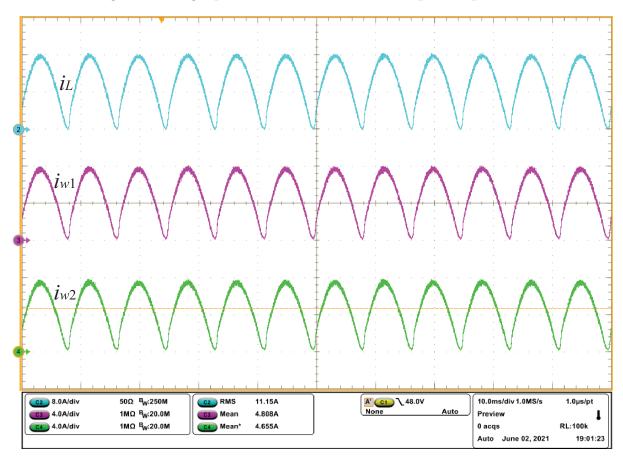

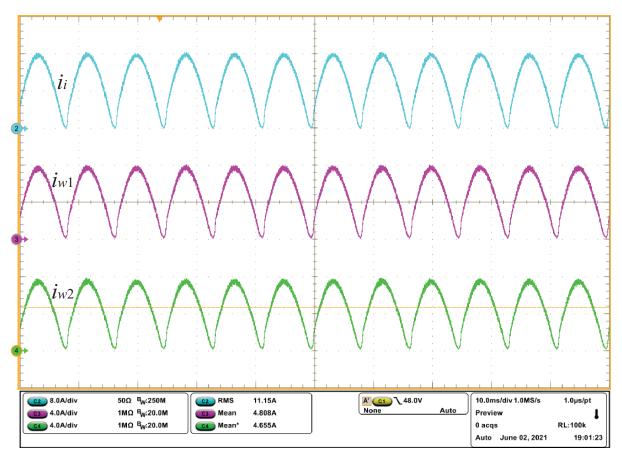

| Figure 81         | Experimental results for the dc-dc converter - Inductor and ICT current. $110$   |

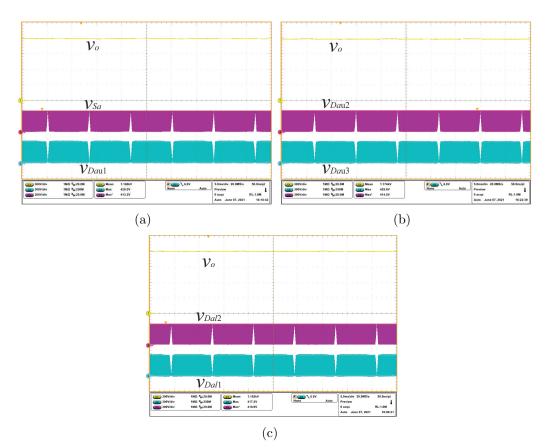

| Figure 82         | Experimental results for the dc-dc converter - Voltage on the switches 111       |

| Figure 83         | Voltage across the semiconductor devices: (a) Switch and upper diode             |

| $D_{au1}$ , (b) u | pper diodes $D_{bu2}$ and $D_{au3}$ and (c) lower diodes $D_{al1}$ and $D_{al2}$ |

| -                 | Experimental results for the dc-dc converter - Current in the cell capaci-       |

| tors              |                                                                                  |

| Figure 85         | Experimental results for the dc-dc converter - Load step                         |

| Figure 86         | Experimental results for the dc-dc converter - Efficiency curves for a 1200      |

| -                 | oltage                                                                           |

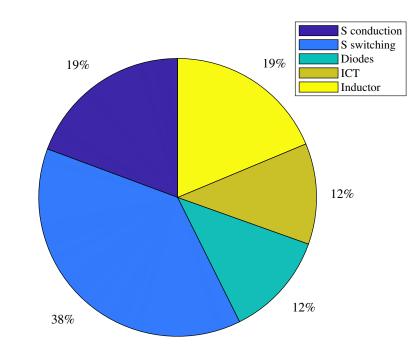

| Figure 87         | Loss breakdown for the dc-dc converter                                           |

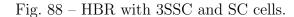

| Figure 88         | HBR with 3SSC and SC cells 117                                                   |

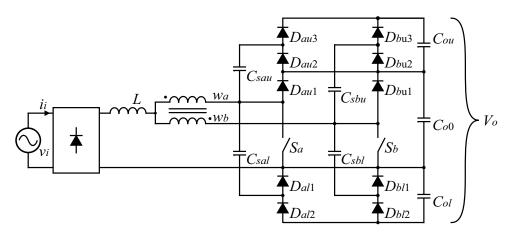

| Figure 89         | Controller diagram for the single-phase rectifier 118                            |

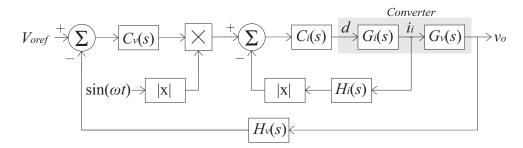

| Figure 90         | Main waveforms of the HBR with 4SSC and SC cells                                 |

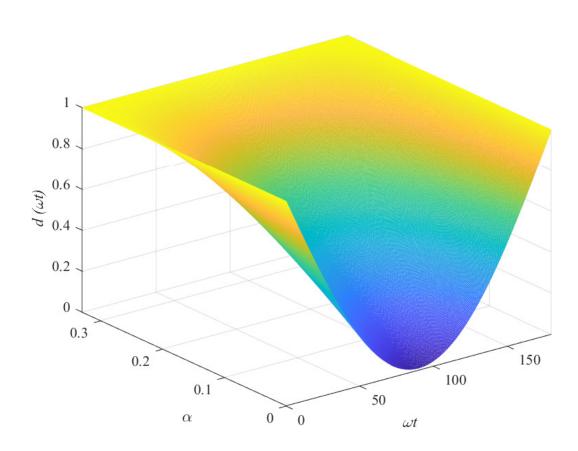

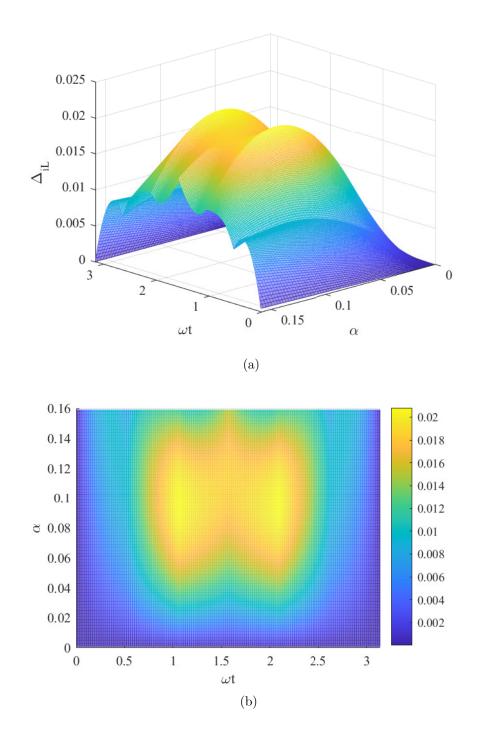

| Figure 91         | HBR duty cycle as a function of $\alpha$ and $\omega t120$                       |

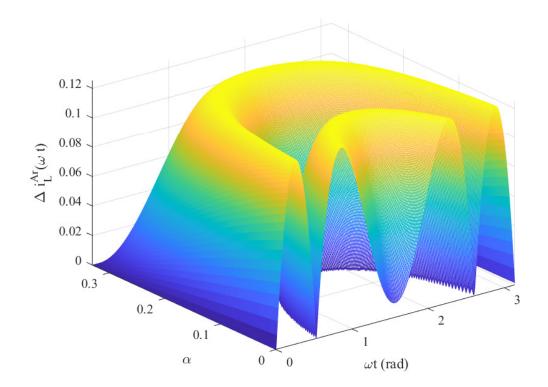

| Figure 92         | Normalized input current ripple                                                  |

| Figure 93         | Equivalent circuit of the converter output                                       |

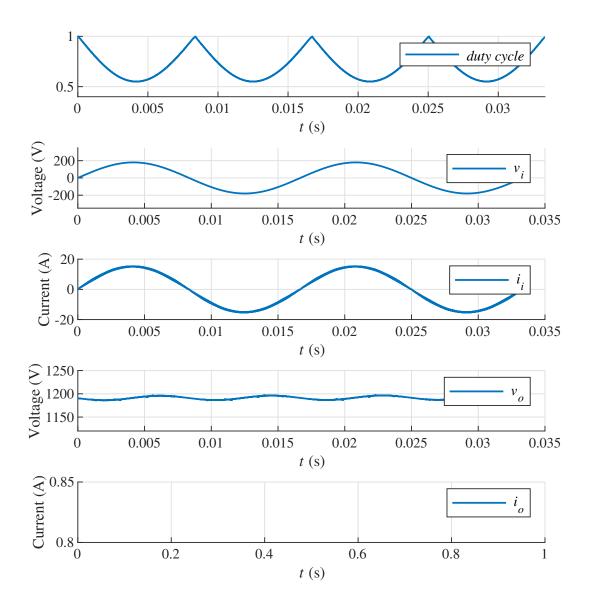

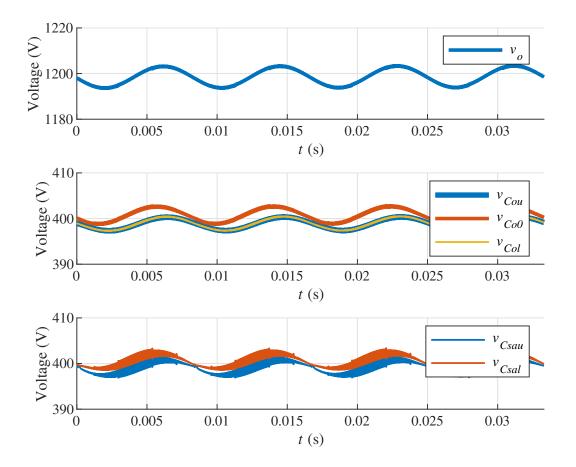

| Figure 94         | Simulation results of the single-phase ac-dc topology - Rated power126           |

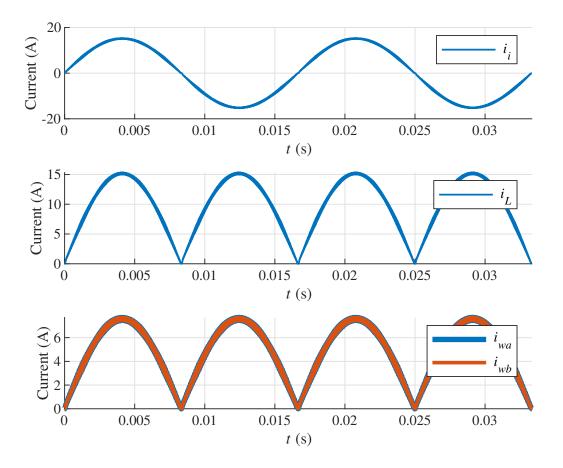

| Figure 95         | Simulation results of the single-phase ac-dc topology - Current in the           |

| inductor and MIA 127                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------|

| Figure 96 Simulation results of the single-phase ac-dc topology - Voltage across the capacitors of leg $a$ and output capacitors |

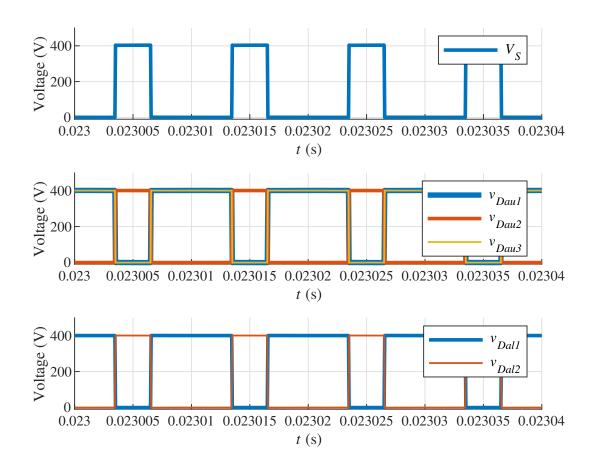

| Figure 97 Simulation results of the single-phase ac-dc topology - Voltage stress across                                          |

| the switch and diodes of leg $a$                                                                                                 |

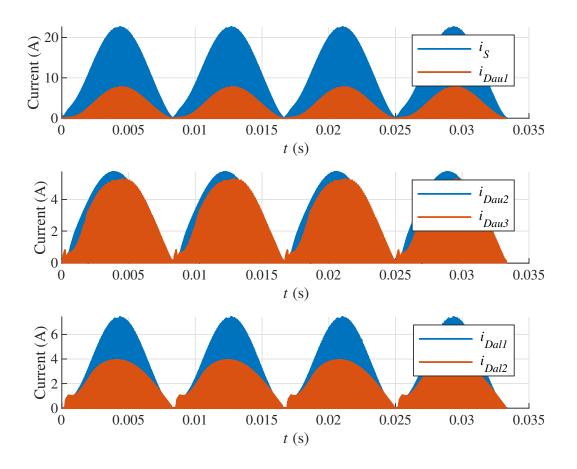

| Figure 98 Simulation results of the single-phase AC-DC topology - Current stress in                                              |

| the switch and diodes of leg <i>a</i> during the grid period130                                                                  |

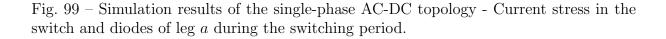

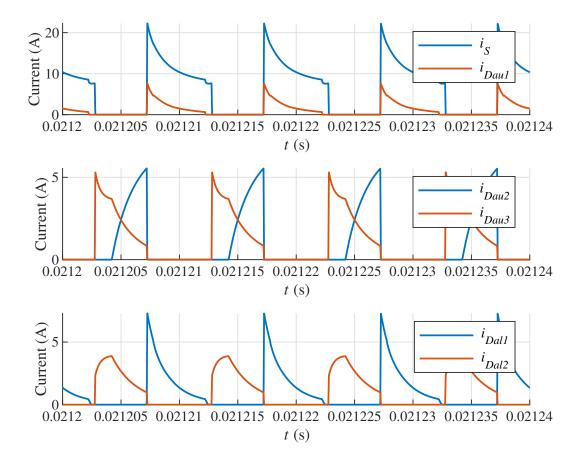

| Figure 99 Simulation results of the single-phase AC-DC topology - Current stress in                                              |

| the switch and diodes of leg <i>a</i> during the switching period                                                                |

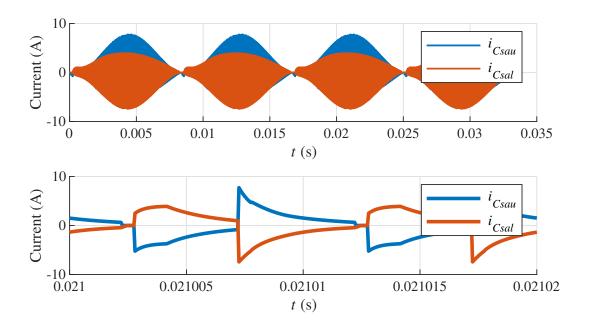

| Figure 100 Simulation results of the single-phase AC-DC topology - Current in the cell capacitors of leg <i>a</i>                |

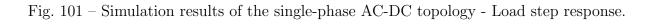

| Figure 101 Simulation results of the single-phase AC-DC topology - Load step re-                                                 |

| sponse                                                                                                                           |

| Figure 102 Single-phase HBR experimental prototype                                                                               |

| Figure 103 Single-phase ac-dc converter: Rated power operation                                                                   |

| Figure 104 Single-phase ac-dc converter: Inductor current and current sharing in the                                             |

| ICT                                                                                                                              |

| Figure 105 Voltage across the semiconductor devices of the single-phase ac-dc con-                                               |

| verter: (a) Switch and upper diode $D_{au1}$ , (b) upper diodes $D_{bu2}$ and $D_{au3}$ and (c)                                  |

| lower diodes $D_{al1}$ and $D_{al2}$                                                                                             |

| Figure 106 Single-phase ac-dc converter: Inductor current and current in the switched                                            |

| capacitors                                                                                                                       |

| Figure 107 Single-phase ac-dc converter: Load step                                                                               |

| Figure 108 Single-phase ac-dc converter: Efficiency curve                                                                        |

| Figure 109 Single-phase ac-dc converter: Loss breakdown                                                                          |

| Figure 110 Single-phase ac-dc converter: Harmonic content                                                                        |

| Figure 111 Three-phase HBR with 3SSC and SC cells                                                                                |

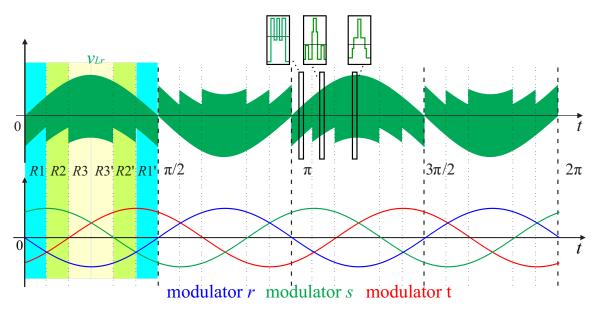

| Figure 112 Modulation scheme of the proposed three-phase rectifier                                                               |

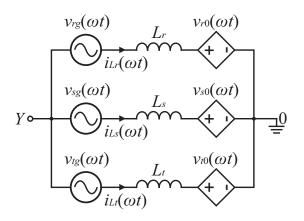

| Figure 113 Equivalent circuit of the proposed three-phase rectifier                                                              |

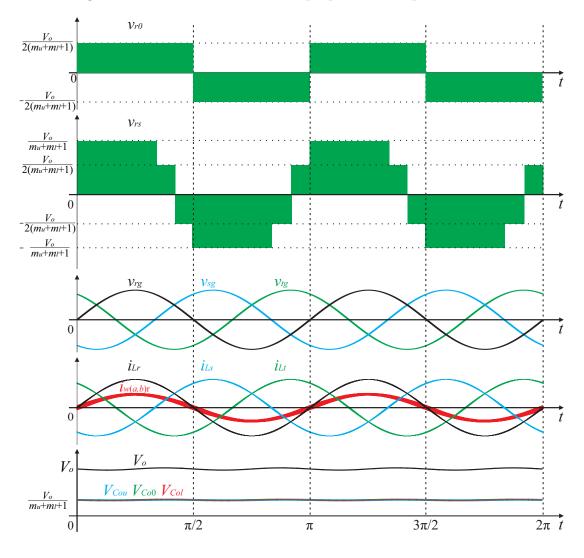

| Figure 114 Main waveforms of the proposed three-phase rectifier                                                                  |

| Figure 115 Equivalent circuits for the states of a single phase of the three-phase circuit:                                      |

| (a) State 1, (b) State 2, (c) State 3                                                                                            |

| Figure 116 Simplified equivalent circuit of the proposed three-phase rectifier 146                                               |

| Figure 117 Voltage across an inductor of the proposed three-phase rectifier                                                      |

| Figure 118 Variation of the input current ripple in the three-phase rectifier as a func-                                         |

| tion of the modulation index                                                                                                     |

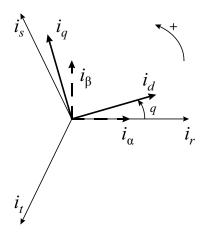

| Figure 119 Current vectors in <i>abc</i> and $\alpha\beta$ rotating orthogonal reference frame and                               |

| dq0 synchronous reference frame [123]                                                                                            |

| Figure 120 Equivalent output capacitance for the three-phase rectifier                                                           |

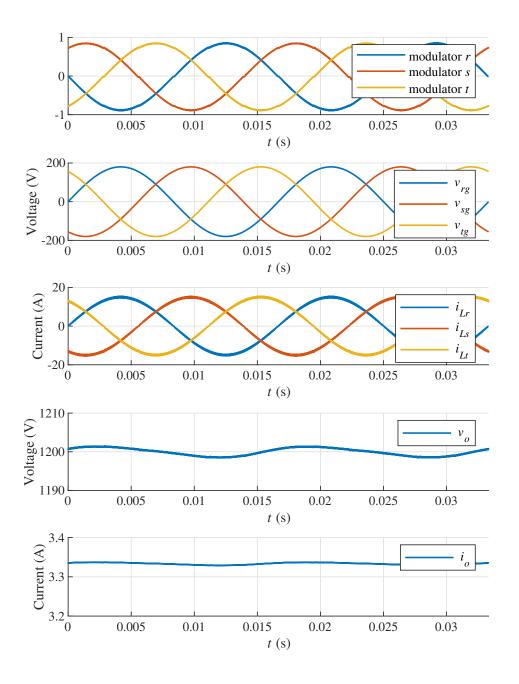

| Figure 121 Simulation results of the three-phase AC-DC topology - Rated power156                                                 |

| Figure 122 Simulation results of the three-phase ac-dc topology - Phase and line                                                 |

| voltages and current in the inductor and ICT                                                                                     |

| Figure 123 Simulation results of the three-phase AC-DC topology - Voltage across                                                 |

| the capacitors of leg $a$                                                                               | 158 |

|---------------------------------------------------------------------------------------------------------|-----|

| Figure 124 Simulation results of the three-phase AC-DC topology - Voltage stress                        |     |

| across the switch and diodes of leg $a$                                                                 |     |

| Figure 125 Simulation results of the three-phase AC-DC topology - Current stress in                     |     |

| the switch and diodes of leg $a$ during the grid period                                                 |     |

| Figure 126 Simulation results of the three-phase AC-DC topology - Current stress in                     |     |

| the switch and diodes of leg $a$ during the switching period                                            | 161 |

| Figure 127 Simulation results of the three-phase AC-DC topology - Current in the                        |     |

| cell capacitors of leg a                                                                                | 162 |

| Figure 128 Block diagram of the three-phase controller                                                  | 162 |

| Figure 129 Simulation results of the three-phase AC-DC topology - Load step re-                         |     |

| sponse                                                                                                  |     |

| Figure 130 Photograph of the experimental prototype of the three-phase ac-dc con-                       |     |

| verter                                                                                                  |     |

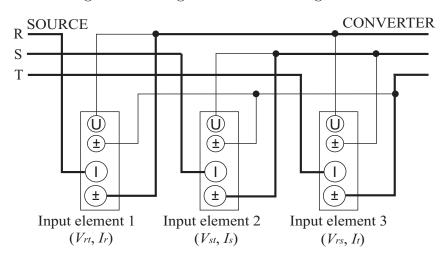

| Figure 131 Yokogawa WT1800 wiring scheme                                                                | 165 |

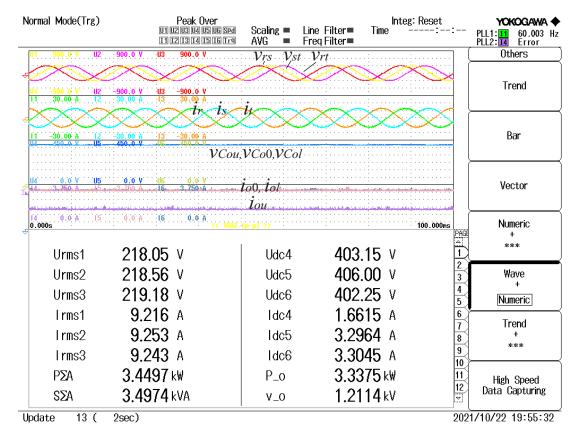

| Figure 132 Waveforms at rated power level: window1: $v_{rt}$ , $v_{st}$ and $v_{rt}$ ; window2: $i_r$ , |     |

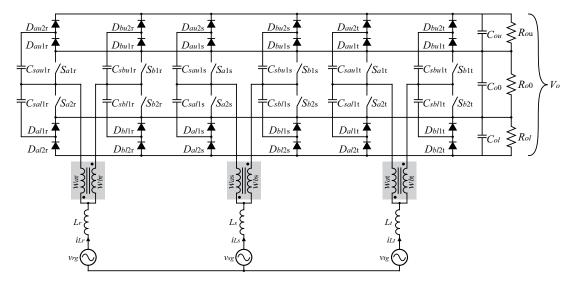

| $i_s$ and $i_t$ and window 3: $V_{Cou}$ , $V_{Co0}$ , $V_{Col}$ and $I_o$                               | 165 |

| Figure 133 Current sharing in the ICT in phase r                                                        | 166 |

| Figure 134 Voltage across the semiconductor devices of the three-phase ac-dc con-                       |     |

| verter and output voltage: (a) Switches $S_{a1r}$ and $S_{a2r}$ , (b) upper diodes $D_{bu2r}$ and       |     |

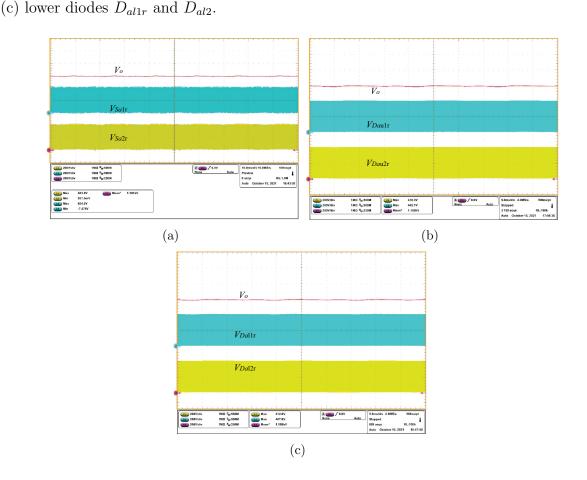

| $D_{au3r}$ and (c) lower diodes $D_{al1r}$ and $D_{al2}$                                                | 167 |

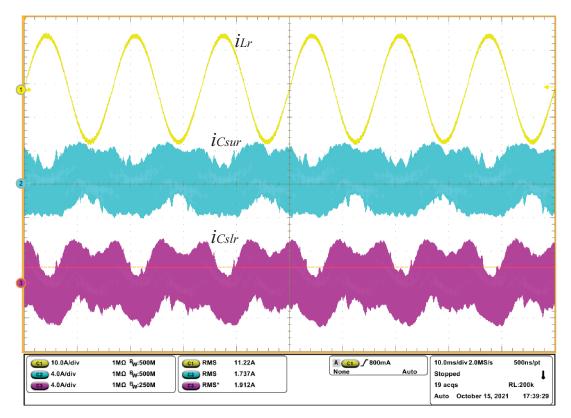

| Figure 135 Current in the input inductor $L_R$ and cell capacitors $C_{sur}$ and $C_{slr}$              | 168 |

| Figure 136 Diagram of the tested converter with the load shared between the output                      |     |

| capacitors                                                                                              |     |

| Figure 137 Three-phase ac-dc converter with balanced loads shared between the out-                      |     |

| put capacitors                                                                                          | 169 |

| Figure 138 Three-phase ac-dc converter with unbalanced loads shared between the                         |     |

| output capacitors                                                                                       | 170 |

| Figure 139 Load step applied to the output of the three-phase rectifier                                 | 171 |

| Figure 140 three-phase ac-dc converter with unbalanced loads shared between the                         |     |

| output capacitors                                                                                       | 171 |

| Figure 141 Harmonic spectrum of the three-phase ac-dc converter                                         | 172 |

| Figure 142 Efficiency curve of the three-phase ac-dc converter                                          | 172 |

| Figure 143 Loss breakdown of the three-phase ac-dc converter                                            | 173 |

| Figure 144 Magnetic circuit of the three-phase ICT                                                      |     |

| - •                                                                                                     |     |

# LIST OF TABLES

| Table 1 | Specifications of the ladder simulated circuits        | 82 |

|---------|--------------------------------------------------------|----|

| Table 2 | Topological states of the 3SSC                         | 87 |

| Table 3 | Specifications of the proposed DC-DC converter1        | 02 |

| Table 4 | Specifications of the proposed single-phase rectifier  | 25 |

| Table 5 | Phase voltages for the states in a single phase 1      | 46 |

| Table 6 | Specifications of the proposed three-phase rectifier 1 | 55 |

# LIST OF ABBREVIATIONS

| AC            | Alternate Current                                  | 34  |

|---------------|----------------------------------------------------|-----|

| DC            | Direct Current                                     | 34  |

| EMI           | Electromagnetic Interference                       | 34  |

| PCC           | Point of common coupling                           | 34  |

| PFC           | Power Factor Correction                            | 34  |

| IEEE          | Institute of Electrical and Electronics Engineers  | 34  |

| IEC           | International Electrotechnical Commission          | 34  |

| SCR           | Silicon controlled rectifier                       | 36  |

| MSSC          | Multistate switching cell                          | 37  |

| $\mathbf{SC}$ | Switched capacitor                                 | 37  |

| PWM           | Pulse width modulation                             | 39  |

| NPC           | Neutral-Point-Clamped                              | 41  |

| CW            | Cockcroft-Walton                                   | 44  |

| HBC           | Hybrid boost converter                             | 47  |

| HBR           | Hybrid Boost Rectifier                             | 48  |

| DCM           | Continuous conduction mode                         | 50  |

| DCM           | Discontinuous conduction mode                      | 50  |

| SEPIC         | Single-ended primary inductance converter          | 50  |

| CC            | Complete charge                                    | 68  |

| PC            | Partial charge                                     | 68  |

| NC            | No charge                                          | 68  |

| ESR           | Equivalent series resistance                       | 74  |

| ICT           | Intercell transformer                              | 85  |

| 3SSC          | Three-state switching cell with switched capacitor | 86  |

| 3SSC          | Three-state switching cell                         | 86  |

| RMS           | Root mean square                                   | 96  |

| PLL           | Phase-locked loop                                  | 151 |

|               |                                                    |     |

# LIST OF SYMBOLS

| $C_s$        | SC cell capacitor                                             | 67 |

|--------------|---------------------------------------------------------------|----|

| $V_i$        | Input voltage                                                 | 67 |

| $C_o$        | Output capacitor                                              | 68 |

| $V_o$        | Output voltage                                                | 68 |

| $R_{eq}$     | Equivalent resistance                                         | 69 |

| $C_{s_{kN}}$ | Switched-capacitor cell capacitance in leg $k$ and cell $N$   | 70 |

| $C_{o_N}$    | Output capacitance N                                          | 70 |

| $q_C^{st1}$  | Capacitor charge in the first operational stage               | 71 |

| $q_C^{st2}$  | Capacitor charge in the second operational stage              | 71 |

| $S_j$        | Boost switch, $j = 1, 2$                                      | 71 |

| $S_{nj}$     | Switch in lower SC cell, $j = 1, 2$                           | 71 |

| $S_{pj}$     | Switch in upper SC cell, $j = 1, 2$                           | 71 |

| $C_{opj}$    | Upper output capacitor, $j = 1, 2$                            | 71 |

| $C_{onj}$    | Lower output capacitor, $j = 1, 2$                            | 71 |

| $C_{spj}$    | Upper cell capacitor, $j = 1, 2$                              | 71 |

| $C_{snj}$    | Lower cell capacitor, $j = 1, 2, \dots, j$                    | 71 |

| $a_C$        | Capacitor multiplier charge vector                            | 72 |

| $q_{Csu}$    | Upper cell capacitor charge                                   | 72 |

| $q_{Csl}$    | Lower cell capacitor charge                                   | 72 |

| $q_{Cou}$    | Upper output capacitor charge                                 | 72 |

| $q_{Col}$    | Lower output capacitor charge                                 |    |

| $q_o$        | Output load charge                                            | 72 |

| $C_{lsc}$    |                                                               |    |

| $V_{o,SSL}$  | SSL output voltage                                            | 73 |

|              | $_{D}$ SSL equivalent resistance                              | 73 |

| $a_{Rs}$     | Switch resistances multiplier charge vector                   | 74 |

| $a_{Rc}$     | Capacitor resistances multiplier charge vector                | 74 |

| $q_{Rs}$     | Switch resistance charge                                      | 74 |

| $q_{Rc}$     | Capacitor resistance charge                                   | 74 |

| $v_{Rs}$     | On voltage across the switch                                  | 74 |

| $q_{Rc}$     | Voltage across the capacitor ESR                              | 74 |

| $R_{slsc}$   | Vector with switch resistance values of the ladder SC cell    | 74 |

| $R_{clsc}$   | Vector with capacitor resistance values of the ladder SC cell | 74 |

| $D_{slsc}$   | Vector with duty cycle values of the ladder SC cell switches  | 74 |

|              | FSL output voltage                                            | 75 |

| <i>,</i>     | $_{L}$ FSL equivalent resistance                              | 75 |

| $R_o$        | Output resistance                                             | 77 |

| $\eta_{SC}$      | efficiency of a switched capacitor cell                                         | 77  |

|------------------|---------------------------------------------------------------------------------|-----|

| $M_{ij}$         | Mutual inductance between phases $i$ and $j$                                    | 85  |

| $L_{i,j}$        | Self inductance of the ICT                                                      | 85  |

| n                | Number of phases in the ICT                                                     | 85  |

| $k_{ICT}$        | Coupling factor of the ICT                                                      | 85  |

| $S_i$            | Switch in leg $j, i = a, b, c$                                                  | 88  |

| $D_{iuj}$        | Upper diode number $j$ in leg $i, k = a, b, c$                                  | 88  |

| $D_{ilj}$        | Lower diode number $j$ in leg $i, k = a, b, c$                                  | 88  |

| $w_i$            | Interphase transformer winding connected to leg $i, k = a, b, c$                | 88  |

| $V_D$            | Diode reverse voltage                                                           | 95  |

| $V_D$            | MOSFET voltage                                                                  | 95  |

| $u_i$            | Switch function of the switch $S_i$                                             | 96  |

| $V_{wICT}$       | Vector of the voltages across the windings of the multi-interphase transformer  | 98  |

| $M_{wICT}$       | Inductance matrix of the multi-interphase transformer                           | 98  |

| $I_{wICT}$       | Vector of the currents through the windings of the multi-interphase transformer | 98  |

| $J_k$            | $k \times k$ matrix of ones                                                     | 98  |

| $I_n$            | Identity matrix of size <i>n</i>                                                | 98  |

| $D_{MSS}$        | $_{C}$ Duty cycle vector of the MSSC                                            | 98  |

| $M_{wsym}$       | <sup>1</sup> Inductance matrix for a symmetrical interphase transformer         | 99  |

| x                | State vector                                                                    | 101 |

| y                | Output vector                                                                   | 101 |

| u                | Input vector                                                                    | 101 |

| A                | State matrix                                                                    | 101 |

| В                | Input matrix                                                                    | 101 |

| E                | Output matrix                                                                   | 101 |

| F                | Feedforward matrix                                                              | 101 |

| $v_{\varphi 0}$  | Phase voltage at the PCC                                                        | 101 |

| $f_g$            | Grid frequency                                                                  | 117 |

| $\alpha$         | Relative modulation index                                                       | 119 |

| $\omega t$       | Grid angle                                                                      | 119 |

| $i_x$            | Current delivered from the converter to the output                              | 122 |

| $X_{Co^{eq}}$    | Equivalent output capacitor reactance                                           | 122 |

| $I_{Copp}$       | Equivalent output capacitor peak-to-peak current                                | 122 |

| $\Delta V_o$     | Output voltage ripple                                                           | 122 |

| $T_g$            | Grid period                                                                     | 123 |

| $S_{ij\varphi}$  | Switch number $n$ in leg $k$ of phase $\Phi$                                    | 143 |

| $v_{\varphi 0}$  | Phase voltage at the PCC                                                        | 145 |

| $d_{\varphi}$    | Duty cycle of the lower switches in phase $\varphi$                             | 146 |

| $v_{L\varphi}$   | Inductor voltage in phase $\varphi$                                             | 147 |

| $v_{L\varphi g}$ | Grid phase voltage in phase $\varphi$                                           | 147 |

| $v_{Y0}$   | Common-mode voltage                                                          | 147 |

|------------|------------------------------------------------------------------------------|-----|

| $\alpha_r$ | transition value that determines which operation point has the highest input |     |

| ripple     | in the three-phase rectifier                                                 | 149 |

| $i_d$      | Direct current                                                               | 150 |

| $i_q$      | Quadrature current                                                           | 150 |

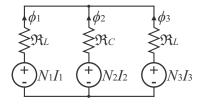

| $\Re_C$    | Central leg reluctance of a three-phase transformer                          | 192 |

| $\Re_L$    | Lateral leg reluctance of a three-phase transformer                          | 192 |

| $l_{gC}$   | Central leg air-gap of a three-phase transformer                             | 192 |

| $l_{gL}$   | Lateral leg air-gap of a three-phase transformer                             | 192 |

| $A_e$      | Effective area of a transformer                                              | 192 |

| $\mu_0$    | vacuum magnetic permeability                                                 | 192 |

| $\phi_C$   | Magnetic flux in the central leg of a three-phase transformer                | 192 |

| $\phi_L$   | Magnetic flux in the lateral leg of a three-phase transformer                | 192 |

# CONTENTS

| 1 I        | NTRODUCTION                                         | 33  |

|------------|-----------------------------------------------------|-----|

| 1.1        | CONTEXTUALIZATION                                   | 33  |

| 1.2        | LITERATURE REVIEW: MULTISTATE SWITCHING CELLS       | 38  |

| 1.3        | LITERATURE REVIEW: SWITCHED CAPACITOR CONVERTERS    | 44  |

| 1.4        | PROPOSED TOPOLOGIES                                 | 54  |

| 1.5        | STRUCTURE OF THE THESIS                             | 65  |

| 2 S        | SWITCHED CAPACITOR CELLS                            | 67  |

| 2.1        | OPERATION PRINCIPLE                                 | 67  |

| 2.2        | CHARGE MODES                                        | 68  |

| 2.3        | DESIGN METHODOLOGY                                  | 69  |

| 2.3        | .1 Slow switching limit (SSL)                       | 72  |

| 2.3        | .2 Fast switching limit (FSL)                       | 73  |

| <b>2.3</b> | .3 Total equivalent resistance                      | 75  |

| <b>2.3</b> | .4 Generalization                                   | 77  |

| 2.4        | SUMMARY                                             | 83  |

| 3 F        | HYBRID BOOST DC-DC CONVERTER WITH MSSC AND SC CELLS | 85  |

| 3.1        | MULTISTATE SWITCHING CELL                           | 85  |

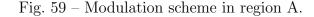

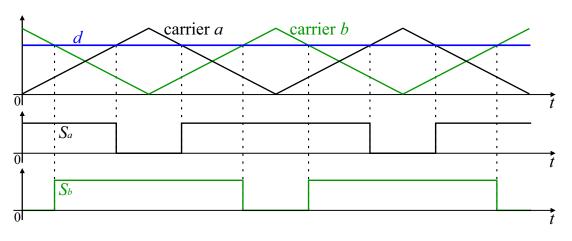

| 3.2        | REGION A $(D < 1/2)$                                | 87  |

| 3.2        | .1 Operation principle                              | 87  |

| 3.2        | .2 Static gain                                      | 89  |

| 3.2        | .3 Inductor current ripple                          | 90  |

| 3.3        | REGION B $(D > 1/2)$                                | 91  |

|            | .1 Operation principle                              | 91  |

| 3.3.       | .2 Static gain                                      | 93  |

| 3.3.       | .3 Inductor current ripple                          | 94  |

| 3.4        | VOLTAGE STRESS                                      | 95  |

| 3.5        | CURRENT STRESS                                      | 95  |

| 3.6        | MSSC DYNAMIC ANALYSIS                               | 96  |

| 3.7        | OUTPUT VOLTAGE DYNAMIC ANALYSIS                     | 99  |

| 3.8        | SIMULATION RESULTS 1                                |     |

|            | EXPERIMENTAL RESULTS 1                              |     |

|            | ) SUMMARY 1                                         | 114 |

|            | SINGLE-PHASE HYBRID BOOST RECTIFIER WITH MSSC AND   |     |

|            | SC CELLS 1                                          |     |

|            | DUTY CYCLE 1                                        |     |

|            | INPUT CURRENT RIPPLE 1                              |     |

|            | OUTPUT CAPACITORS 1                                 |     |

|            | OUTPUT VOLTAGE DYNAMIC ANALYSIS 1                   | -   |

|            | VOLTAGE STRESS AND CURRENT STRESS 1                 |     |

| 4.6        | SIMULATION RESULTS                                  |     |

|            | EXPERIMENTAL RESULTS 1                              |     |

|            | SUMMARY 1                                           | 142 |

|            | THREE-PHASE HYBRID BOOST RECTIFIER WITH MSSC AND    |     |

|            | SC CELLS                                            |     |

| 5.1        | DUTY CYCLE 1                                        | 145 |

| 5.2 | INDUCTOR CURRENT RIPPLE                                     | 147 |

|-----|-------------------------------------------------------------|-----|

| 5.3 | CAPACITORS                                                  | 150 |

| 5.4 | DYNAMIC ANALYSIS                                            | 150 |

| 5.5 | OUTPUT DYNAMIC ANALYSIS                                     | 153 |

| 5.6 | VOLTAGE AND CURRENT STRESS                                  | 154 |

| 5.7 | SIMULATION RESULTS                                          | 155 |

| 5.8 | EXPERIMENTAL RESULTS                                        | 164 |

|     | SUMMARY                                                     |     |

| 6 C | CONCLUSIONS                                                 | 177 |

| 6.1 | FUTURE WORKS                                                | 178 |

| Ref | erences                                                     | 179 |

| AP  | PENDIX A – 4SSC implementation issues with commercial cores | 191 |

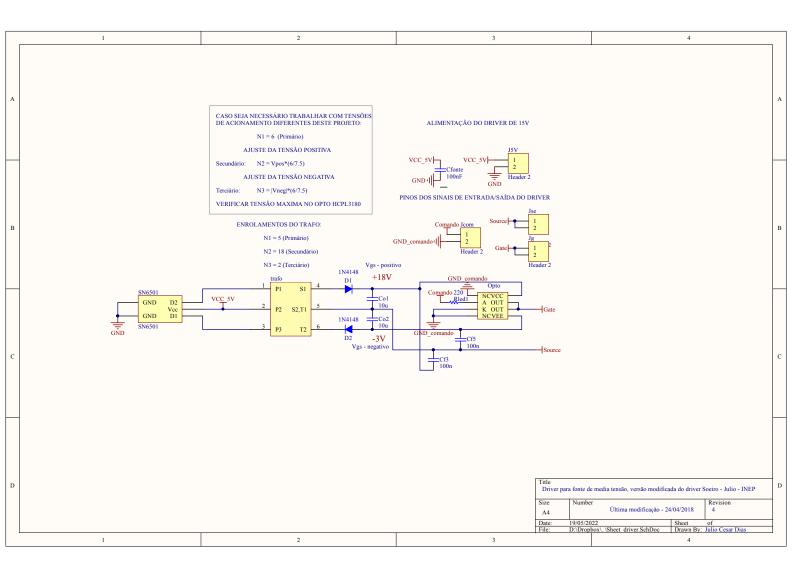

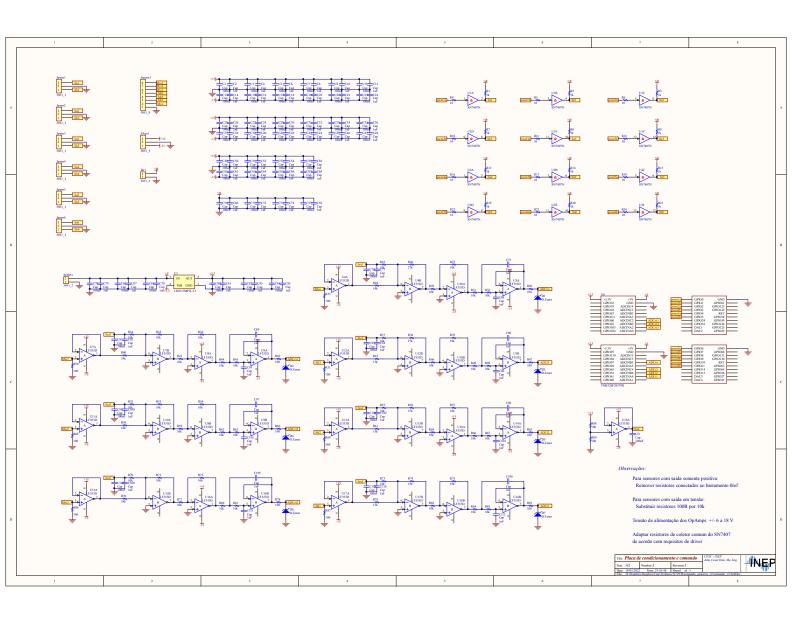

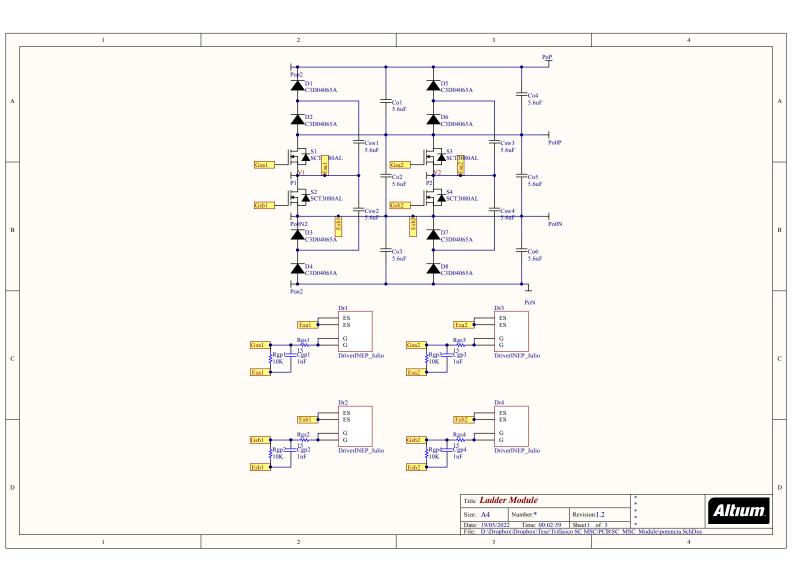

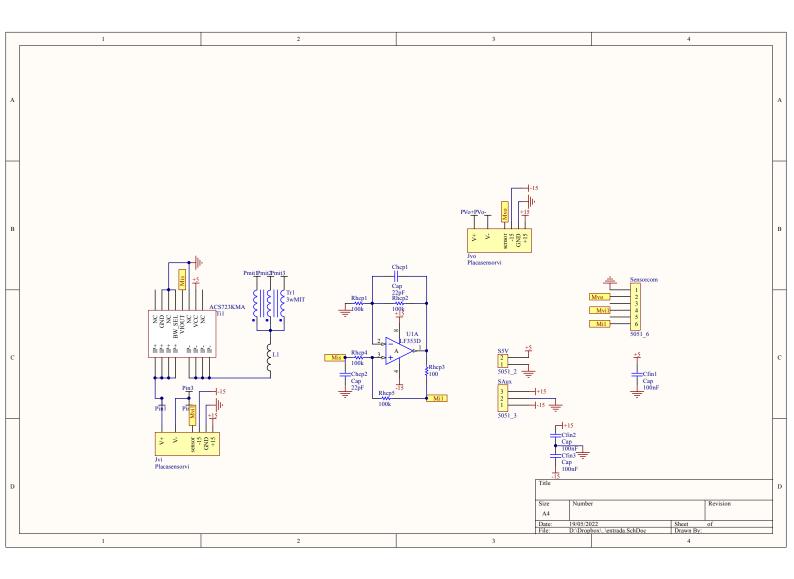

| AP  | PENDIX B – Schematic Diagrams                               | 197 |

#### **1 INTRODUCTION**

#### 1.1 CONTEXTUALIZATION

High voltage levels can be beneficial and necessary for several uses, since it is used to reduce the power losses and volume of conductors due to the current level reduction. Some applications, such as X-ray, air filters and plasma sources need high voltages to operate properly, and to generate these higher voltage levels there is a need for power supplies capable to withstand the high voltages on their semiconductor devices. There are several other applications today that require these supplies, such as pulsed lasers, telecommunication supplies, electric vehicles and machine drives [1–6].

Step-up ac-dc converters are usually required in these types of applications, which aim to rectify and increase the voltage levels from the utility grid or to lift the voltage levels from sources with even lower voltage outputs (e.g., wind energy conversion systems, photovoltaic modules, fuel cells. The voltage from these types of sources can be increased to inject the extracted energy into the grid or to supply equipment [7–11]. However, there are many limitations regarding the voltage and current stress in the devices used in these power supplies.

Although the power electronics field has evolved substantially over the last decades, more studies are yet needed to improve the efficiency, cost, weight and volume and to overcome current limitations of energy conversion systems. Power electronics is an important component in many applications and its research is necessary due to the rising demand of consumer electronics, automation, and new problems that have arised in the last years with the rise of blockchain technology, cryptocurrency mining, electromobility and the increased teleworking rates during the COVID-19 pandemic. All of these factors have caused a higher demand of electrical energy, which requires more efficient conversion systems to reduce costs, environmental impact and improve power quality [12–14].

As new semiconductor devices become available with the emergence of wide band gap technologies, the research for new structures can help solving issues in power conversion. In applications that require high voltage rates, there are still several issues with conventional conversion techniques, such as maximum voltage restrictions of electronic devices and parasitic elements, which limit the conversion ratio of power converters and reduce their efficiency as the power and voltage rates increase. These restrictions call for the research of new structures that do not need to rely on semiconductors devices with high breakdown voltages, which are expensive devices with slow dynamics and are not commercially available at a large scale. The slow dynamics of these devices require bulkier passive filters, which increase the costs of the converters. Furthermore, these devices have high conduction losses that decrease the conversion ratio and efficiency of high voltage gain converters [1, 11, 15].

Power converters supplied by the grid or energy sources should have input currents with low harmonic distortion in order to avoid electromagnetic disturbances, reduce the non-active power content and avoid causing voltage distortions that may damage equipment that is connected to the same point of power delivery [point of common coupling (PCC)] [16–18]. Several systems are supplied by the utility grid or ac generators and, making it necessary to regulate the input current of the equipment in order to achieve near-unit power factor. Furthermore, it is essential that the converters input harmonic currents meet the requirements for harmonic control and recommended practices that are established by international standards and guidelines [19–21].

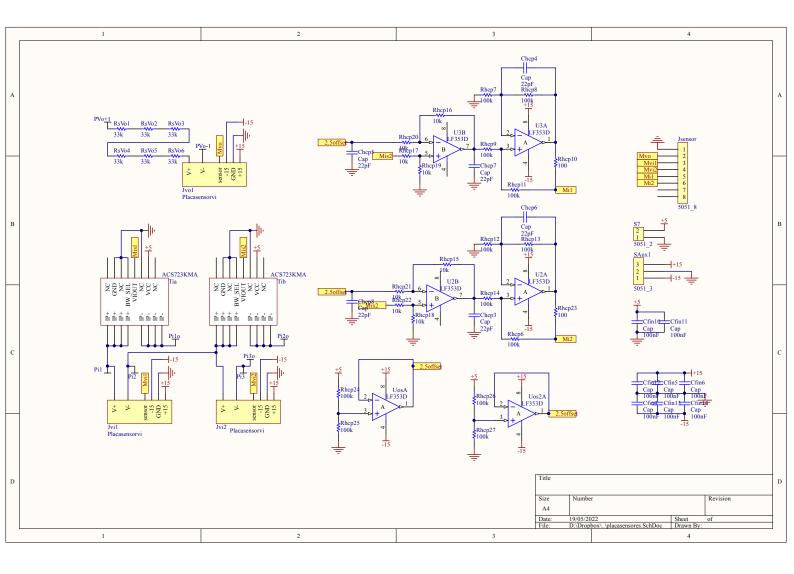

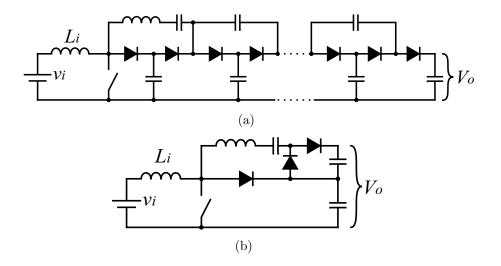

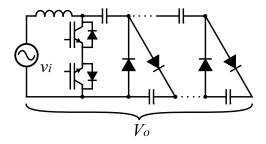

Fig. 1 – Boost PFC rectifier.

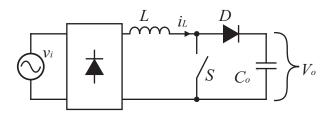

The input power factor of an equipment can be improved by using passive or active solutions. Although passive solutions are more robust, they require bulky and heavy passive devices for filtering the harmonic content. Besides, passive filters may be more expensive compared to active solutions due to the rising cost of copper and magnetic core material. One alternative is the boost converter with active power factor correction (PFC), shown in Fig. 1, which is a widespread active technique to achieve near-unit power factor. The main advantage of the boost rectifier compared to other basic converter topologies (buck, buck-boost) is its input inductor, which is designed to attenuate the switching frequency harmonic component from the input current. PFC rectifiers that operate in continuous conduction mode (CCM) are typically controlled with two cascaded loops, one inner input current loop with faster dynamics and an outer output voltage loop with slower dynamics (See Fig. 2). The outer loop generates a peak current reference which is multiplied by the phase of the input voltage, thus providing a rectified sinusoidal input current reference to the inner loop. The inner loop controls the input current according to the outer loop reference. Because the inner loop is designed with a much faster dynamic response than the outer loop, the dynamics of the inner loop can be ideally viewed by the outer loop as a static gain, thus the two loops can be controlled independently and the system transfer functions for each loop have a first order equivalent response. Since the PFC boost rectifier has a current-fed input, regulated output voltage, high input power factor and it can be controlled by linear methods, it is a very widespread topology that is suitable for several applications. However, due to its parasitic components and the voltage stress across the switches, it has limitations for high-gain applications. It is also not suitable for high-power applications, since they require power switches that are more expensive and have slower dynamics. Due to the switches slow dynamics, the switching frequency must be decreased in higher voltage or higher power applications, increasing the size and weight of the input filters [22-26].

For higher power levels, three-phase inputs are more adequate, since the current is shared between the phases. There are several configurations of the three-phase boost rectifier suitable for different input configurations. A simple solution is the three-phase extension of the single-phase boost rectifier, which is conceived by changing the input diode bridge (See Fig. 3). The input current in this converter is divided in the three-phase diode bridge. However, the boost converter switch and diode process all the output energy. Besides, the input currents presents low-frequency harmonic content, since the phase currents cannot be controlled individually [27–29].

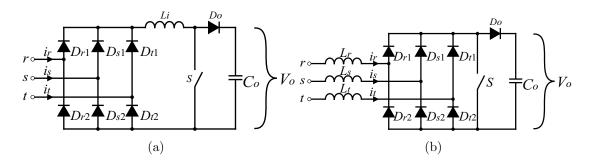

Fig. 3 – Three-phase boost rectifiers with diode bridge [29]: (a) inductor on the dc side, (b) inductors on the ac side.

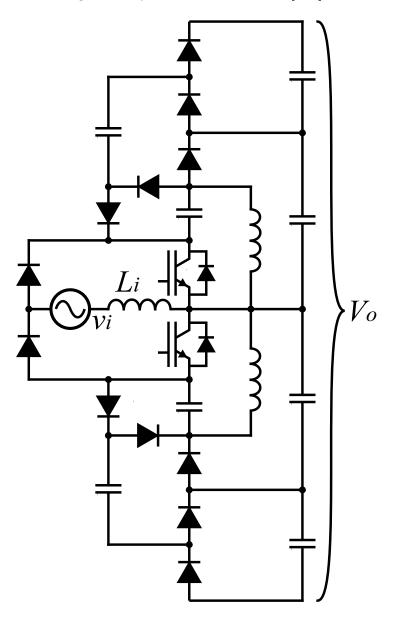

An alternative for reducing the current stress on the switches of the boost converter and controlling the input phase currents is the three-phase bidirectional boost rectifier, shown in Fig. 4. This converter enables the control of the input current within a sinusoidal shape in the three phases and divides the current stress in the switches. The control strategy of three-phase rectifiers is more complex than the single-phase, since the three phase currents cannot be controlled individually due to their coupling [29–32]. The threephase rectifier analysis will be addressed with more details in later chapters, since the new structures presented in this thesis are derived from this rectifier and the design methodology of the proposed rectifier is very similar to the conventional bidirectional boost rectifier.

Fig. 4 – Three-phase bidirectional boost rectifier [29].

The three-phase bidirectional rectifier has a higher voltage gain than the single-phase PFC boost converter and it can process higher current values, since the input power is divided between the three phases. However, there are still limitations due to the voltage stress on the devices (equal to the output voltage), which requires more expensive switches for higher output voltages. These switches are also slower and have higher conduction losses than switches designed for lower current levels. There are also limitations regarding the voltage gain due to parasitic elements, which require lower modulation index and affects the converter voltage regulation. As the voltage and power levels increase, the use of slower switches result in bulkier and heavier input passive filters [26, 33].

In cases where the switching frequency of the semiconductor devices is too low, the input current filter must also be designed for lower cutoff frequencies, which can result in phase-shifted currents due to the inductive reactance, therefore affecting the input power factor. There are some solutions to prevent this issue, which can be implemented in a passive or active way. A passive solution is the use of higher order filters with a higher cutoff frequency, which present faster dynamics and a higher high-frequency attenuation. However, these filters require more components and the higher order transfer function might increase the control complexity. Furthermore, in cases that the switching frequency is too low, the high-frequency attenuation might not be enough to meet the requirements of harmonic control guidelines [19–21].

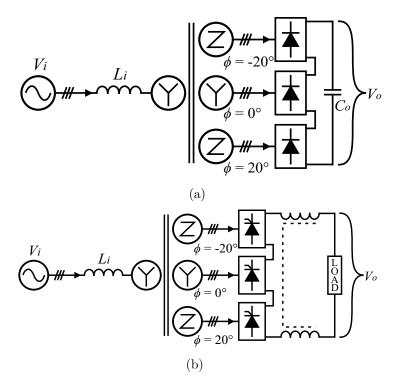

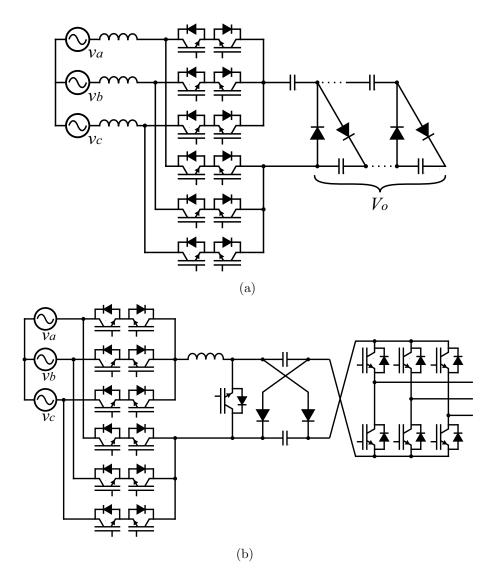

Improvements in the input power factor in applications that require higher voltage or power levels can be achieved with other more suitable topologies. An alternative is the use of multipulse rectifiers, which can be implemented with diode or SCR bridges (See Fig. 5). These rectifiers use transformers in configurations to phase-shift the voltage on the secondary windings, which result in an input current in the primary coil with lower harmonic content than the conventional six-pulse rectifier. The secondary windings of the transformers are connected to six-pulse rectifiers, which can be connected in a series association, thus providing a high voltage gain and reducing the voltage stress across the semiconductor. This solution is robust and capable of processing higher power levels, since it uses only diodes or SCRs as switching devices. However, the gain of the rectifier depends on the turn ratio of the transformer and the number of modules. A higher turn ratio affects the voltage stress on the switches and might require gate drivers with high voltage isolation for applications with SCR. The increased number of modules requires additional transformers and diodes or SCRs, which affects the size, cost and complexity of the converter. Other disadvantage is the use of low-frequency transformers, which must be designed in non-conventional configurations for phase-shifting the voltages on the secondary windings in applications were multiple pulses are used. Besides, the use of low frequency transformers increase significantly the weight and volume of the conversion system.

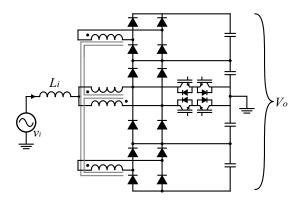

Low frequency input filters can be avoided by using different structures of switchedmode power supplies able of reducing the voltage stress on the switches, such as multilevel and multistage converters [1,34–37]. Multilevel rectifiers use multiple switch combinations to provide different voltage levels on the converter input, thus shaping the switched voltage after the input filter into a sinusoidal shape with lower harmonic content than the conventional two-level rectifiers. These rectifiers also allow the use lower voltage switches, which are less expensive and faster, thus reducing even more the size and weight of input filters. A major advantage of multilevel topologies is the voltage stress on the switches, which can be lower than the grid peak voltage, being useful structures for high and medium voltage applications. The main disadvantage of the multilevel converters is their complexity. These converters have a high number of controlled switches and require many isolated gate drivers. Furthermore, complex modulation schemes are required in some structures to balance the capacitor voltages, thus increasing computational effort and including elements that can fail and reduce the robustness of the converter [34–38]. Fig. 6 illustrates some multilevel rectifier topologies.

In this thesis a new alternative for higher voltage gain and power levels is proposed, which is a family of dc-dc and ac-dc converters based on the integration between switchedcapacitor (SC) and multistate switching cells (MSSC). Because these techniques are the main study subjects of this thesis, a more thorough literature review is presented with an

Fig. 5 – 18-pulse series-type rectifiers [34]: (a) diode bridge, (b) SCR bridge.

individual section for each one of them.

Fig. 6 – Multilevel three-phase rectifier topologies [36]: (a) Unidirectional five-level rectifier, (b) Five-level diode clamped rectifier, (c) Five-level flying-capacitor rectifier.

# 1.2 LITERATURE REVIEW: MULTISTATE SWITCHING CELLS

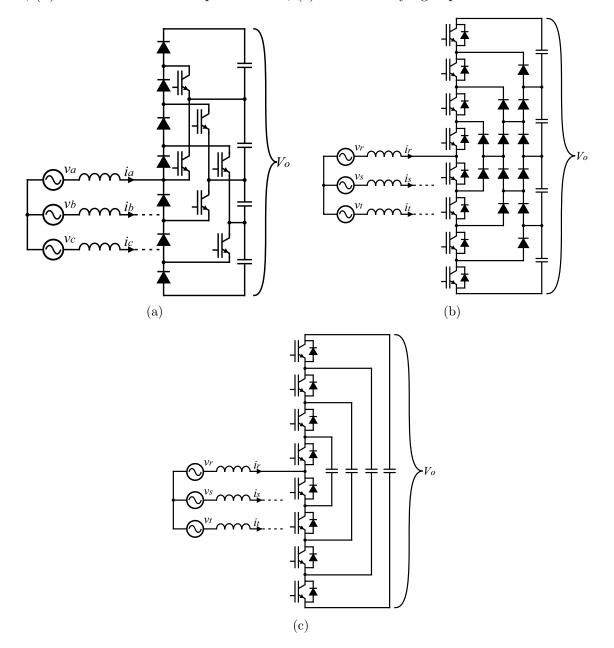

As mentioned previously, some common issues related to high power conversion are the current stress in the switches and low switching frequency, which can require bulky input filters. However, it is possible to process more power with a higher frequency by dividing the power between more converters or by dividing the current between more switches. Two techniques that have been often used in literature for this purpose are the interleaved converters and the MSSC, shown in Fig. 7.

In this thesis the MSSC will be studied due to the possibility of reducing the number of magnetic cores and increasing the number of voltage levels in the filter point of connection. This study, however, can be expanded into future works to cover interleaved

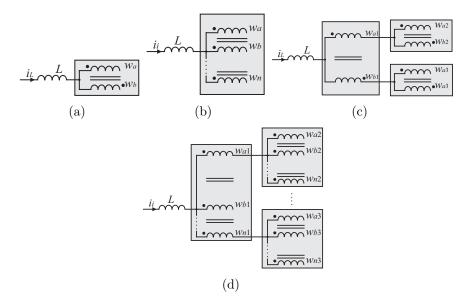

Fig. 7 – Current sharing techniques: (a) interleaved converter, (b) 3SSC, (c) MSSC.

topologies without major differences or increased complexity issues. The main purpose of this thesis is to introduce the concept of integrating MSSC with SC cells in ac-dc conversion.

Either the interleaved cell and the MSSC are controlled by phase-shifted PWM signals. The input current of the converter is the sum of the phase shifted currents of each winding, which results in a total input current with a fundamental frequency that is the switching frequency multiplied by the number of phase-shifted carrier waves. The operation principle of the MSSC will be described in chapter 3.

The use of the MSSC for dc-dc conversion was first presented in Brazilian literature by [39, 40], where variations of the three-state switching cell (3SSC) were integrated to the basic converter topologies. The 3SSC is based on the current-fed push-pull converter, which uses an isolated transformer with a center-tapped input. By removing the secondary winding of the push-pull transformer and connecting the windings to the output, the input current can be shared between the switches and the converter can operate as a conventional boost [41]. The use of integrated magnetics had been first proposed before in [42] for buck converters with MSSC and interphase transformers have also been used for harmonic current reduction in low frequency applications [43, 44]. The study of the interphase transformer for the 3SSC boost converter with two input sources had also been performed before in [45]. In [46] the work was extended for a generalization of the MSSC converters based on the study of the four-state cell basic topologies.

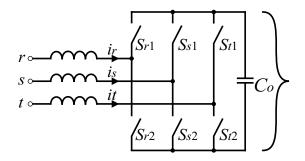

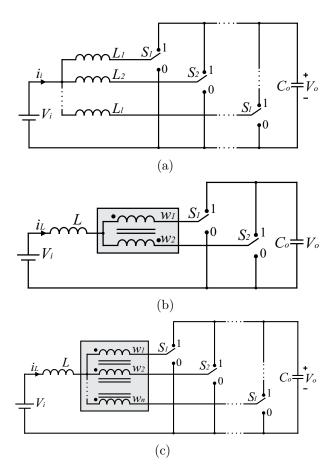

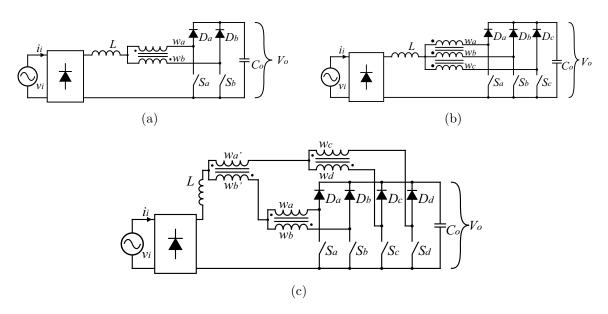

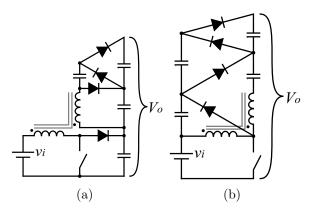

In [47] the use of the 3SSC in PFC rectifiers was proposed. The study was expanded in [48], covering 4SSC and 5SSC and proposing different methods for implementing the MSSC, as shown in Fig. 8. The circuit shown in Fig. 8 (c) suggests a different configuration that cascades the interphase transformers for more states. However, the use of cascaded coupled inductors for MSSC was proposed by [49] for ac-dc conversion. This configuration is practical for more states due to the constructive aspects of the interphase transformer, however, it lacks experimental verification.

Fig. 8 – Single-phase PFC rectifiers with MSC [48]: (a) 3SSC, (b) 4SSC, (c) 5SSC with cascaded interphase transformers.

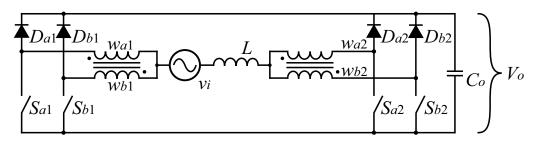

A bridgeless version of the 3SSC boost rectifier was proposed in [50]. The bridgeless version of the structure requires more semiconductor devices and magnetic elements than the conventional structure, as can be seen in Fig. 9. However, the current in the devices of the bridgeless version is divided between the legs, whereas in the bridged converter the input diode bridge must be designed for the total input current.

Fig. 9 – Single-phase bridgeless boost rectifier with 3SSC [50].

In [51] a T-Type 3SSC converter with high voltage gain was proposed. The converter provides high power factor, current sharing in the switches, low voltage stress and high voltage gain. However, it uses an isolated transformer to provide the high voltage gain.

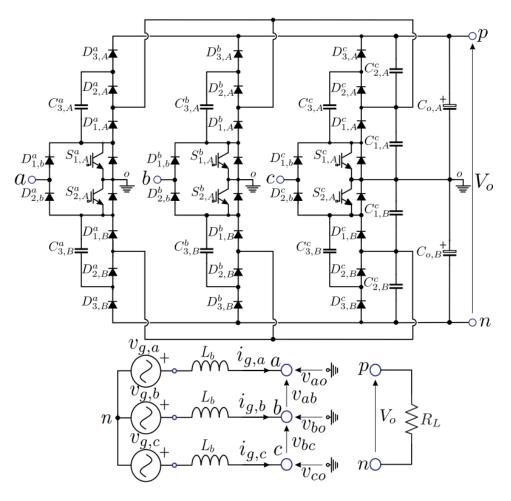

The MSSC can also be implemented in multilevel topologies, thus reducing the voltage stress on the switches and reducing the size of the input filters. A generalized study of multilevel MSSC rectifiers was presented in [52]. In this work, a 3-level 3SSC converter was implemented to evaluate the analysis. Fig. 11 (a) shows the generalized structure and Fig. 11 (b) shows the converter that was implemented in [52].

Fig. 10 – Single-phase T-type rectifier with 3SSC [51].

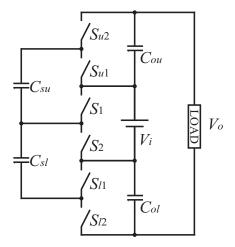

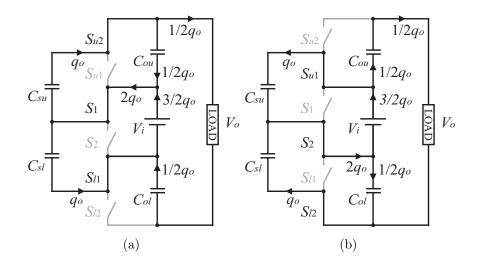

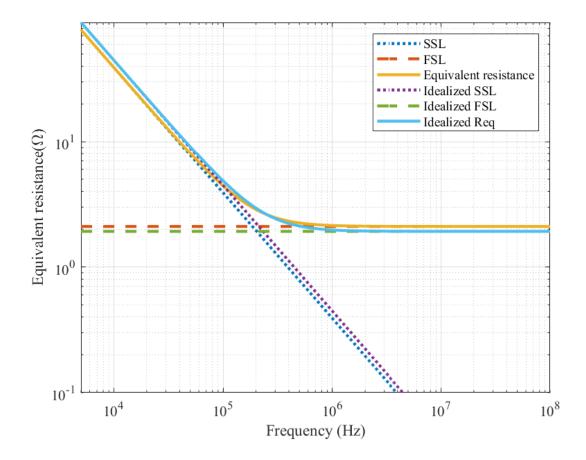

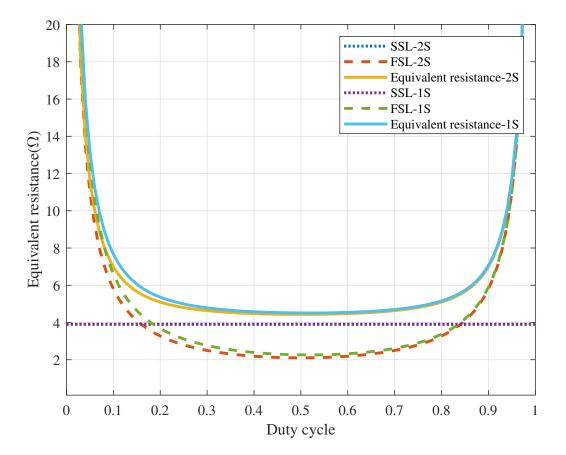

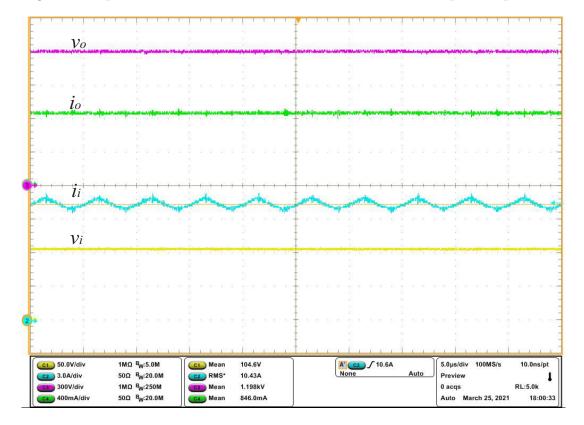

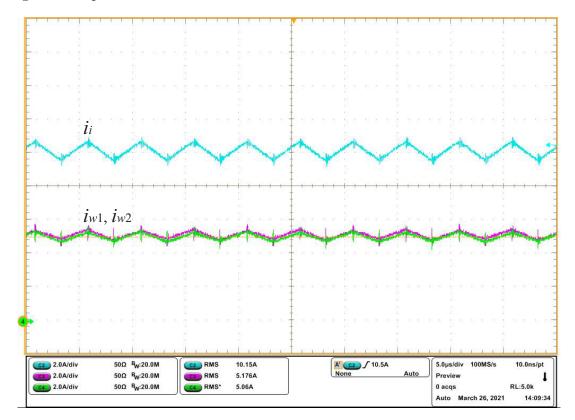

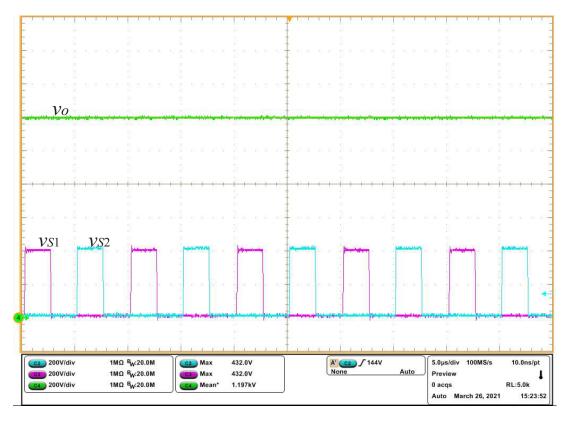

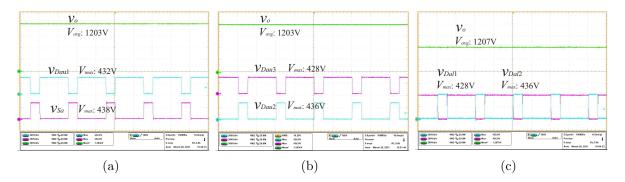

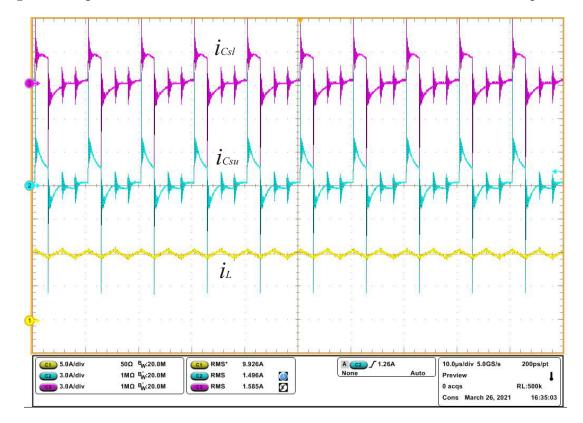

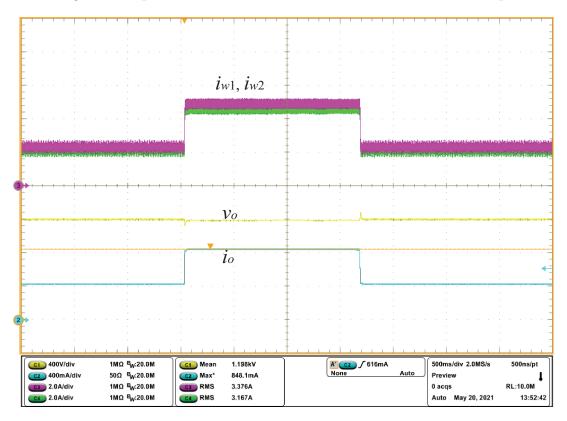

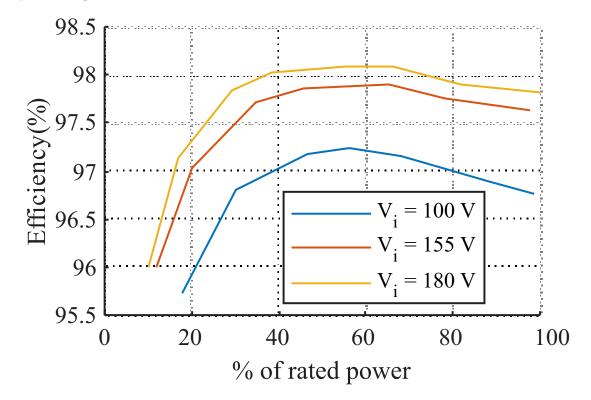

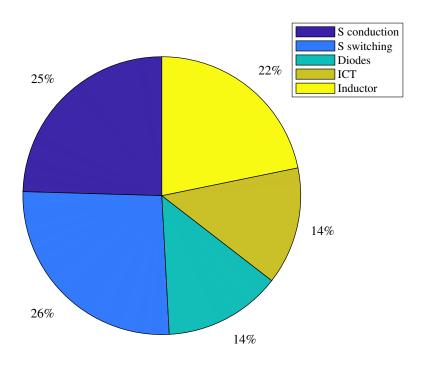

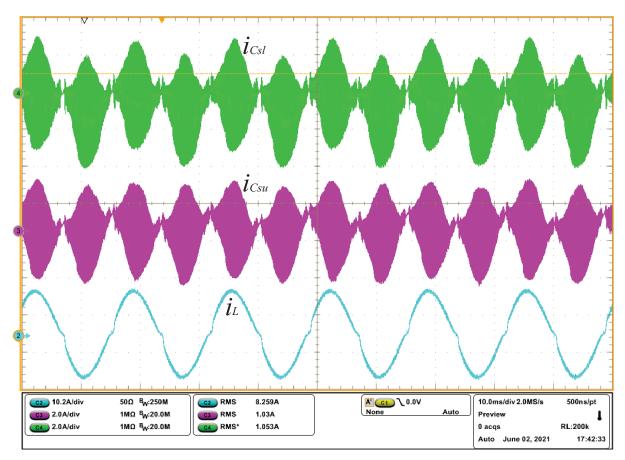

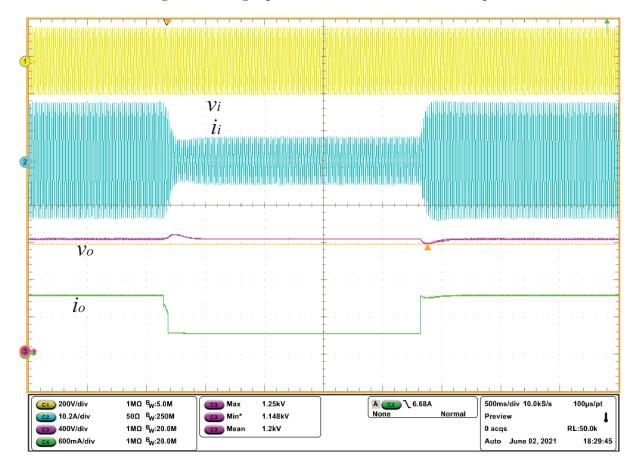

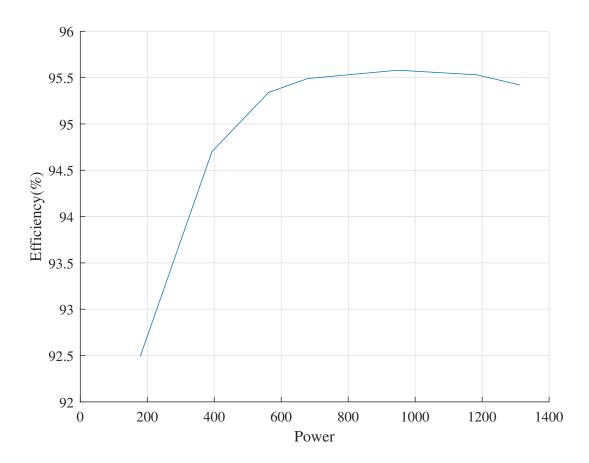

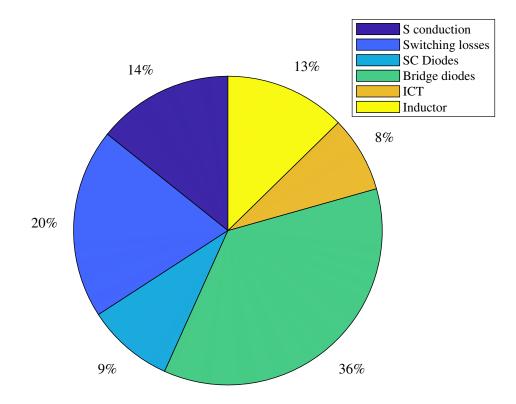

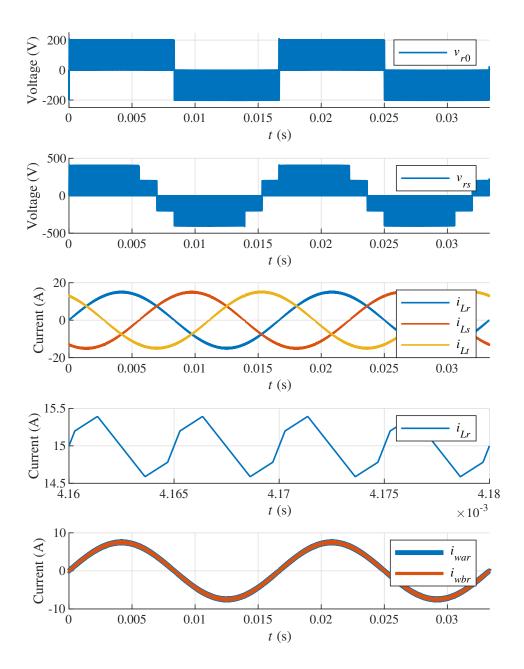

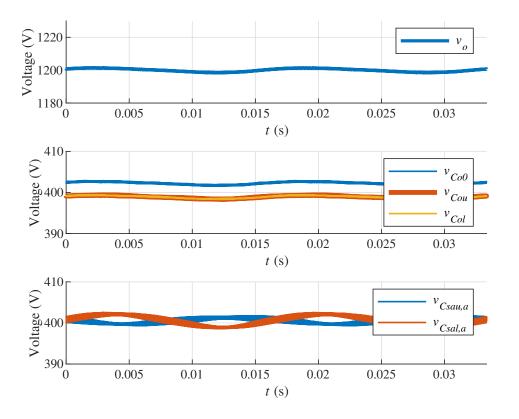

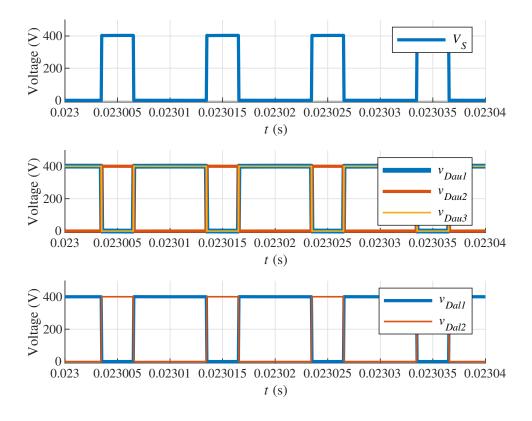

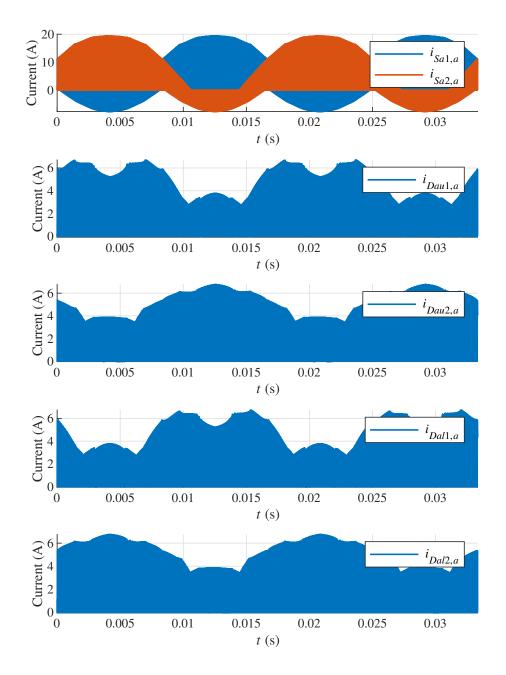

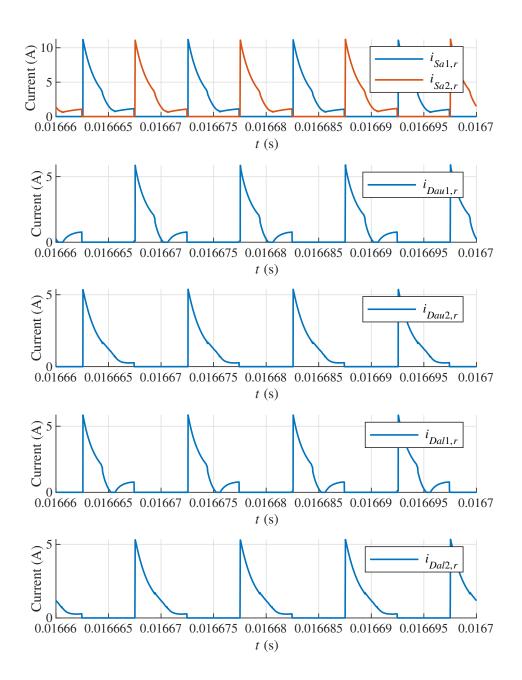

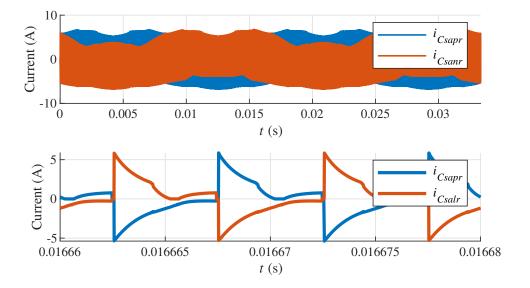

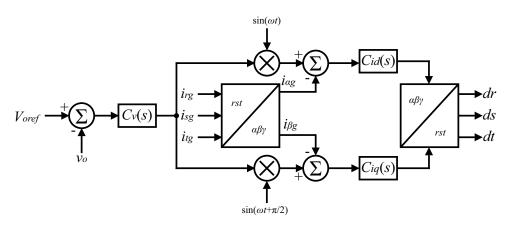

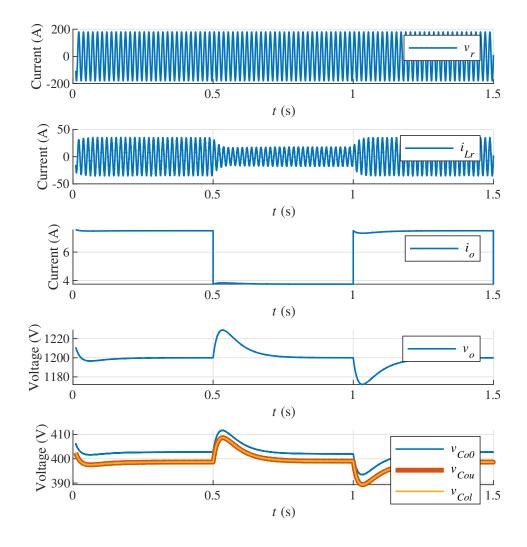

Fig. 11 – Three-level MSSC rectifiers [52].