# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Deni Germano Alves Neto

Ultra-Low-Voltage Minimalist Standard Cell Library

Florianópolis 2022 Deni Germano Alves Neto

## Ultra-Low-Voltage Minimalist Standard Cell Library

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do título de mestre em Engenharia Elétrica.

Orientador: Prof. Carlos Galup-Montoro, Dr.

Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Alves Neto, Deni Germano Ultra-Low-Voltage Minimalist Standard Cell Library / Deni Germano Alves Neto ; orientador, Carlos Galup-Montoro , 2022. 102 p. Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2022. Inclui referências. 1. Engenharia Elétrica. 2. Ultra-Low-Voltage. 3. CMOS. 4. Subthreshold. 5. Standard cells. I., Carlos Galup Montoro. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título. Deni Germano Alves Neto

## Ultra-Low-Voltage Minimalist Standard Cell Library

O presente trabalho em nível de mestrado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. Cesar Ramos Rodrigues, Dr. Universidade Federal de Santa Catarina

Profa. Cristina Meinhardt, Dra. Universidade Federal de Santa Catarina

> Eng. William Prodanov, Dr. Chipus Microelectronics

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de mestre em Engenharia Elétrica.

Coordenação do Programa de Pós-Graduação

Prof. Carlos Galup-Montoro, Dr. Orientador

Florianópolis, 2022.

Este trabalho é dedicado aos meus queridos avós.

### ACKNOWLEDGEMENTS

First, I would like to thank the institutions that made the realization of this work possible. Thanks to the Federal University of Santa Catarina (UFSC) for public, accessible, and quality education; to MOSIS and SBMicro, for the silicon processing of this work.

I would like to thank PPGEEL/UFSC, particularly the secretaries Marcelo, Lis, and Wilson, who were always very helpful.

It goes without saying how paramount professors Carlos Galup-Montoro and Marcio Cherem Schneider were throughout the last few years, uttermost to the development of this project. I can only appreciate their dedication to their work as scientists and teachers. Their guidance, criticism, explanations, and ideas inspire me to give my best. This work would not have been possible without them. Also, thanks to Nazide Martins for the help on the LCI.

I also would like to thank the examination committee members, prof. Cesar Ramos, profa. Cristina Meinhardt and Eng. of Chipus William Prodanov, for accepting the invitation and disposing of their time to evaluate this work.

Needless to say, I also thank my fellow LCI colleagues. On this regard, I have to acknowledge Luiz Rodovalho, Thiago Darós, João Vitor Testi, Cristina Adornes, Gabriel Maranhão, Evandro Bolzan, Rodrigo Wrege, Rafael Sanchotene, Jefferson Cardoso, Andrés Hurtado, Jeffer Rueda (in memoriam), Lucas Luiz and Franciele Nörnberg for their readiness to assist. Last but not least, I should probably thank Cristina Adornes (again), who directly worked with me, reviewing this dissertation for countless hours discussing transistors and writing in general. Their impact is crystalized in this manuscript.

Finally, I thank my family, to whom I dedicate this work. Despite understanding nothing about my research, they were always very supportive. My family and friends helped in more ways they can imagine to fulfill this work.

"What I cannot create, I do not understand." (Feynman, 1988)

### RESUMO

A operação de ultrabaixa tensão é uma abordagem atraente para aplicações com restrição de energia, onde a frequência de operação é uma preocupação secundária. No entanto, o aumento da variabilidade dos parâmetros do processo deve ser mitigado neste domínio. Esta dissertação propõe abordagens para melhorar a robustez de circuitos integrados digitais em operação sublimiar por meio de dimensionamento de dispositivos e topologias alternativas de circuito. A fim de transcender os limites anteriores de bibliotecas de células padrão de baixa tensão, esta dissertação apresenta uma metodologia para projetar uma biblioteca de células padrão minimalista de ultra baixa tensão de 100 mV; a biblioteca consiste em células combinacionais e sequenciais. Foram utilizadas duas topologias de circuitos lógicos, o CMOS sliced e o Schmitt trigger. A biblioteca de células padrão foi validada através do projeto e teste de circuitos divisores de frequência fabricados nas tecnologias de 130 nm e 180 nm. Resultados experimentais na tecnologia de 130 nm de um divisor de frequência com 15 estágios cascateados utilizando a lógica Schmitt trigger demonstram a operação em 32 kHz com uma tensão de alimentação de 76 mV. Os resultados em silício da tecnologia 180 nm operam em uma tensão ainda mais baixa, um divisor de frequência baseado na topologia *sliced* opera com uma tensão de alimentação de 72 mV, com 32 kHz de frequência de entrada. Todas as dez amostras dos divisores de frequência de 180 nm são totalmente funcionais em  $V_{DD} = 100$  mV, mostrando a robustez da biblioteca de ultra baixa tensão projetada nesta dissertação.

Palavras-chave: Ultra-baixa-tensão. Sublimiar. CMOS. Schmitt Trigger. Standard cells

### **RESUMO EXPANDIDO**

## INTRODUÇÃO

Os dispositivos semicondutores são os blocos de construção essenciais da economia moderna. Todos os produtos e serviços atuais dependem fortemente de chips, desde smartphones, computadores e carros até automação industrial.

Nas últimas décadas, a computação de alto desempenho permaneceu o domínio principal da tecnologia CMOS. No entanto, outra via de pesquisa e desenvolvimento é estimulada por eletrônicos vestíveis consumíveis em massa e a já estabelecida internet das coisas. No entanto, o desafio a ser enfrentado é fornecer energia elétrica a esses dispositivos eletrônicos. Sistemas sempre ativos, como nós de sensores sem fio, dispositivos biomédicos implantáveis e redes IoT, devem fornecer funcionalidade, mantendo uma quantidade de energia limitada. Em tais aplicações, os circuitos estão espalhados por diferentes ambientes e espera-se que sejam autossuficientes em energia. A rede elétrica e baterias não são mais uma solução viável para sustentar esses sistemas devido ao custo de manutenção e substituição de componentes no esgotamento da energia. Por outro Iado, a captação de energia fornece energia termoelétrica, fotovoltaica e vibracional nas proximidades do nó sensor. A operação de ultrabaixa tensão é uma abordagem atraente para aplicações com restrição de energia, onde a frequência de operação é uma preocupação secundária. No entanto, o aumento da variabilidade dos parâmetros do transistor MOS no processo de fabricação deve ser mitigado neste domínio.

### OBJETIVOS

Esta dissertação propõe abordagens para melhorar a robustez de circuitos integrados digitais em operação sublimiar por meio de dimensionamento de dispositivos e topologias alternativas de circuito.

### METODOLOGIA

A fim de transcender os limites anteriores de bibliotecas de células padrão de baixa tensão, esta dissertação apresenta uma metodologia para projetar uma biblioteca de células padrão minimalista de ultra baixa tensão de 100 mV; a biblioteca consiste em células combinacionais e sequenciais. Foram utilizadas duas topologias de circuitos lógicos, o CMOS *sliced* e o *Schmitt trigger*. A biblioteca de células padrão foi validada através do projeto e teste de circuitos divisores de frequência fabricados nas tecnologias de 130 nm e 180 nm.

## **RESULTADOS E DISCUSSÃO**

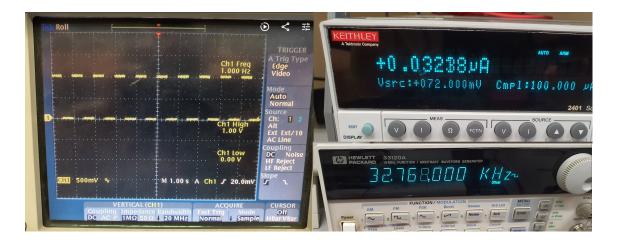

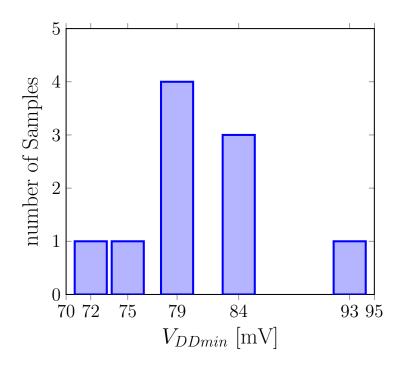

Resultados experimentais na tecnologia de 130 nm de um divisor de frequência com 15 estágios cascateados utilizando a lógica *Schmitt trigger* demonstram a operação em 32 kHz com uma tensão de alimentação de 76 mV. Os resultados em silício da tecnologia 180 nm operam em uma tensão ainda mais baixa, um divisor de frequência baseado na topologia *sliced* opera com uma tensão de alimentação de 72 mV, com 32 kHz de frequência de entrada. Todas as dez amostras dos divisores de frequência de 180 nm são totalmente funcionais em  $V_{DD}$  =100 mV, mostrando a robustez da biblioteca de ultra baixa tensão projetada nesta dissertação.

# CONSIDERAÇÕES FINAIS

Abordar a variabilidade na região sublimiar foi o principal desafio deste trabalho. No projeto a nível do transistor, técnicas de dimensionamento e associação de transistores foram usadas para melhorar a robustez das portas lógicas.

Duas topologias de portas lógicas foram comparadas neste trabalho, a baseada na topologia *sliced* e a baseada no inversor *Schmitt trigger*. A simulações pós-layout da biblioteca de células padrão mostrou que as células baseadas em *sliced* têm uma melhoria significativa na dissipação de potência, tempo de propagação e área.

A biblioteca de células padrão foi verificada através do projeto de divisores de frequência. O divisor de frequência foi simulado e fabricado em duas tecnologias CMOS diferentes; este circuito foi escolhido devido à vasta aplicação em relógios de tempo real. O divisor de frequência baseado na topologia *sliced* chegou a uma tensão de alimentação de 72 mV, a mais baixa para um circuito sequencial CMOS. Este resultado prova que mesmo em um campo maduro como o projeto de circuitos operando na região sublimiar, há espaço para melhorias.

Palavras-chave: Ultra-baixa-tensão. Sublimiar. CMOS. Schmitt Trigger. Células lógicas

### ABSTRACT

Ultra-low-voltage operation is a compelling approach for power-constrained applications where the frequency of operation is a secondary concern. However, the increased variability of the process parameters must be mitigated in this domain. This dissertation proposes approaches to improve the robustness of digital integrated circuits in subthreshold operation through device sizing and improved circuit topologies. In order to transcend the previous limits of low voltage standard cells libraries, this dissertation presents a methodology to design an ultra-low-voltage minimalist standard cell library to operate with a supply voltage of 100 mV; the library consists of combinational and sequential cells. Two topologies of logic circuits were used, the CMOS sliced-based and the Schmitt trigger-based cells. The standard cell library was validated through the design and test of frequency dividers circuits fabricated in 130 nm and 180 nm technologies. Experimental results on the 130 nm tech of a 15-stage Schmitt trigger-based frequency divider chain demonstrate the operation at 32 kHz with a supply voltage of 76 mV. The 180 nm silicon results operate in an even more extreme low voltage, a 72 mV CMOS sliced-based frequency divider operate at 32 kHz. All ten samples of the 180 nm frequency dividers are fully functional at  $V_{DD} = 100 \text{ mV}$ , resulting in a 100% yield.

Keywords: Ultra-Low-Voltage. CMOS. Subthreshold. Schmitt trigger. Standard cells

# LIST OF FIGURES

| Figure 1 –  | Unity-gain frequency of an CS amplifier versus inversion level at three dif-                                                              |    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | ferent technology nodes                                                                                                                   | 24 |

| Figure 2 –  | Symbol of the NMOS transistor                                                                                                             | 28 |

| Figure 3 –  | Low-frequency small-signal model of the MOSFET                                                                                            | 30 |

| Figure 4 –  | $I_D \ge V_{GS}$ @ $V_{DS}$ = 100 mV of an NMOS transistor, BSIM vs 4PM                                                                   | 31 |

|             | $I_D \times V_{DS}$ @ $V_{GS}$ = 100 mV of an NMOS transistor, BSIM vs 4PM                                                                | 32 |

| Figure 6 –  | CMOS Inverter with a equivalent load capacitance $C_L$                                                                                    | 33 |

| Figure 7 –  | Voltage transfer characteristic of the CMOS inverter for different values of                                                              |    |

|             | supply voltages.                                                                                                                          | 33 |

| Figure 8 –  | VTC dependence on the imbalance factor.                                                                                                   | 34 |

| Figure 9 –  | Definition of $t_{p_{HL(LH)}}$ and $t_{p_{HL(LH)}}$ of the CMOS inverter                                                                  | 36 |

|             | Ring Oscillator schematic                                                                                                                 | 37 |

| Figure 11 – | Delay of an inverter vs $V_{DD}$ in the 180 nm technology, with $rac{W_N}{L_N}=rac{420\ nm}{300\ nm}$                                   |    |

|             | and $\frac{W_P}{L_P} = \frac{530 \ nm}{300 \ nm}$                                                                                         | 37 |

| Figure 12 - | Schematic of the variable activity factor circuit                                                                                         | 38 |

|             | PDP vs $V_{DD}$ with variable activity factor.                                                                                            | 39 |

| Figure 14 - | Voltage transfer characteristics of the symmetrical CMOS Schmitt trigger                                                                  | 40 |

|             | Voltage gain of the ST inverter as a function of $I_2/I_0$                                                                                | 41 |

|             | Oscillation frequency as a function of the channel length                                                                                 | 41 |

| Figure 17 – | Distributions of the threshold voltage of an NMOS transistor.                                                                             | 43 |

| Figure 18 – | Impact of mismatch and process variation on VTC of the CMOS inverter                                                                      |    |

|             | at $V_{DD} = 100 \text{ mV}$ .                                                                                                            | 44 |

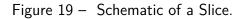

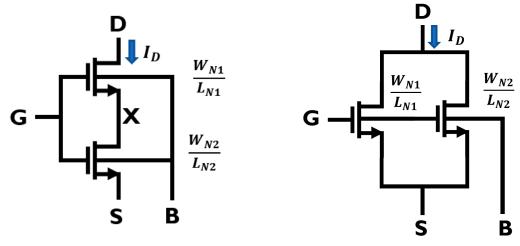

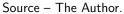

| Figure 19 – | Schematic of a Slice                                                                                                                      | 45 |

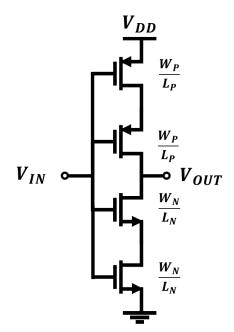

| Figure 20 - | MOS associations.                                                                                                                         | 45 |

| Figure 21 – | Schematic of two Slices.                                                                                                                  | 47 |

| Figure 22 – | Schematic of the NAND logic gates                                                                                                         | 48 |

| Figure 23 – | Comparison of VTCs of sliced and traditional CMOS inverter, from 200                                                                      |    |

|             | samples of Monte Carlo: mismatch and process variations. Sliced from Fig-                                                                 |    |

|             | ure 21. The dimensions of the transistors are : $\frac{W_P}{L_P} = \frac{530 nm}{300 nm}$ and $\frac{W_N}{L_N} = \frac{420 nm}{300 nm}$ . | 48 |

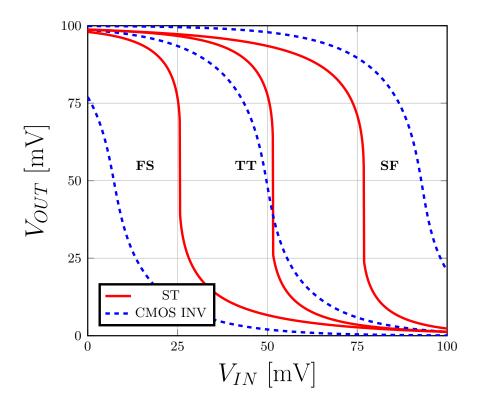

| Figure 24 - | Comparison of VTCs of ST and traditional CMOS inverter, from simulation,                                                                  |    |

| -           | for FS,TT, and SF corners at $V_{DD} = 100$ mV                                                                                            | 49 |

| Figure 25 - | CMOS inverter VTC at $V_{DD} = 100$ mV. The dimensions of the transistors                                                                 |    |

|             | are given in Table 3                                                                                                                      | 51 |

| Figure 26 - | NAND-Sliced VTC at $V_{DD} = 100 \text{ mV}$ .                                                                                            | 52 |

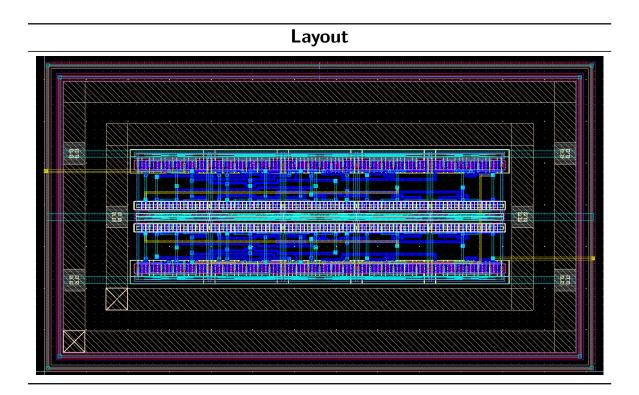

|             | Standard cell layout style                                                                                                                | 53 |

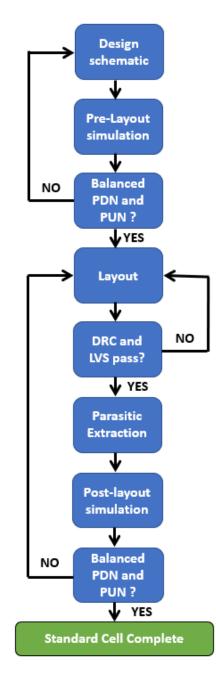

|             | Design flow of the ULV standard cell library                                                                                              | 54 |

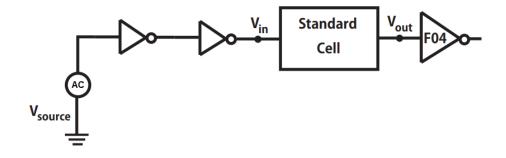

| Figure 29 – Testbench used to characterize the standard cells                              | 55  |

|--------------------------------------------------------------------------------------------|-----|

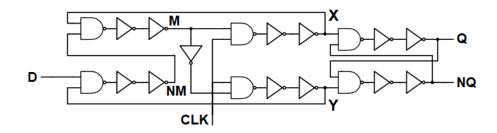

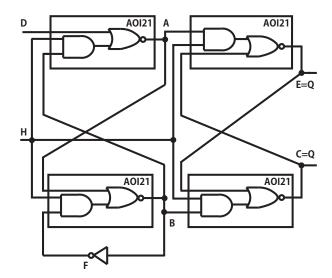

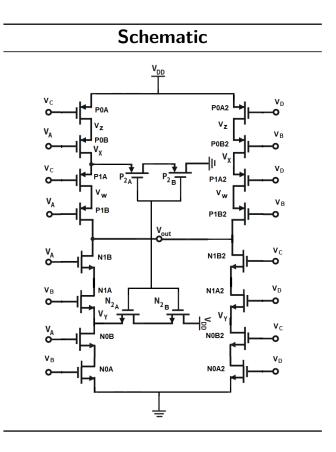

| Figure 30 – Race-free D-Flip-Flop architecture 1 (DFF1)                                    | 57  |

| Figure 31 – Race-free D-Flip-Flop architecture 2 (DFF2)                                    | 57  |

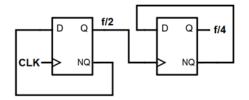

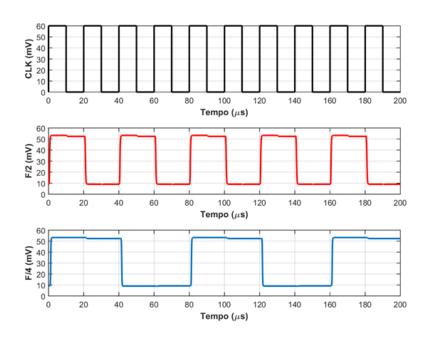

| Figure 32 – Schematic of a counter-based frequency divider by four using the DFF1          |     |

| topology                                                                                   | 59  |

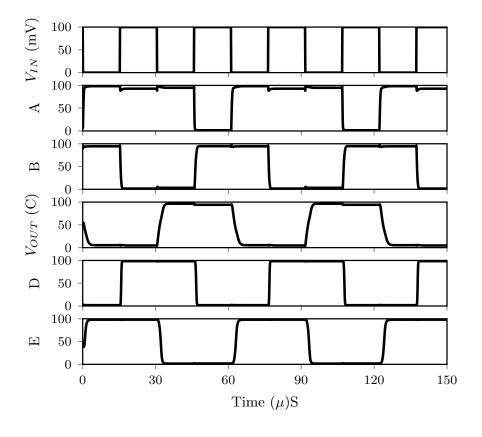

| Figure 33 – Counter-based Frequency divider by 4 operating at $V_{DD}=$ 60 mV              | 60  |

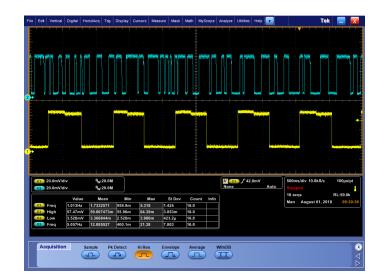

| Figure 34 – Output signals of both frequency divider chains at 76 mV of supply voltage     | 61  |

| Figure 35 – Minimum supply voltage of the 15-stages frequency divider chain in the         |     |

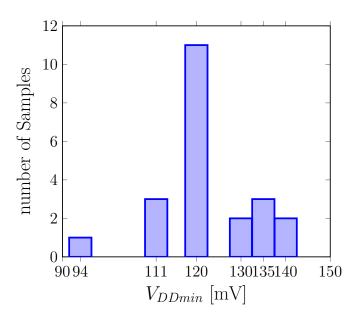

| tapeout 1 - Conventional logic, with 32 kHz of input frequency. $\ldots$ .                 | 61  |

| Figure 36 – Minimum supply voltage of the frequency divider by $2^{15}$ in the tapeout 1 - |     |

| ST-based logic, with 32 kHz of input frequency                                             | 62  |

| Figure 37 – Vittoz Frequency divider by 2                                                  | 63  |

| Figure 38 – Waveforms of the Vittoz Frequency divider by 2                                 | 64  |

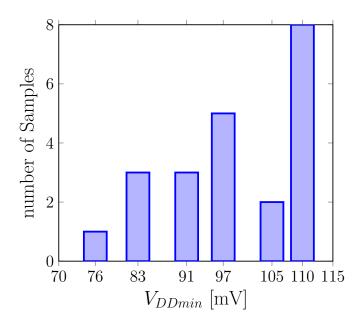

| Figure 39 – Minimum supply voltage of the 15-stages frequency divider chain in the         |     |

| tapeout 2 - Sliced based logic, with 32 kHz of input frequency                             | 64  |

| Figure 40 – Minimum supply voltage of the frequency divider by $2^{15}$ in the tapeout 2,  |     |

| with 32 kHz of input frequency.                                                            | 65  |

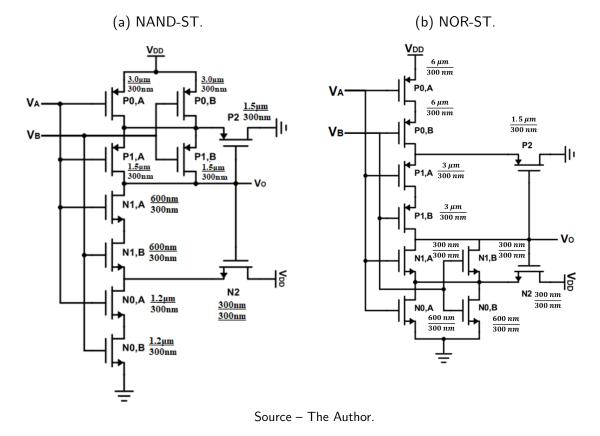

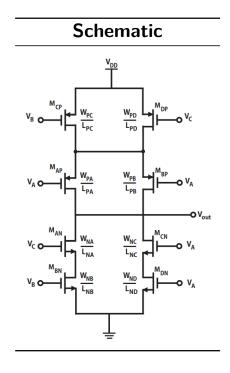

| Figure 41 – Schematic and dimensions of the ST logic gates in 130 nm technology. $\ . \ .$ | 76  |

| Figure 42 – (a) Circuit to measure the $g_m/I_D$ characteristic in the linear region; (b)  |     |

| measurements of $g_m/I_D$ and $I_D$ as a function of $V_{GB}$ ; the annotated              |     |

| points are used to determine $V_{T0}$ and $I_S$ [57]                                       | 101 |

| Figure 43 $-$ (a) Circuit to determine the CSIG and (b) its equivalent small-signal model. | 102 |

|                                                                                            |     |

## LIST OF TABLES

| Table 1 –  | The ratio between the strong and weak maximum currents in some repre-          |    |

|------------|--------------------------------------------------------------------------------|----|

|            | sentative technology nodes                                                     | 23 |

| Table 2 –  | Truth table of the 2-input NAND gate                                           | 47 |

| Table 3 –  | Dimensions and parameters of the balanced CMOS inverter in 180 nm tech-        |    |

|            | nology                                                                         | 50 |

| Table 4 –  | Dimensions and parameters of the transistors used in the SCL in 180 nm         |    |

|            | technology.                                                                    | 53 |

| Table 5 –  | Simulation results of the Sliced Library in 180 nm technology                  | 56 |

| Table 6 –  | Simulation results of the Sliced D-Flip-Flops in 180 nm technology             | 58 |

| Table 7 –  | Simulation results of the Sliced frequency dividers, $V_{DD}=100$ mV and       |    |

|            | $f_{in} = 32 \text{ kHz}.$                                                     | 63 |

| Table 8 –  | Results of Monte Carlo simulations across process, temperature, and sup-       |    |

|            | ply voltage variations of a Vittoz frequency divider by four, with an input    |    |

|            | frequency of 32 kHz                                                            | 66 |

| Table 9 –  | State-of-the-art comparison of ultra-low-voltage frequency dividers            | 68 |

| Table 10 – | Simulation results of the Schmitt trigger-based standard cell library in 180   |    |

|            | nm technology.                                                                 | 74 |

| Table 11 – | ST inverter dimensions                                                         | 75 |

| Table 12 – | NAND and NOR dimensions in 130 nm technology.                                  | 75 |

| Table 13 – | Simulated Comparison of delay, total power and area of the classical and ST $$ |    |

|            | logic for $V_{DD} = 90$ mV.                                                    | 76 |

| Table 14 – |                                                                                | 99 |

# LIST OF ABBREVIATIONS AND ACRONYMS

| AOI    | AND-OR-INVERTER                                   |

|--------|---------------------------------------------------|

| BSIM   | Berkeley Short-Channel IGFET Model                |

| CMOS   | Complementary Metal-Oxide Semiconductor           |

| CS     | Common-Source                                     |

| CSIG   | Common-Source Intrinsic Gain                      |

| DC     | Direct Current                                    |

| DFF    | D-Flip-Flop                                       |

| DIBL   | Drain-Induced Barrier Lowering                    |

| DRC    | Design Rule Check                                 |

| FD     | Frequency Divider                                 |

| MEP    | Minimum Energy Point                              |

| LVS    | Layout Versus Schematic                           |

| MOS    | Metal-Oxide-Semiconductor                         |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

| MVT    | Medium Threshold Voltage Transistor               |

| Ν      | Number of Stages                                  |

| NMOS   | N-Channel MOS                                     |

| NVT    | Native Transistor                                 |

| OAI    | OR-AND-INVERTER                                   |

| PDK    | Process Design Kit                                |

| PDN    | Pull-down Network                                 |

| PDP    | Power-Delay-Product                               |

| PMOS   | P-Channel MOS                                     |

| PUN    | Pull-up Network                                   |

| RSCE   | Reverse Short-Channel Effect                      |

- ROSC Ring Oscillator

- SCL Standard Cell Library

- SVT Standard Threshold Voltage Transistor

- ST Schmitt-Trigger

- ULV Ultra-Low-Voltage

- VTC Voltage Transfer Characteristic

# LIST OF SYMBOLS

| $\alpha$     | Activity factor                              |

|--------------|----------------------------------------------|

| $\mu$        | Mean value                                   |

| $\mu_n$      | Electron mobility                            |

| $\phi_t$     | Thermal voltage                              |

| $\sigma_x$   | Standard deviation of x                      |

| σ            | DIBL coefficient                             |

| $A_V$        | Voltage gain                                 |

| $A_{V_T}$    | Pelgrom coefficient of the threshold voltage |

| $C_L$        | Load capacitance                             |

| $C_{ox}$     | Oxide capacitance per unit area              |

| $f_{in}$     | Input frequency                              |

| $f_{osc}$    | Frequency of oscillation                     |

| $f_{out}$    | Output frequency                             |

| $f_{switch}$ | Switching frequency                          |

| $f_T$        | Unity gain frequency                         |

| $g_{mb}$     | Bulk transconductance                        |

| $g_{md}$     | Drain transconductance                       |

| $g_{ms}$     | Source transconductance                      |

| $g_m$        | Gate transconductance                        |

| $I_{SC}$     | Short-circuit current                        |

| $I_D$        | Drain current                                |

| $i_d$        | Normalizes drain current                     |

| $I_F$        | Forward current                              |

| $i_f$        | Normalized forward current (inversion level) |

| $I_{LK}$     | Leakage current                              |

| $I_{N(P)}$     | Transistor scale factor/transistor strength |

|----------------|---------------------------------------------|

| $I_R$          | Reverse current                             |

| $i_r$          | Normalized reverse current                  |

| $I_S$          | Specific current                            |

| $I_2/I_1$      | Design factor                               |

| $I_{1}/I_{0}$  | Design factor                               |

| L              | Transistor channel length                   |

| n              | Slope factor                                |

| $P_{dyn}$      | Dynamic power                               |

| $P_{stat}$     | Static power                                |

| $P_{sc}$       | Short-circuit power                         |

| $P_{tot}$      | Total power                                 |

| T              | Temperature                                 |

| $T_{sc}$       | Period of conduction of ${\cal I}_{SC}$     |

| $t_p$          | Propagation delay                           |

| $t_{pHL}$      | High-to-low propagation delay               |

| $t_{pLH}$      | Low-to-high propagation delay               |

| $V_B$          | Bulk voltage                                |

| $V_{DD_{min}}$ | Minimum voltage supply                      |

| $V_{DD}$       | Supply voltage                              |

| $V_D$          | Drain voltage                               |

| $V_G$          | Gate voltage                                |

| $V_{IN}$       | Input voltage                               |

| $V_M$          | Inverter threshold voltage                  |

| $V_{OUT}$      | Output voltage                              |

| $V_P$          | Pinch-off voltage                           |

- $V_S$  Source voltage

- $V_{T0}$  Threshold voltage

- W Transistor channel width

# CONTENTS

| 1     |                                                   | 22                        |  |  |  |

|-------|---------------------------------------------------|---------------------------|--|--|--|

| 1.1   | OBJECTIVES                                        | 26                        |  |  |  |

| 1.2   | WORK ORGANIZATION                                 | 26                        |  |  |  |

| 2     | TRANSISTOR LEVEL DESIGN                           | 27                        |  |  |  |

| 2.1   | MOSFET MODELING                                   | 27                        |  |  |  |

| 2.1.1 | The 4-parameter model                             |                           |  |  |  |

| 2.1.2 | Subthreshold operation                            | 29                        |  |  |  |

| 2.1.3 | Small-Signal Transconductances                    | 29                        |  |  |  |

| 2.1.4 | 4PM vs BSIM                                       | 31                        |  |  |  |

| 2.2   | THE ULV INVERTER                                  | 32                        |  |  |  |

| 2.2.1 | Voltage transfer characteristic                   | 32                        |  |  |  |

| 2.2.2 | Power dissipation                                 | 34                        |  |  |  |

| 2.2.3 | Delay                                             | 35                        |  |  |  |

| 2.2.4 | Power-delay-product                               | 38                        |  |  |  |

| 2.3   | THE ULV SCHMITT TRIGGER                           | 39                        |  |  |  |

| 3     | STANDARD CELL DESIGN IMPLEMENTATION               |                           |  |  |  |

| 3.1   | ADDRESSING VARIABILITY                            |                           |  |  |  |

| 3.1.1 | Techniques to Improve Robustness                  |                           |  |  |  |

| 3.1.2 | Schmitt trigger vs process corners                |                           |  |  |  |

| 3.2   | SIZING STRATEGIES IN ULV STANDARD CELLS           |                           |  |  |  |

| 3.3   | LAYOUT OF A STANDARD CELL                         |                           |  |  |  |

| 3.4   | STANDARD CELL SIMULATIONS                         | STANDARD CELL SIMULATIONS |  |  |  |

| 3.5   | SEQUENTIAL STANDARD CELLS                         |                           |  |  |  |

| 3.5.1 | Flip Flop design                                  | 57                        |  |  |  |

| 4     | DESIGN AND TEST OF FREQUENCY DIVIDERS BASED ON    |                           |  |  |  |

|       | THE ULV-SCL                                       | 59                        |  |  |  |

| 4.1   | CHIP 1 - FIRST FREQUENCY DIVIDER PROTOTYPE        | 59                        |  |  |  |

| 4.2   | CHIP 2 - SECOND FREQUENCY DIVIDER PROTOTYPE       | 62                        |  |  |  |

| 4.3   | CHIP 3 - THIRD FREQUENCY DIVIDER PROTOTYPE        |                           |  |  |  |

| 5     | CONCLUSIONS AND FUTURE WORK                       | 67                        |  |  |  |

|       | References                                        | 69                        |  |  |  |

|       | APPENDIX A – SIMULATIONS RESULTS OF THE ST-SLICED |                           |  |  |  |

|       | BASED SCL IN 180 NM TECHNOLOGY                    | 74                        |  |  |  |

|       | APPENDIX B – 130 NM STANDARD CELL LIBRARY         | 75                        |  |  |  |

|       | APPENDIX C – LAYOUT INFORMATION                   | 77                        |  |  |  |

|       | APPENDIX D – CMOS INVERTER SCHEMATIC AND LAYOUT   | 78                        |  |  |  |

| APPENDIX        | E – CMOS INVERTER-SLICED SCHEMATIC AND                                                                       |     |

|-----------------|--------------------------------------------------------------------------------------------------------------|-----|

|                 | LAYOUT                                                                                                       | 79  |

| APPENDIX        | F – CMOS INVERTER-ST SCHEMATIC AND LAY-                                                                      |     |

|                 | OUT                                                                                                          | 80  |

| APPENDIX        | G – CMOS INVERTER-SLICED X2 AND X4 LAY-                                                                      |     |

|                 | OUTS                                                                                                         | 81  |

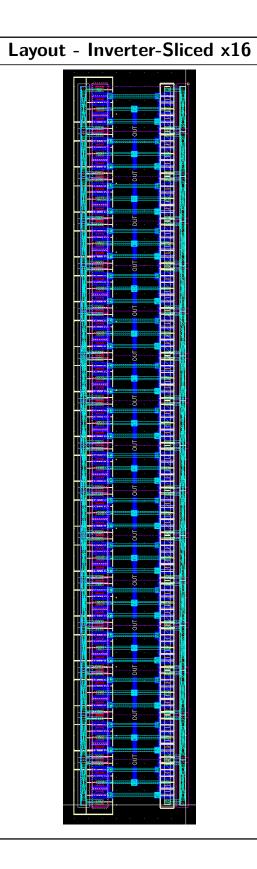

| APPENDIX        | H – CMOS INVERTER-SLICED X16 LAYOUT                                                                          | 82  |

| APPENDIX        | I – CMOS NAND-SLICED SCHEMATIC AND LAY-                                                                      |     |

|                 | OUT                                                                                                          | 83  |

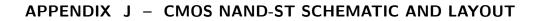

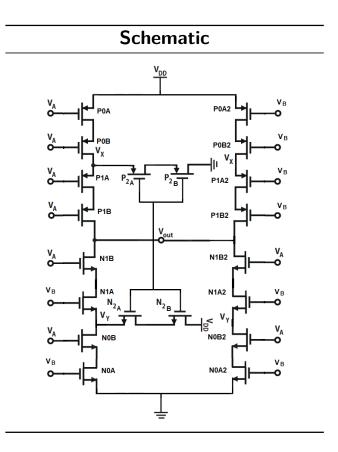

| APPENDIX        | J – CMOS NAND-ST SCHEMATIC AND LAYOUT                                                                        | 84  |

| APPENDIX        | K – CMOS NOR-SLICED SCHEMATIC AND LAY-                                                                       |     |

|                 | OUT                                                                                                          | 85  |

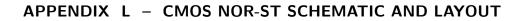

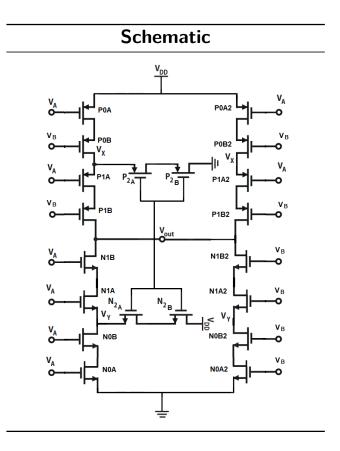

| APPENDIX        | L – CMOS NOR-ST SCHEMATIC AND LAYOUT                                                                         | 86  |

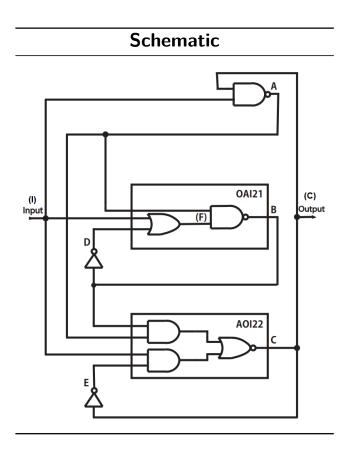

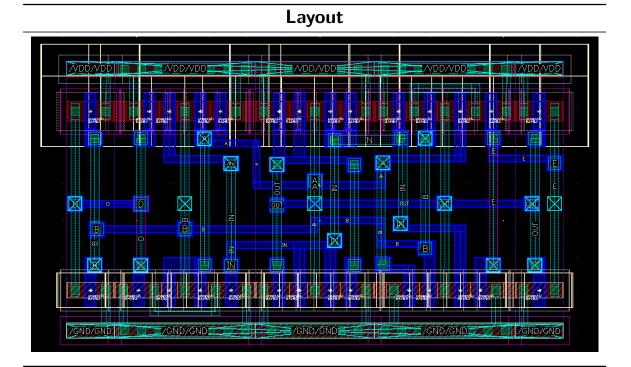

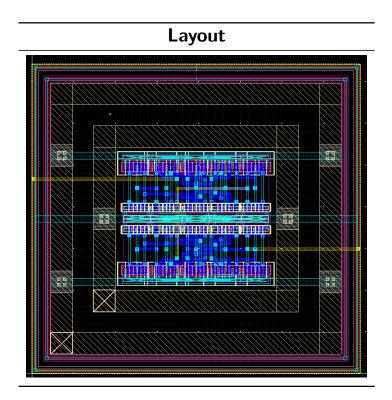

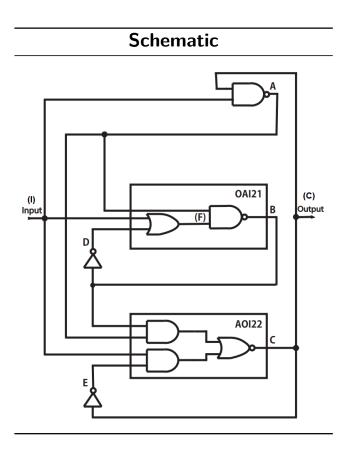

| APPENDIX        | M – CMOS OAI21-SLICED SCHEMATIC AND LAY-                                                                     |     |

|                 | OUT                                                                                                          | 87  |

| APPENDIX        | N – CMOS OAI21-ST SCHEMATIC AND LAYOUT                                                                       | 88  |

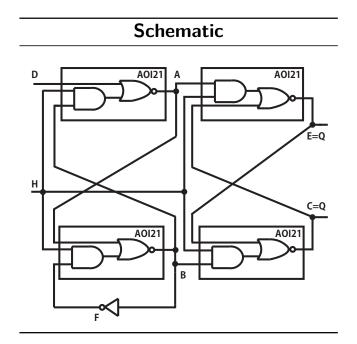

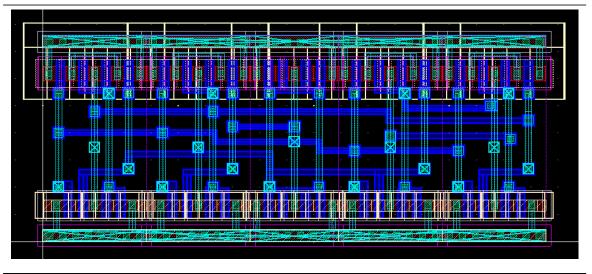

| APPENDIX        | 0 – CMOS AOI21-SLICED SCHEMATIC AND LAY-                                                                     |     |

|                 | OUT                                                                                                          | 89  |

| APPENDIX        | P – CMOS A0I21-ST SCHEMATIC AND LAYOUT                                                                       | 90  |

| APPENDIX        | Q – CMOS AOI22-SLICED SCHEMATIC AND LAY-                                                                     |     |

|                 | OUT                                                                                                          | 91  |

| APPENDIX        | R – CMOS A0122-ST SCHEMATIC AND LAYOUT                                                                       | 92  |

| APPENDIX        | S – CMOS DFF-SLICED SCHEMATIC AND LAY-                                                                       |     |

|                 | OUT                                                                                                          | 93  |

|                 | T – CMOS DFF-ST SCHEMATIC AND LAYOUT .                                                                       | 94  |

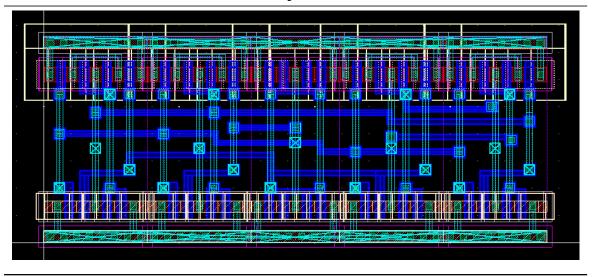

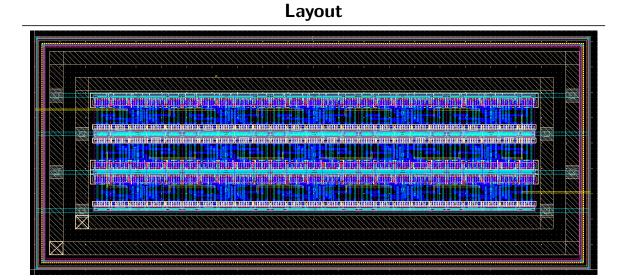

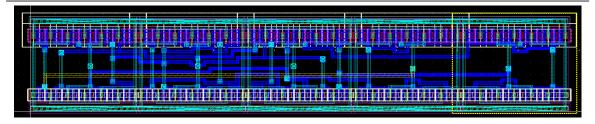

| APPENDIX        | U – VITTOZ SLICED FREQUENCY DIVIDER BY                                                                       |     |

|                 | 2 SCHEMATIC AND LAYOUT                                                                                       | 95  |

| APPENDIX        | V – VITTOZ SLICED FREQUENCY DIVIDER BY 4                                                                     |     |

|                 | AND 15 STAGES FREQUENCY DIVIDER CHAIN                                                                        |     |

|                 | LAYOUTS                                                                                                      | 96  |

| APPENDIX        | W – VITTOZ ST FREQUENCY DIVIDER BY 2 SCHE                                                                    |     |

|                 | AND LAYOUT                                                                                                   | 97  |

| APPENDIX        | X – VITTOZ ST FREQUENCY DIVIDER BY 4 AND                                                                     |     |

|                 | 15 STAGES FREQUENCY DIVIDER CHAIN LAY                                                                        |     |

|                 | OUTS                                                                                                         | 98  |

|                 | Y – DESIGNED CHIPS                                                                                           | 99  |

|                 |                                                                                                              | 100 |

|                 | N OF THRESHOLD VOLTAGE ( $V_{T0}$ ), SPECIFIC CURRENT                                                        |     |

| $(I_S)$ AND SLO | $OPE  FACTOR (n) \ldots \ldots$ | 100 |

A.1

# A.2 EXTRACTION OF DRAIN-INDUCED BARRIER LOWERING FACTOR ( $\sigma$ ) 101

### **1** INTRODUCTION

Semiconductor devices are the essential building blocks of the modern economy. All current products and services rely heavily on chips, from smartphones, computers, and cars to industrial automation and defense. The global chip market was approximately \$500 billion in 2021 and is expected to grow to \$1 trillion by 2030 [1] as data volumes, computing power, and connectivity increase.

Over the past decades, high-performance computing remained the primary domain of complementary metal-oxide-semiconductor (CMOS) technology. Nevertheless, another avenue of research and development is stimulated by mass-consumable electronic wearables and the already established Internet-of-Things (IoT). However, the challenge to be addressed is supplying those electronic devices with electrical power. Always-on systems, such as wireless sensor nodes, implantable biomedical devices, and IoT networks, must provide functionality while maintaining a limited power budget [2]. In such applications, circuits are scattered across different environments and expected to be energy self-sufficient. Power grids and batteries are no longer a viable solution to sustain these systems due to the cost of maintenance and replacement of components upon energy depletion. On the other hand, energy harvesting provides power from thermometric, photovoltaic, and vibration in the vicinity of the sensor node, as presented in [3].

In the early years of the metal-oxide-semiconductor field-effect transistor (MOSFET), integrated circuit designers used the well-known quadratic relationship between drain current  $(I_D)$  and gate-source voltage  $(V_{GS})$  in a saturated transistor [4], presented in Equation (1), also known as the strong inversion (SI) drain current, to determine the transistor gate geometry.

$$I_{D,SI} = \frac{\beta}{2n} (V_{GS} - V_{T0})^2$$

(1)

In this simplified model of  $I_D$ , the transistor is represented by 3 parameters, the threshold voltage  $(V_{T0})$ , the slope factor n and the transconductance parameter  $\beta$  given by

$$\beta = \mu C_{ox} \frac{W}{L} \tag{2}$$

where  $\mu$  is the carrier mobility,  $C_{ox}$  is the oxide capacitance, W the channel width and L the channel length.

The MOS transistor has increased performance and decreased power consumption over the years through the scaling down of its dimensions. Dennard's constant field scaling [5] was the predominant device scaling method used in the last four decades of Moore's Law [6]. Dennard proposed that performance improvement could be observed by scaling the minimum channel length. To mitigate the inevitable reliability problems and reduction in functional lifetime, the length of the channel and the operating voltage must also be scaled by the same factor to maintain the same electric field. Reducing the gate-source voltage  $(V_{GS})$  below the threshold of conduction, also known as the threshold voltage  $(V_{T0})$ , leads to an exponential relationship between the drain current and the gate-source voltage, as shown in Equation (3). The regime of operation of the MOS when  $V_{GS} \leq V_{T0}$  is called the subthreshold region, also known as weak inversion (WI), studied by Swanson and Meindl in [7].

$$I_{D,WI} = I_0 e^{\frac{V_{GS} - V_{T0}}{n\phi_t}}$$

(3)

where  $\phi_t$  is the thermal voltage and  $I_0$  is the specific saturation current.

One can compare a mature MOS process of the '80s with a 00's technology node and a low voltage advanced technology 10's by taking the ratio of a transistor in strong inversion (1) operating at the supply voltage  $(V_{DD})$ , i.e.,  $V_{GS} = V_{DD}$  over the subthreshold current of a transistor operating at the threshold of conduction, i.e.,  $V_{GS} = V_{TO}$ . Equation (4) shows the ratio between the strong and weak inversion drain currents.

$$\frac{I_{D,SI_{@V_{DD}}}}{I_{D,WI@V_{T0}}} = \frac{1}{2e} \left(\frac{V_{DD} - V_{T0}}{n\phi_t}\right)^2$$

(4)

Table 1 shows the supply voltage, threshold voltage, and current ratio of some representative technology nodes: n = 1,  $\phi_t$  = 26 mV, the values of  $V_{DD}$  and  $V_{T0}$  were based on the work of CMOS scaling trends in [8].

Table 1 – The ratio between the strong and weak maximum currents in some representative technology nodes.

| Technology decade | $V_{DD}$ [V] | $V_{T0}$ [V] | $\frac{I_{D,SI}}{I_{D,WI}}$ |

|-------------------|--------------|--------------|-----------------------------|

| '80s              | 15           | 1            | 53331                       |

| 00's              | 1.5          | 0.5          | 272                         |

| 10's              | 0.5          | 0.25         | 17                          |

Source - The Author.

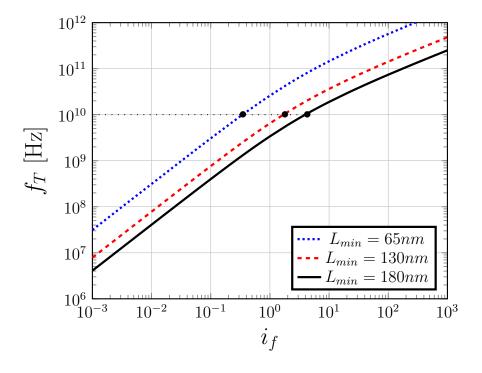

Table 1 presents a simple but effective way to observe that with the scaling process, the values of  $V_{DD}$  and  $V_{TO}$  are getting closer at each new technology; thus, the subthreshold current is becoming more relevant on the design of integrated circuits. Another way to deal with the importance of subthreshold design is to introduce the concept of inversion levels  $(i_f)$ , presented in chapter 2 of [9]. For design purposes,  $i_f < 1$  characterizes operation in weak inversion, while for  $i_f > 100$ , it is assumed operation in strong inversion. For inversion levels between 1 and 100, it is said that the transistors operate in moderate inversion (MI). Equation (5) shows the unity gain frequency  $(f_T)$  of a single transistor, i.e., the frequency at which the short-circuit current gain drops to 1 in the common-source (CS) configuration. The first-order approximation of the unity-gain frequency is plotted for three different technology nodes in Figure 1. The schematic and formal analysis of the circuit are shown in Chapter 2 of [9].

$$f_T \approx \frac{\mu \phi_t}{2\pi L^2} 2\left(\sqrt{1+i_f} - 1\right) \tag{5}$$

Figure 1 – Unity-gain frequency of an CS amplifier versus inversion level at three different technology nodes.

Source - The Author.

Figure 1 shows the impact of MOS scaling on the unity-gain frequency of the MOSFET. In the 180 nm technology, a given frequency, e.g.,  $f_T = 10$  GHz requires the transistor to operate in moderate inversion ( $i_f \approx 6$ ), while for a more advanced node such as the 65 nm, the same frequency is obtained for a transistor operating in weak inversion ( $i_f \approx 0.4$ ), which strengthens the importance of the subthreshold design as the semiconductor industry evolves. Although it was used a first-order approximation without the specific technology parameters of each node to calculate the frequency, one can observe that the frequency range (from MHz to GHz) of the subthreshold regime is appropriate for designing analog, radio-frequency and digital integrated circuits.

Up to this point, the importance of subthreshold design was discussed based on the MOS scaling. Another well-known technique, called voltage scaling also benefits from subthreshold design, this technique has been used to reduce power consumption over the last twenty years without the necessity to use an advanced technology node to design a circuit under severe power constraints, as extensively reviewed in [10]. The critical parameter in the design space of the voltage scaling technique is the supply voltage.

Considering digital CMOS circuit design, the supply voltage has a quadratic relationship with the dynamic power. i.e.,  $P_{dyn} \propto V_{DD}^2$  and a linear dependency with the idle power, i.e.,  $P_{idle} \propto V_{DD}$ . Therefore, to achieve the minimum power consumption  $(P_{min})$ , a circuit must operate at the minimum supply voltage  $(V_{DDmin})$ . As it was investigated by Calhoun et al. [11], there is a minimum energy point (MEP) of operation, near  $V_{DD} \approx 200 \text{ mV}$  - 300 mV, that depends on both the application and the technology. This optimal point of energy occurs for an optimum balance between dynamic and leakage energy.

Systems operating at the MEP may satisfy the demands of power constraint applications; however, depending on the circuit switching activity, power consumption in the idle state can be a significant or even the dominant part of the entire power consumption, as pointed out in [2]. Thus, a digital system being operational near the supply voltages given by energy harvesting sources, e.g., of the order of 100 mV or even lower, as showed in [12] - [13], will be vital to the wireless sensor nodes and implantable devices [13].

The region of operation for  $V_{DD} \leq 200 \text{ mV}$  will be called the ultra-low-voltage (ULV) domain in this work. Although the applications of ULV circuits are recent [14] - [15], we can go back to 1972 when the study of an inverter operating in the subthreshold region was pioneered by Swanson and Meindl [7]. Due to the limitations of the technology of the early 1970s, they estimate that the minimum supply voltage was around  $8\phi_t$  or 200 mV at 300K. Later in 2000, Meindl and Davis [16] derived the fundamental limit of operation of an inverter in CMOS technology, which is 36 mV at 300K. One year later, in 2001, Bryant et al. designed a CMOS inverter operating at  $V_{DD}$ = 100 mV in [17]. In 2018 Melek et al. [18] derived the fundamental limit of operation of an Schmitt trigger inverter, which is 31.5 mV at 300K. The interest in the ULV domain keeps on, as demonstrated in recent papers [19] - [20], which can be applied to the design of the fundamental blocks of digital integrated systems: the standard cells, as shown in [21].

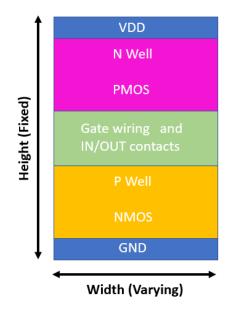

A standard cell is a network of transistors and interconnections arranged in a particular pattern to yield a Boolean logic function, e.g., NOT, AND, OR, NAND, NOR. The synthesis of the desired digital circuit is done by translating the behavioral language into the netlist created with the standard cell. A minimalist number of cells (NOT, NAND or NOR) can implement any digital system due to the universal propriety of these gates. A standard cell library (SCL) is a collection of cells designed in a standard way, e.g., with one of its dimensions fixed, specific supply voltage ( $V_{DD}$ ), and process technology, such as a brick in civil engineering.

Until now, the necessity and advantage of ULV design are mentioned for the feasibility of batteryless systems with extremely low power consumption. However, there is a significant problem in the subthreshold design: the impact of process variations in the ULV design [22]. The drain current of the metal-oxide-semiconductor field-effect transistor (MOSFET) in the subthreshold region has an exponential dependence on the threshold voltage  $V_{TO}$  [9].  $V_{TO}$

depends on technology, aspect ratio, temperature, and process. Due to the exponential behavior, any minor shift in the threshold voltage significantly impacts the drain current; thus, increases the variability in the delay and power consumption of the digital circuit, as presented by Vittoz in chapter 16 of [23].

This work proposes designing and implementing an ultra-low-voltage minimalist standard cell library using a commercial 180 nm CMOS technology while addressing the process variation issue with transistor-level design.

### 1.1 OBJECTIVES

Driven by the opportunities and challenges in the ULV domain, this research aims to investigate a minimalist SCL, which consists of a basic set of combinational logic gates: NOT, NAND, NOR, AOI, OAI, and a sequential logic gate: a D-Flip-flop, operating in the subthreshold region.

The specific objectives of this work are:

- Design and implementation of a minimalist standard cell library operating at the supply voltage  $V_{DD}$  = 100 mV while maintaining the robustness of the logic circuits.

- Investigate the minimum supply voltage of a frequency divider designed with the custom SCL.

- Investigate the yield and the maximum frequency of a frequency divider operating at 100 mV.

### 1.2 WORK ORGANIZATION

The overall structure of this dissertation takes the form of five chapters, including this introductory chapter. Chapter 2 briefly introduces the basis of transistor-level design. The third chapter presents a methodology to develop the standard cell library. Chapter 4 evaluates the ultra-low-voltage minimalist standard cell library using frequency dividers as a testbench. Finally, chapter 5 concludes with a brief state-of-the-art summary, findings, and future research.

### 2 TRANSISTOR LEVEL DESIGN

An intuitive, easy-to-use MOSFET model is essential for designing integrated circuits. In this work, we are confined to the subthreshold region of the MOS transistor; thus, in this chapter, we will briefly overview the behavior of the MOSFET in the ULV domain and the significant parameters of the model. Also, this chapter will briefly review the traditional CMOS inverter and the Schmitt trigger, which are the essential components of the standard cell library.

#### 2.1 MOSFET MODELING

Although BSIM [24] -[25] has been vastly used as the primary MOSFET model to simulate MOS circuits in EDA tools, the complexity of its calculations and numerous parameters opens a gap between circuit simulation and hand-design [26] - [27], complicating the understanding of how the main MOSFET parameters relate to the simulation results. Therefore, incorporating inversion charge-based models based on physics in the simulators simplifies the action of design

In the fast-expanding ultra-low-voltage domain [20], some short-channel effects, such as velocity saturation, are not relevant; thus, a simplified MOSFET model can be satisfactory for circuit design. Targeting the ultra-low-voltage designs, this work uses a 4-parameter model (4PM) [28] - [29] based on the all-region Advanced Compact MOSFET model (ACM) [30]-[31].

### 2.1.1 The 4-parameter model

The Advanced Compact MOSFET model describes the electrical behavior of MOS transistors in all regions of operation.

The three main parameters of the ACM model are the specific current  $I_S$ , the threshold voltage  $V_{T0}$ , and the slope factor n. Though these three parameters are usually enough to design a large set of circuits, a secondary effect called the drain-induced barrier lowering (DIBL) [32] completes the 4-parameter model. Despite being a very pronounced effect for short-channel transistors, the DIBL is also relevant for long-channel transistors in weak inversion. For long channel transistors in strong inversion (out of the scope of this work), DIBL is overshadowed by channel length modulation.

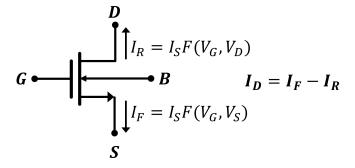

Figure 2 presents the symbol of an N-channel MOSFET (NMOS) transistor and its four terminals: gate (G), source (S), drain (D), and bulk (B). In this work, the bulk terminal is always grounded for the NMOS transistor and tied to  $V_{DD}$  for the PMOS transistor. For this reason, the bulk terminal will be omitted in the main text of this dissertation.

Figure 2 – Symbol of the NMOS transistor.

Source – The Author.

In the ACM model, the drain current  $I_D$  can be written as the difference between the forward  $(I_F)$  and reverse  $(I_R)$  currents, both dependent on the voltage  $V_{GB}$ , as illustrated in Figure 2.  $I_F$  is also dependent on  $V_{SB}$ , while  $I_R$  is dependent on  $V_{DB}$ . Equation (6) shows the MOS source-drain symmetry.

$$I_D = I_F - I_R = I_S \ (i_f - i_r)$$

(6)

The specific (or normalization) current  $I_S$  is dependent on both geometry and technological parameters as given by (7), where  $\mu$  is the carrier mobility,  $C_{ox}$  is the oxide capacitance per unit area,  $\phi_t$  is the thermal voltage, n is the slope factor, W is the width and L is the length of the transistor channel.

$$I_S = \mu C_{ox} n \frac{\phi_t^2}{2} \frac{W}{L} \tag{7}$$

The normalized form of the unified current-control model (UICM), expressed in Equation (8), establishes the relationship between the terminal voltages and the forward (reverse) inversion levels  $i_{f(r)}$ . As a rule of thumb [9], the transistor operates in weak inversion (WI) up to  $i_f = 1$  and in strong inversion (SI) for  $i_f > 100$ . The intermediate values of  $i_f$ , from 1 to 100, characterize moderate inversion (MI).

$$I_{F(R)} = I_S F \left[ \frac{V_P - V_{S(D)}}{\phi_t} \right]$$

(8a)

$$F^{-1} = \sqrt{1 + i_{f(r)}} - 2 + \ln\left(\sqrt{1 + i_{f(r)}} - 1\right)$$

(8b)

An useful approximation of the pinch-off voltage  $V_P$  is given by Equation (9), where  $V_{T0}$  is the equilibrium threshold voltage that corresponds to the gate voltage for which  $V_P = 0$

and  $\sigma$  is the magnitude of the DIBL coefficient. In the 4PM model, the DIBL effect comply with the MOSFET symmetry.

$$V_P = \frac{V_{GB} - V_{T0} + \sigma V_{DB} + \sigma V_{SB}}{n} \tag{9}$$

### 2.1.2 Subthreshold operation

In the ULV domain, the MOSFET operates in the subthreshold regime only (  $i_{f(r)} \ll 1$ ). Thus, Equation (8) simplifies to Equation (10), which has an exponential relationship between the control voltages and the forward (reverse) inversion levels.

$$i_{f(r)} = 2e^{\frac{V_P - V_S(D)}{\phi_t} + 1}$$

(10)

Using Equations (6) and (10), one can express the well-known drain current of the MOS in the subthreshold region (11).

$$I_{DN(P)} = I_{N(P)} e^{\frac{V_{GB(BG)} + \sigma \left(V_{DB(BD)} + V_{SB(BS)}\right)}{n_{N(P)}\phi_t}} \left(e^{\frac{-V_{SB(BS)}}{\phi_t}} - e^{\frac{-V_{DB(BD)}}{\phi_t}}\right)$$

(11a)

$$I_{N(P)} = 2I_{SN(P)}e^{\frac{-|v_{TON(P)}|}{n_{N(P)}\phi_t} + 1} = I_{ON(P)}e^{\frac{-|v_{TON(P)}|}{n_{N(P)}\phi_t}}$$

(11b)

The current scaling factor  $I_{N(P)}$  represents the strength of the device, which depends on the main technological parameters and the dimensions of the transistors.

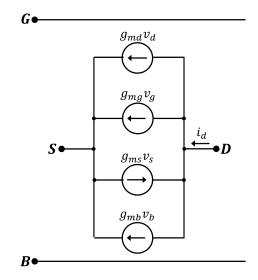

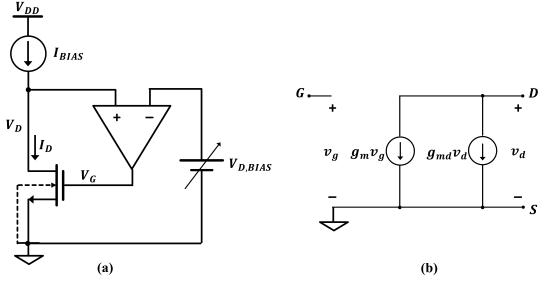

### 2.1.3 Small-Signal Transconductances

The small-signal transconductances are essential for both the design of integrated circuits and the extraction of the four transistor parameters [29]. As the MOSFET transistor is a 4-terminal device, Figure 3 presents the low-frequency small-signal model for the MOSFET, in which the voltage variation in each of its terminals will contribute to the variation of the drain current  $(I_D)$ .

Figure 3 – Low-frequency small-signal model of the MOSFET.

Source – The Author.

The differentiation of the drain current  $I_D$  with respect to  $V_G$ ,  $V_S$ , and  $V_D$  gives us the small-signal transconductances  $g_{mg}$ ,  $g_{ms}$ , and  $g_{md}$  respectively, as shown in (12).

$$g_{mg} = \frac{\partial I_D}{\partial V_G}; g_{ms} = -\frac{\partial I_D}{\partial V_S}; g_{md} = \frac{\partial I_D}{\partial V_D}; g_{mb} = \frac{\partial I_D}{\partial V_B}$$

(12)

If we take the particular case where all the terminals of a MOSFET increase the voltage by the same amount, the change in  $I_D$  would be 0, as shown in (13).

$$g_{mg} - g_{ms} + g_{md} + g_{mb} = 0 \tag{13}$$

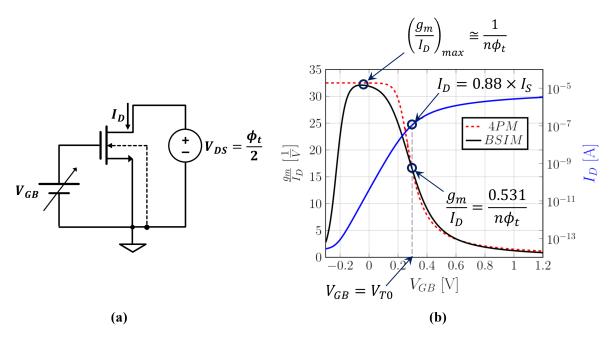

The vital relationships to design integrated circuits are the transconductance-to-current ratios. Applying the partial derivatives of (12) to the 4-parameter UICM (8), we have the relationship between the transconductances and the inversion levels. The thorough expressions of the transconductances and transconductance-to-current ratios are investigated in [29]. In this work, we will use two fundamental relationships to extract the four parameters of the model, the gate transconductance-to-current ratio (14) and the ratio of the gate to the drain transconductance in saturation (15). Annex A presents the parameter extraction method.

$$\frac{g_m}{I_D} = \frac{2}{n\phi_t(\sqrt{1+i_f} + \sqrt{1+i_r})}$$

(14)

$$\frac{g_m}{g_{md}} = \frac{1}{\sigma} \tag{15}$$

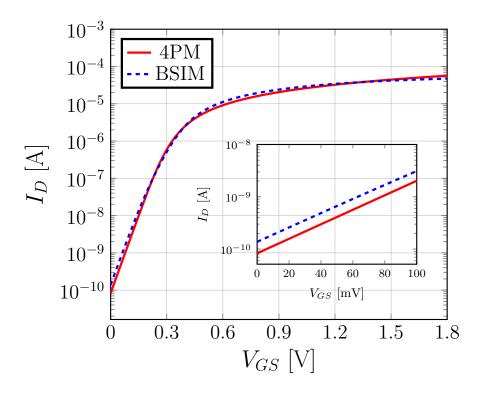

### 2.1.4 4PM vs BSIM

This section will present a brief overview of the two most significant IV curves of the MOS transistor with a comparison of the 4PM and the BSIM model. The fully detailed implementation and comparison between the models have been carried out in [29].

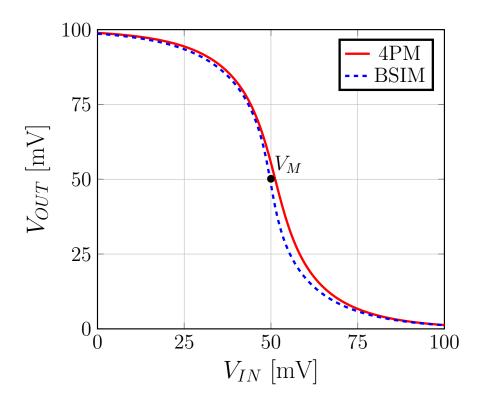

Figure 4 presents the  $I_D$  vs  $V_{GS}$  at  $V_{DS} = 100$  mV. Overall, this IV characteristic resulted in a 4PM curve close to BSIM's curve throughout the  $V_{GS}$  range. In the zoom from 0 to 100 mV, one can see the difference in the drain current between the models.

Figure 4 –  $I_D \times V_{GS}$  @  $V_{DS}$ = 100 mV of an NMOS transistor, BSIM vs 4PM.

Source - The Author.

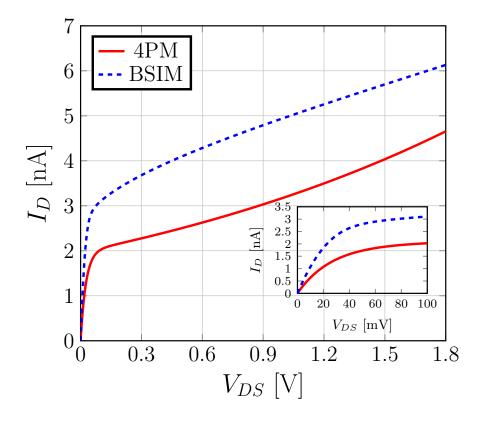

The  $I_D$  vs  $V_{DS}$  at  $V_{GS} = 100$  mV characteristic was also simulated, as shown in Figure 5. One can see difference between the model's curves, mainly because only one short-channel effect (DIBL) is included in the 4-parameter model.

Figure 5 –  $I_D \times V_{DS}$  @  $V_{GS}$ = 100 mV of an NMOS transistor, BSIM vs 4PM.

Source - The Author.

Indeed, the 4PM model is far less complicated than the BSIM4.5 model [33],with only four parameters (n, $V_{TO}$ ,  $I_S$  and  $\sigma$ ) as shown in (8). In this work, we will use the 4PM model implemented in [29] and compare some simulations on Cadence Virtuoso<sup>©</sup> with those obtained with the BSIM 4.5 model available on the process design kit (PDK) of the 180 nm technology node.

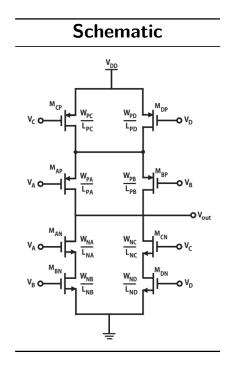

### 2.2 THE ULV INVERTER

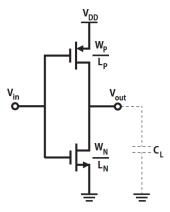

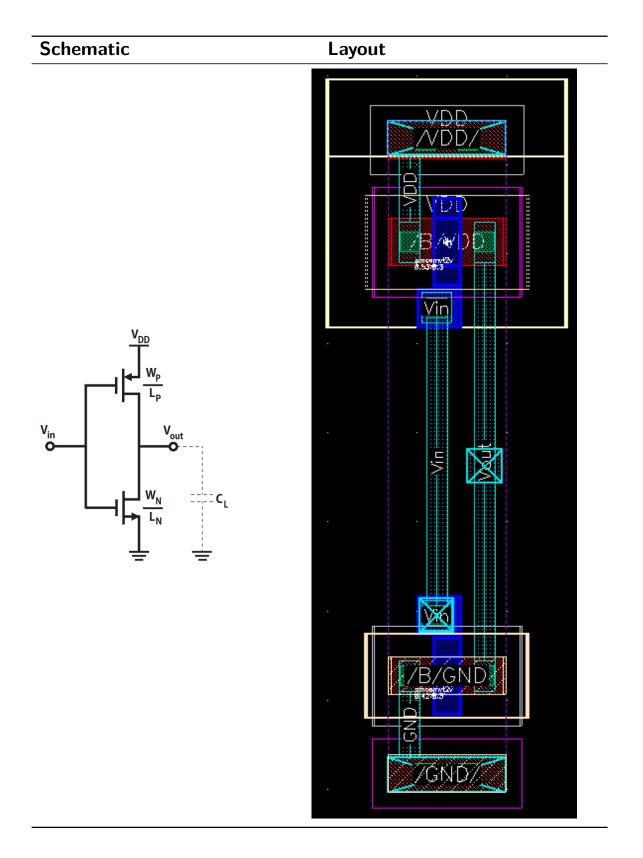

The CMOS inverter, shown in Figure 6, is the fundamental building block of any digital system [34], the analysis of CMOS inverters can be extended to explain the behavior of more complex gates such as NAND, NOR, AOI, or OAI. Despite being well-known, we will briefly overview in this section the characteristics of the classical CMOS inverter in the ULV domain.

### 2.2.1 Voltage transfer characteristic

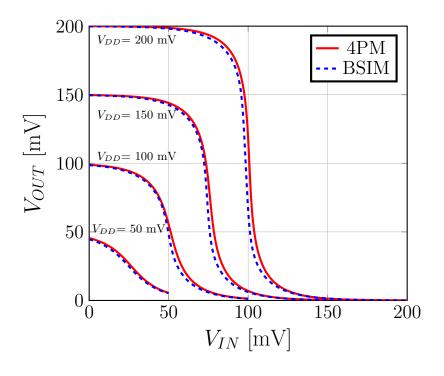

The essential characteristic of the CMOS inverter is its regenerative property that leads to well-defined logic levels, even in the ULV domain [16], operating at a supply voltage of 100 mV, as shown in Figure 7.

Figure 6 – CMOS Inverter with a equivalent load capacitance  $C_L$ .

Source – The Author.

Figure 7 – Voltage transfer characteristic of the CMOS inverter for different values of supply voltages.

Source – The Author.

The analysis of the voltage transfer characteristic (VTC) of the CMOS inverter conducted in [35] points out that the inverter threshold voltage ( $V_M$ ), defined as the voltage such that  $V_{IN} = V_{OUT}$ , shows dependence on the supply voltage, on technological parameters, and on transistors strength ratios, as shown in Equation (16).

$$V_M \approx \frac{V_{DD}}{2} + \frac{\frac{V_{TON} - V_{TOP}}{2} + \frac{n\phi_t}{2} ln\left(\frac{I_{OP}}{I_{ON}}\right)}{1 + \frac{e^{\frac{V_{DD}}{2\phi_t}} - 1}{n}}$$

(16)

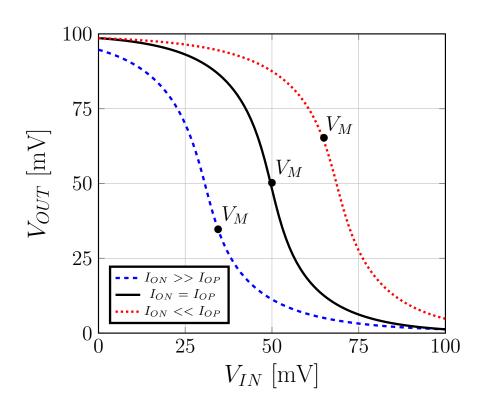

If the PMOS transistor is stronger than the NMOS transistor, then  $V_M > \frac{V_{DD}}{2}$  and, if the NMOS transistor is stronger than the PMOS transistor, then  $V_M < \frac{V_{DD}}{2}$ . From (16), it can be noted that the imbalance between the PMOS-NMOS transistors can be compensated with proper sizing. The imbalance of the networks can be also evaluated by the imbalance factor (IF), which is defined as the transistor current strength ratio  $I_{OP}/I_{ON}$ , as illustrated in Figure 8.

Figure 8 – VTC dependence on the imbalance factor.

Source - The Author.

### 2.2.2 Power dissipation

Melek et al. conducted a deep analysis of the CMOS inverter in [35]; the static and dynamic characteristics, as well as power dissipation, were analyzed.

The total power dissipation  $P_{tot}$  of the CMOS inverter consists of 3 components:

dynamic power, short-circuit power, and static power, as shown in Equation (17).

$$P_{tot} = P_{dyn} + P_{sc} + P_{stat} \tag{17}$$

The dynamic power  $P_{dyn}$  is dependent on the switching frequency  $(f_{switch})$ , activity factor ( $\alpha$ ), load capacitance  $(C_L)$  and quadratic dependent of the supply voltage, as shown in (18).

$$P_{dyn} = \alpha C_L V_{DD}^2 f_{switch} \tag{18}$$

The short-circuit power  $P_{sc}$  given in (19), is due to the simultaneous conduction of the PMOS and NMOS transistors.  $P_{sc}$  is linearly dependent on  $V_{DD}$ .

$$P_{sc} = V_{DD} \left(\frac{1}{T_{sc}}\right) \int_0^{T_{sc}} I_{SC} dt$$

(19)

where  $I_{SC}$  is the short circuit current and  $T_{sc}$  is the period of conduction of  $I_{SC}$  .

The static power  $P_{stat}$ , in (20), is independent of the frequency. However, it is dependent on the leakage current  $I_{LK_{N(P)}}$ , which has the same magnitude as  $I_{N(P)}$ , and is also dependent on the supply voltage.

$$P_{statN(P)} = I_{LKN(P)} V_{DD}$$

<sup>(20)</sup>

Static power is the dominant power in low-frequency applications, such as ULV domain systems [2]. In this work, the static power at  $V_{DD} = 100$  mV can be further reduced by properly balancing the inverter, i.e.,  $I_N = I_P$ , and by selecting appropriate transistors in the available CMOS technology, which will be discussed in detail in chapter 3.

### 2.2.3 Delay

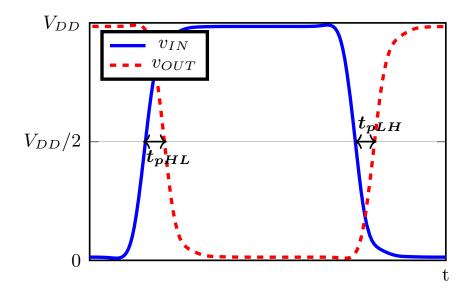

Indeed, the power dissipation in the subthreshold region is reduced by a lower supply voltage. However, the propagation delay  $t_p$  of the CMOS inverter increases exponentially [35], as shown in Equation (22). The inverter delay is defined as the maximum of the low-to-high  $t_{p_{LH}}$  and high-to-low  $t_{p_{HL}}$  delays, i.e., the worst-case scenario, as shown below.

$$t_p = \max\left(t_{p_{LH}}, t_{p_{HL}}\right) \tag{21}$$

The delay  $t_{p_{LH(HL)}}$  is defined as the time it takes for the output voltage to switch from low-to-high (high-to-low), reaching the midpoint between the low and high logic levels,

i.e., 50% of  $V_{DD}$  in our CMOS logic case, after the input voltage switches from high-to-low (low-to-high). Figure 9 illustrates the definition of the delays.

Figure 9 – Definition of  $t_{p_{HL(LH)}}$  and  $t_{p_{HL(LH)}}$  of the CMOS inverter.

Source – The Author.

$$t_{pHL(LH)} = \frac{V_{DD} \left( 0.5 + ln \left( \frac{1 - e^{-\frac{V_{DD}}{2\phi_t}}}{1 - e^{-\frac{V_{DD}}{\phi_t}}} \right) \right)}{2e^{1\frac{I_{S_N(P)}}{C_L}} e^{\frac{V_{DD} - V_{TO_N(P)}}{n_{N(P)\phi_t}}}}$$

(22)

The delay of a CMOS inverter can also be calculated by measuring the oscillation frequency  $f_{osc}$  of a ring oscillator (ROSC). Equation (23) presents  $t_p$  in terms of the number of stages (N) and the  $f_{osc}$  of a ROSC.

$$t_p = \frac{1}{2Nf_{osc}} \tag{23}$$

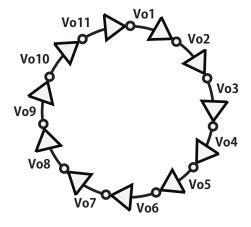

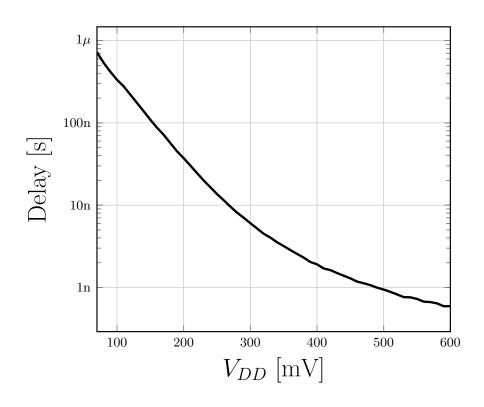

The ring oscillator shown in Figure 10 consists of an odd number of inverters in a loop. Following the guidelines for ULV ring oscillators discussed in [36], we chose the number of stages N=11. Figure 11 shows the delay of an inverter as a function of  $V_{DD}$ . One can observe that the subthreshold delay increases exponentially as the supply voltage decreases, in agreement with Equation (22).

# Figure 10 – Ring Oscillator schematic

Source – The Author.

Figure 11 – Delay of an inverter vs  $V_{DD}$  in the 180 nm technology, with  $\frac{W_N}{L_N} = \frac{420 \ nm}{300 \ nm}$  and  $\frac{W_P}{L_P} = \frac{530 \ nm}{300 \ nm}$

Source – The Author.

#### 2.2.4 Power-delay-product

Another figure of merit evaluated in digital circuits is the power-delay-product (PDP). As the name implies, the PDP is the product of the total power dissipation ( $P_{tot}$ ) and the propagation delay ( $t_p$ ), as shown in Equation (24). It indicates the energy consumed per switching event by the CMOS circuit [23].

$$PDP = P_{tot}t_p \tag{24}$$

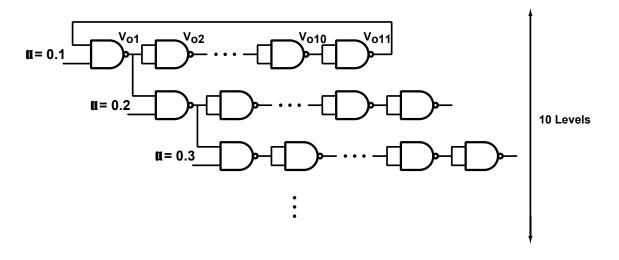

The design of subthreshold digital circuits with minimal energy consumption has been studied in detail by Wang et al. in [37], as well as the advantages of voltage scaling in CMOS logic and the dependence of the energy per switching event on the activity factor ( $\alpha$ ). In this work, the variable activity factor circuit presented in Chapter 4 of [37] was implemented using only NAND gates in the 180 nm technology. The circuit consists of 10 levels of 11 cascaded NAND gates, with the first level being a ring oscillator that drives the other branches when activated, as shown in Figure 12. The logic depth increases when one more branch is enabled, which is similar to the behavior of a processor pipeline. Also, by allowing one more level to operate, the activity factor increases 10%. The circuit is simulated through  $V_{DD}$  sweeps to determine the relationship between the PDP and the activity factor.

Figure 12 – Schematic of the variable activity factor circuit

Source - The Author.

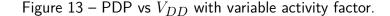

Figure 13 shows the energy per switching event (PDP) of the variable activity factor circuit as a function of the supply voltage. As mentioned earlier, lowering  $V_{DD}$  reduces the total power of a CMOS logic circuit, mainly due to the dynamic power component. However, lowering  $V_{DD}$  also exponentially increases the propagation delay, according to Equation (22), which leads to a minimum energy point in the PDP, even in the ULV domain.

Therefore, it is possible to control the  $V_{DD}$  to which the MEP occurs by simply increasing the activity factor which increases the dynamic power. For instance, the results in Figure 12 show the MEP shifts from  $V_{DD} \approx 200 \text{ mV}$  to 100 mV as  $\alpha$  increases from 0.1 to 1. This circuit is just one example of the relationship between the activity factor and the minimum energy point for CMOS logic, and it demonstrates the importance of determining the logic depth to design ULV systems with minimum energy consumption.

Source – The Author.

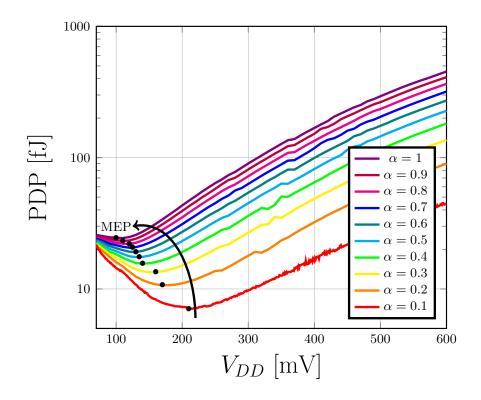

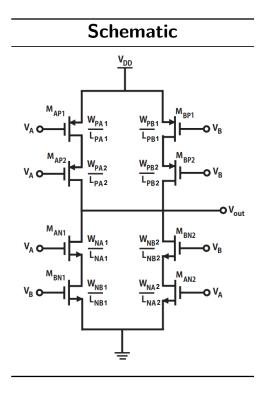

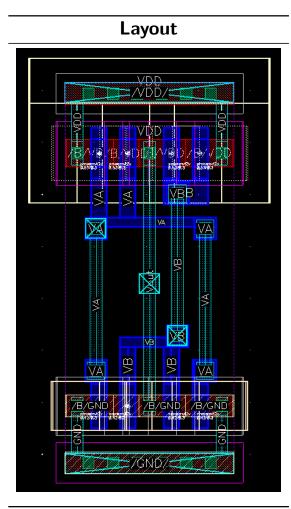

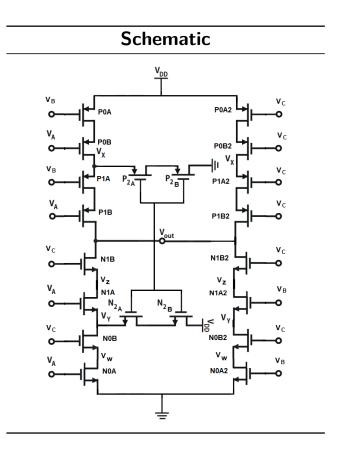

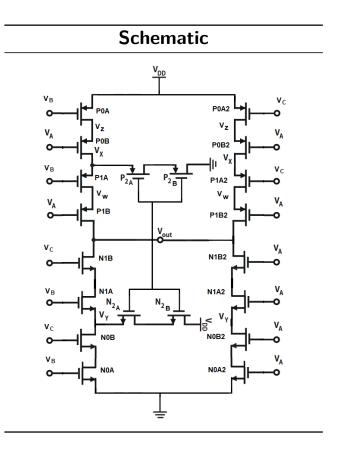

#### 2.3 THE ULV SCHMITT TRIGGER

This section presents a brief overview of the design of a ULV Schmitt-trigger (ST), which was extensively investigated in [38] - [18]. Figure 14 shows the voltage transfer characteristic (VTC) of a CMOS Schmitt trigger with balanced PMOS and NMOS subcircuits under ULV operation [18]. The voltage transfer characteristic shows hysteresis for  $V_{DD} = 100 \text{ mV}$  but not for  $V_{DD} = 70 \text{ mV}$  and  $V_{DD} = 50 \text{ mV}$ . As demonstrated in [38], the ST of Figure 14 cannot theoretically present hysteresis for supply voltages below 75 mV due to the lack of voltage gain. In practice, due to the non-perfect balance between the NMOS and PMOS networks and slope factors larger than unity, hysteresis can only appear for over 100 mV of supply. As mentioned in Subsection 2.1.2, the transistor current scaling factor,  $I_{N(P)}$ , in Equation (11b), represents the transistor strength, is dependent on both the technology parameters and dimen-

sions. For a balanced (symmetrical) ST,  $I_{N0} = I_{P0} = I_0$ ,  $I_{N1} = I_{P1} = I_1$ ,  $I_{N2} = I_{P2} = I_2$ and  $n_N = n_P = n$ .

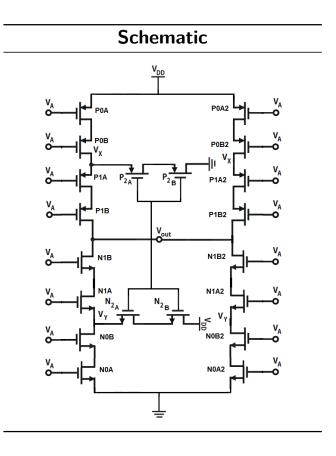

Figure 14 - Voltage transfer characteristics of the symmetrical CMOS Schmitt trigger

Source - [38]

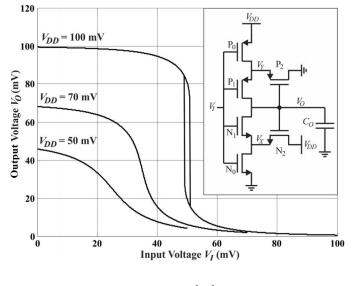

The voltage gain of the ST circuit around  $V_{DD}/2$ , given by (25) [38], is a function of the supply voltage  $V_{DD}$  and ratios  $I_1/I_0$  and  $I_2/I_0$ . Figure 15 shows the gain calculated using Equation (25) for  $V_{DD} = 60$  mV. This low voltage was selected in order to explore the limits of the design space. The value of  $I_1/I_0 = I_2/I_0 = 0.5$  was chosen for layout convenience.

$$\frac{v_o}{v_i} = \frac{\left(2 + \frac{I_0}{I_2} + \frac{I_1}{I_2} - \frac{I_2}{I_0}e^{\frac{-V_{DD}}{\phi_t}}\right)\left(1 - e^{-\frac{V_{DD}}{2\phi_t}}\right)}{1 - \left(2 + \frac{I_0}{I_2} + \frac{I_1}{I_2} + \frac{I_2}{I_0}\right)e^{\frac{-V_{DD}}{2\phi_t}} - \left(1 + \frac{I_1}{I_0}\right)e^{\frac{-V_{DD}}{\phi_t}}}$$

(25)

Figure 15 – Voltage gain of the ST inverter as a function of  $I_2/I_0$ .

Source – The Author.

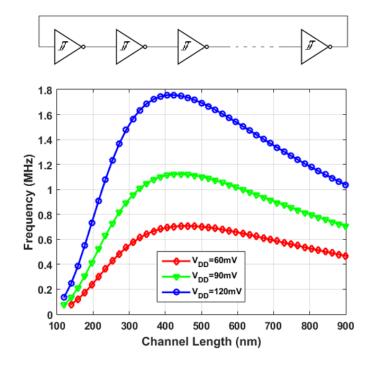

The channel length is determined through the simulation results for the operating frequency of an ST-based 11-stage ring oscillator [36]. Due to the reverse short-channel effect (RSCE), in WI, the maximum operating frequency does not occur for the minimum channel length [36], [39], as shown in Figure 16.

Figure 16 – Oscillation frequency as a function of the channel length.

Source - The Author.

For the 130 nm technology, the ratio of the widths of the corresponding p- and nchannel transistors is 5 to 1 to balance their current strengths for a supply voltage of 90 mV. The 180 nm technology did not present the RSCE, thus the minimum length will be used in the design.

Another significant characteristic of the ST inverter is that it is less sensitive to technology parameter variations than the conventional inverter since both the pull-up and pull-down circuits are composed of both nMOS and pMOS [38] transistors. Consequently, the robustness of the ST logic can be much higher than that of the conventional logic in ULV operation.

In [40], the design of an 8x8 multiplier based on the ST standard cell library was investigated with different cell strengths and additional layout area, with one sample operating at the extremely low voltage of 62 mV. Also, in [40], Lotze et al. investigate the static noise margin, on-to-off current ratio, temperature dependence, and operation frequency of the Schmitt Trigger. The ST was superior to the traditional CMOS inverter in almost all of those design spaces. However, the ST is slower than the CMOS inverter at the same supply voltage.

In this work, the ST will be used as a comparison to the CMOS inverter as a fundamental building block of a SCL to operate in the ULV domain.

#### **3 STANDARD CELL DESIGN IMPLEMENTATION**

Robustness is fundamental in any digital system [34]. It is well known that ultra-low-voltage design has a degraded performance [2] compared with the drift-dominant strong inversion design. Yet, while digital logic may function at extremely low voltages, another problem arises: the variability of the process fabrication [2]. This chapter will discuss the design of standard cells driven by variability awareness in subthreshold operation.

#### 3.1 ADDRESSING VARIABILITY

The MOS parameters ( $V_{TO}$ ,  $I_S$ , n,  $\sigma$ ) are affected by the fabrication process due to variations in the device geometry, and random dopant fluctuations [9]. The MOSFET operating in the subthreshold regime is very sensitive to the threshold voltage due to the exponential relationship between the  $V_{TO}$  and the drain current, as shown in Equation (11).

The fabrication process variations can be classified into two major categories: mismatch and process. The mismatch variation is due to individual (local) device variations, and the process variations occur as a group (die-to-die, wafer-to-wafer) [9].

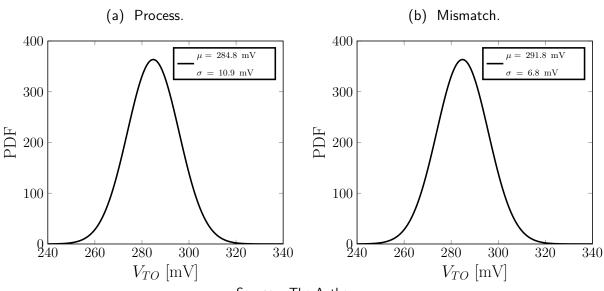

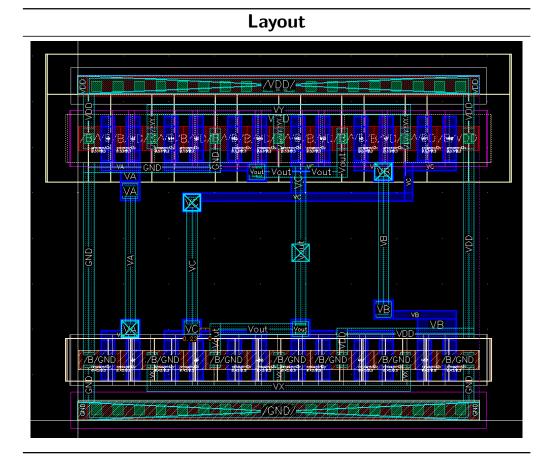

With the parameter extractor circuit from Figure 42a in Annex A, Monte Carlo simulations of an NMOS transistor using the BSIM4 MOS model were conducted to observe the  $V_{TO}$  variability due to mismatch and process. Figure 17 shows the result of 2000 samples Monte Carlo simulations. The dimensions of the NMOS were W = 420 nm and L = 300 nm. Figure 17a and 17b shows the variability of  $V_{TO}$  with respect to the process and mismatch, respectively.

Figure 17 – Distributions of the threshold voltage of an NMOS transistor.

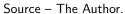

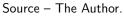

The standard deviations of  $V_{TO}$  in mismatch and process will have a considerate impact on the device drain current. Variations of the drain current of NMOS and PMOS transistors in a CMOS inverter will result in shifts in the VTC, as shown in Figure 18. Consequently, VTC shifts increase the logic cell's delay and total power variability.

Figure 18 – Impact of mismatch and process variation on VTC of the CMOS inverter at  $V_{DD}$ = 100 mV.

Source - The Author.

#### 3.1.1 Techniques to Improve Robustness

To address this variability  $(\sigma/\mu)$  problem of the threshold voltage, the design of the ULV standard cells will combine already known techniques to improve the robustness, i.e., minimize the shift in the VTC of the logic cell. Presented by Pelgrom et al. in [41], the first technique consists of increasing the area of a MOS transistor which will decrease the standard deviation of the threshold voltage due to mismatch, as shown in Equation (26).

$$\sigma_{V_{TO}} = \frac{A_{V_{TO}}}{\sqrt{WL}} \tag{26}$$

The second technique was introduced by Bjerkedok et al. in [42]; which instead of increasing only the W or L of the MOS transistor in a logic gate, they use a series association of MOS transistors called "slices".

Source – The Author.

The symmetry of the MOS transistor is suitable for making associations equivalent to a single device. Such associations can be series or parallel, as shown in Figure 20.

Figure 20 – MOS associations.

(a) Series association of 2 MOS transistors.

(b) Parallel association of 2 MOS transistors.

The associations of transistors with the same channel width and terminals connected in series allow the construction of a device equivalent to a single transistor. The length L of this device is the result of the sum of the unit channel lengths and a width W. On the other

hand, in parallel associations of transistors with the same channel length, we obtain a device with a width equivalent to the sum of the unit widths and a length L.

To model the series associations in the triode region, we consider the schematic shown in Figure 20a. The composition presented here consists of two NMOS transistors connected from node "X" connecting drain and source of N1 and N2, respectively, with the gate and substrate terminals common to both devices. The formal analysis presented in [43] using the gradual channel approximation allows us to write the drain current as a function of the applied potentials at the gate, source ( $V_G$ ,  $V_S$ ) and gate, drain ( $V_G V_S$ ) terminals, as expressed in the equation (27).

$$I(V_G, V_X) = \frac{\left(\frac{W}{L}\right)_{N1} I(V_G, V_D) + \left(\frac{W}{L}\right)_{N2} I(V_G, V_S)}{\left(\frac{W}{L}\right)_{N1} + \left(\frac{W}{L}\right)_{N2}}$$

(27)

From Equation (27) and using the ACM model we have that the drain current for a series composition of two transistors is

$$I_D = \left(\frac{W}{L}\right)_{eq} \left[I\left(V_G, V_S\right) - I\left(V_G, V_D\right)\right]$$

(28a)

$$\left(\frac{W}{L}\right)_{eq} = \frac{\left(\frac{W}{L}\right)_{N1} \left(\frac{W}{L}\right)_{N2}}{\left(\frac{W}{L}\right)_{N1} + \left(\frac{W}{L}\right)_{N2}}$$

(28b)

Equation (28) shows that the current obtained through the series association for transistors in linear region is similar to that obtained with a unitary transistor whose aspect ratio is equivalent. For example, in a series association of two unitary transistors (N1 = N2) the equivalent aspect ratio is

$$\left(\frac{W}{L}\right)_{eq} = \frac{\left(\frac{W}{L}\right)_{N1}}{2} \tag{29}$$

For the parallel association of 2 unitary MOS transistors of identical lengths, the equivalent width is  $W_{eq} = 2W_N$ . The methodology presented in this section can be used for the association of PMOS transistors.

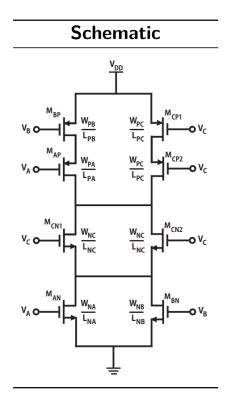

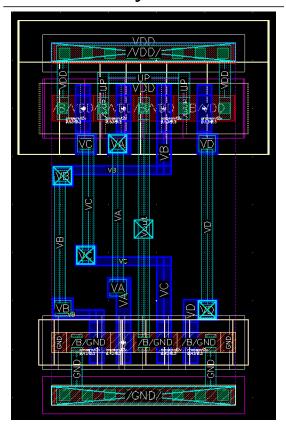

MOS association modeling can be used for the slice shown in Figure 19, which results in the transistor strength in each network being half of the strength of the CMOS inverter. Therefore, a single slice is equivalent to a CMOS inverter with half of the current strength. Using two slices connected, as seen in Figure 21, results in implementing the CMOS invertersliced, which has the same current strength as the conventional CMOS inverter.

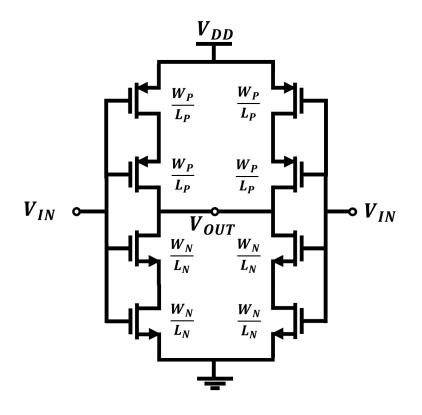

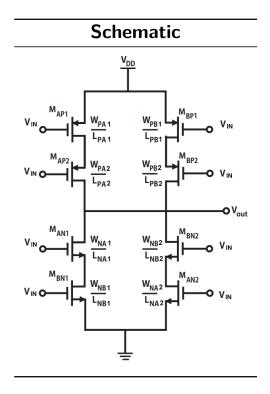

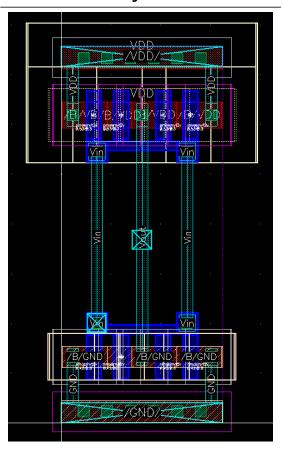

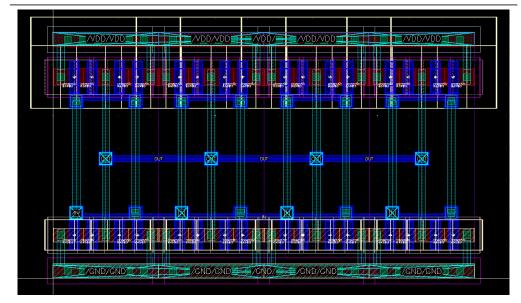

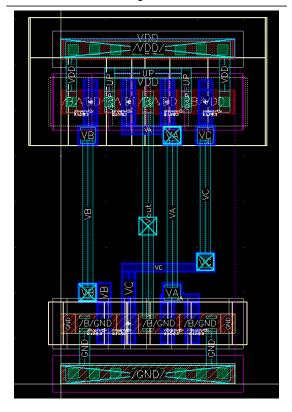

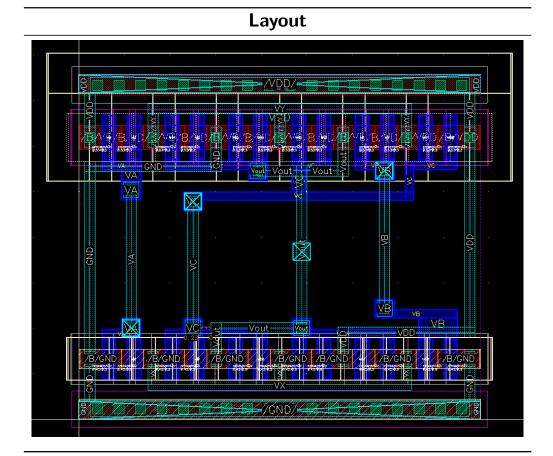

Figure 21 – Schematic of two Slices.

Source – The Author.

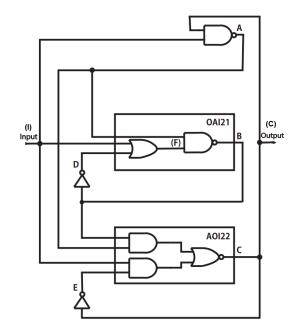

The two slices topology is extremelly versatile. In principle, one can implement any combinational logic function, which includes the traditional Boolean logic gates: NAND, NOR, XOR, XNOR, INV, AOI, OAI and so on.

For example with the truth table of the NAND gate, given in Table 2, the NAND with slices implementation is straighfoward by only changing the inputs of the two slices topology. The same method can implement the others Boolean gates.

| 4 | 1 | В | OUT |

|---|---|---|-----|

| ( | ) | 0 | 1   |

| ( | ) | 1 | 1   |

| ] | L | 0 | 1   |

| ] | L | 1 | 0   |

|   |   |   |     |

Table 2 – Truth table of the 2-input NAND gate.

Source – The Author.

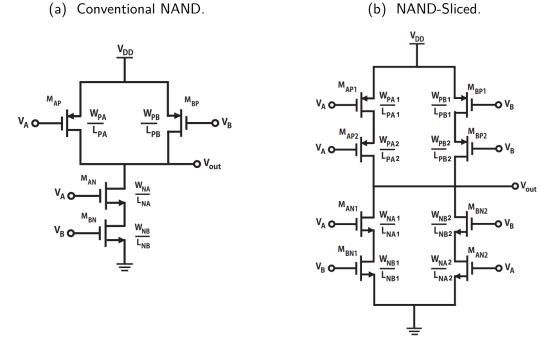

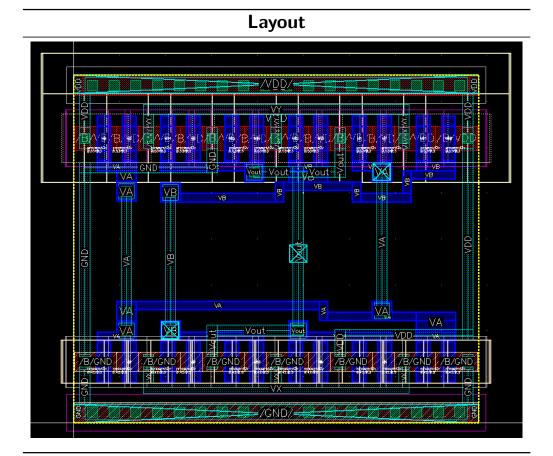

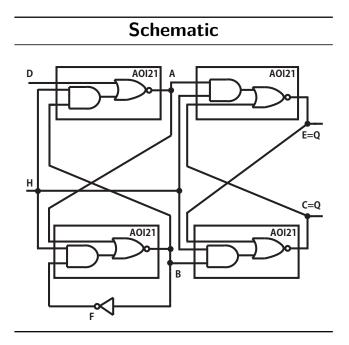

Figure 22a shows the conventional NAND CMOS and Figure 22b shows the application of the sliced technique in a NAND gate, called NAND-Sliced from now on.

Figure 22 – Schematic of the NAND logic gates.

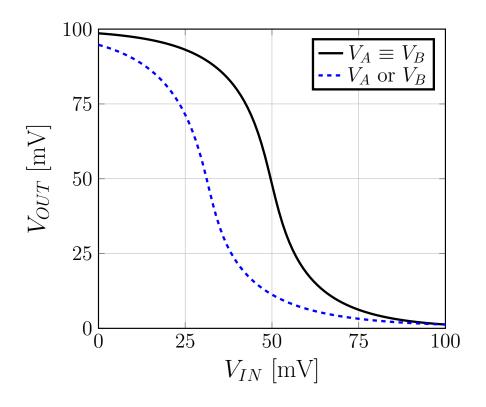

Figure 23 shows the result of 200 samples of Monte Carlo simulations with mismatch and process variations. Visibly, the sliced inverter topology decreases variability due to device mismatch.

Figure 23 – Comparison of VTCs of sliced and traditional CMOS inverter, from 200 samples of Monte Carlo: mismatch and process variations. Sliced from Figure 21. The dimensions of the transistors are :  $\frac{W_P}{L_P} = \frac{530 \, nm}{300 \, nm}$  and  $\frac{W_N}{L_N} = \frac{420 \, nm}{300 \, nm}$ .

Despite the increased robustness of the logic circuit, the use of the sliced technique has disadvantages regarding the total power dissipation and the delay of the cell; as it was explained in [42], the metrics of the sliced-based cells will be evaluated in section 3.4.

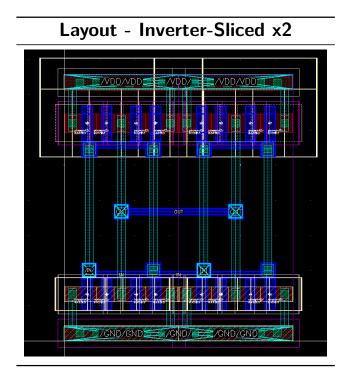

### 3.1.2 Schmitt trigger vs process corners