# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Ricardo Batista Peres

Implementação de PLL (*Phase Locked Loop*) Digital Para Transferência de Energia Sem Fio

| Ricardo B | atista Peres                                                                                                                                                                    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           | ed Loop) Digital Para Transferência de                                                                                                                                          |

| Energia   | Sem Fio                                                                                                                                                                         |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           | Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do título de Mestre em Engenharia Elétrica. |

|           | Orientador: Prof. Fabian Leonardo Cabrera Riano,<br>Dr                                                                                                                          |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

|           |                                                                                                                                                                                 |

## Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Peres, Ricardo Batista Implementação de PLL (Phase Locked Loop) Digital Para Transferência de Energia Sem Fio / Ricardo Batista Peres ; orientador, Fabian Leonardo Cabrera Riano, 2023.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2023.

Inclui referências.

97 p.

1. Engenharia Elétrica. 2. DPLL. 3. PLL. 4. CMOS. 5. Transferência de Energia Sem Fio. I. Riano, Fabian Leonardo Cabrera. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

#### Ricardo Batista Peres

# Implementação de PLL (*Phase Locked Loop*) Digital Para Transferência de Energia Sem Fio

O presente trabalho em nível de Mestrado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. Marcio Cherem Schneider, Dr. Universidade Federal de Santa Catarina

Prof. Roddy Alexander Romero Antayhua, Dr. Instituto Federal de Santa Catarina

Eng. Heider Marconi Guedes Madureira, Dr. Chipus Microeletrônica

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de Mestre em Engenharia Elétrica.

Prof. Telles Brunelli Lazzarin, Dr Coordenação do Programa de Pós-Graduação

Prof. Fabian Leonardo Cabrera Riano, Dr Orientador

Dedicado a minha esposa Mayara Santos Cayres, minha filha Sophia Cayres Peres, meu pai Antonio Peres Puga, minha falecida mãe Zulmira Maria Batista Peres e a toda família.

#### **Agradecimentos**

Primeiramente a Deus!

Ao professor Dr. Fabian Leonardo Cabrera Riano pela orientação e grande ajuda na pesquisa desenvolvida.

À Chipus Microeletrônica pela oportunidade concedida para a realização deste trabalho.

E a todos os colegas de trabalho que influenciaram, de alguma forma, este projeto.

#### Resumo

Nesta dissertação é apresentado um sintetizador de frequência para aplicações de transferência de energia sem-fio na frequência de 1 GHz. O sintetizador é baseado em uma malha de controle de fase com compensação digital (DPLL) usando oscilador em anel para menor impacto na área em silício. O circuito foi projetado na tecnologia CMOS 65 nm. A fundamentação teórica para o projeto de um DPLL é feita, partindo das características de PLLs convencionais, análises de estabilidade e ruído para o PLL tipo I e tipo II. Esses fundamentos são utilizados no projeto do DPLL e também dos blocos que o formam. O conversor de tempo para digital (TDC) projetado utiliza uma estratégia para aumentar a faixa de operação sem aumento significativo de área. Esse TDC gera sinais para o ajuste grosso e fino da malha de modo a reduzir o tempo de acomodação. Um oscilador controlado digitalmente é projetado usando um conversor digital-analógico em conjunto com um oscilador controlado por tensão. O divisor de frequência possui 4 valores para o módulo de divisão. Desta forma, poderá ser observado o comportamento dinâmico do DPLL na ocasião da medição do chip. É apresentado o projeto de malha para um DPLL tipo I. Nesse projeto de malha, a função de transferência do filtro é encontrada no domínio s e depois convertida para o domínio z utilizando a aproximação Backward Difference. Simulações nos ambientes digital, analógico e misto foram realizadas para verificar o correto funcionamento do circuito projetado. Também foi feito o leiaute do DPLL incluindo PADs, estruturas de depuração e buffers. O DPLL proposto atinge uma área de 0,06 mm<sup>2</sup>, um tempo de acomodação de 8 µs para um passo de frequência na saída de 128 MHz. O ruído de fase estimado é de -100 dBc/Hz na frequência de offset de 1 MHz. O consumo de potência foi estimado em 3,4 mW quando o DPLL opera em 1 GHz e tensão de alimentação de 1,2 V.

Palavras-chave: DPLL. PLL. Transferência de Energia Sem Fio. CMOS.

#### **Abstract**

This dissertation presents a frequency synthesizer for wireless power transfer applications at a frequency of 1 GHz. The synthesizer is based on a Digitally compensated Phase Locked Loop (DPLL) using a ring oscillator for less impact on silicon area. The circuit was designed using 65 nm CMOS technology. The theoretical basis for the design of a DPLL is made, starting from the characteristics of conventional PLLs, stability and noise analyzes for PLL type I and type II. These fundamentals are used in the design of the DPLL and also in the blocks that form it. The designed Time-to-Digital Converter (TDC) uses a strategy to increase the operating range without significantly increasing the area. This TDC generates signals for coarse and fine adjustment of the loop in order to reduce the settling time. A Digitally Controlled Oscillator is designed using a Digital-to-Analog Converter in conjunction with a Voltage-Controlled Oscillator. The frequency divider has 4 values for the division module. In this way, the dynamic behavior of the DPLL can be observed when measuring the chip. The loop design for a type-I DPLL is presented. In this loop design, the filter transfer function is found in the s-domain and then converted to the z-domain using the Backward Difference approximation. Simulations in digital, analog and mixed environments were performed to verify the correct functioning of the designed circuit. The DPLL layout was also designed including PADs, debug structures and buffers. The proposed DPLL achieves an area of 0.06 mm<sup>2</sup>, a settling time of 8  $\mu$ s for an output frequency step of 128 MHz. The estimated phase noise is -100 dBc/Hz at the offset frequency of 1 MHz. Power consumption was estimated at 3.4 mW when the DPLL operates at 1 GHz and a supply voltage of 1.2 V.

**Keywords**: DPLL. PLL. Wireless Power Transfer. CMOS.

### Lista de figuras

| Figura 1 — Exemplo basico de transferencia de energia sem fio                      | 16 |

|------------------------------------------------------------------------------------|----|

| Figura 2 - Sistema WPT com detalhes do transmissor                                 | 19 |

| Figura 3 – Diagrama de blocos de um PLL convencional                               | 20 |

| Figura 4 - Exemplo de um PLL tipo I entrando na condição de <i>lock</i>            | 22 |

| Figura 5 – Filtro de malha em PLL tipo I                                           | 25 |

| Figura 6 - Modelo para PLL tipo I                                                  | 26 |

| Figura 7 - Comportamento da função de transferência em malha aberta do PLL         |    |

| tipo I                                                                             | 26 |

| Figura 8 – Modelo de ruído do PLL tipo I                                           | 27 |

| Figura 9 – Diagrama de blocos de PFD+CP+LF                                         | 29 |

| Figura 10 – Modelo para PLL tipo II                                                | 30 |

| Figura 11 – Comportamento da função de transferência em malha aberta do PLL        |    |

| tipo II                                                                            | 31 |

| Figura 12 – Modelo de ruído do PLL tipo-II                                         | 32 |

| Figura 13 – Diagrama de blocos de um DPLL convencional                             | 34 |

| Figura 14 – Topologias base de osciladores, (a) oscilador LC e (b) oscilador em    |    |

| anel                                                                               | 37 |

| Figura 15 – Exemplo de filtro digital para DPLL (a) tipo I, (b) tipo II de segunda |    |

| ordem e (c) tipo II de terceira ordem                                              | 39 |

| Figura 16 – Detector de fase Bang-Bang de 1 bit                                    | 39 |

| Figura 17 – TDC convencional                                                       | 40 |

| Figura 18 – TDC Vernier                                                            | 41 |

| Figura 19 – TDC baseado em oscilador em anel                                       | 42 |

| Figura 20 – Estrutura de exemplo de um divisor multi módulo                        | 43 |

| Figura 21 – Domínio dos blocos existentes no DPLL                                  | 44 |

| Figura 22 – Diagrama de blocos do DPLL proposto                                    | 45 |

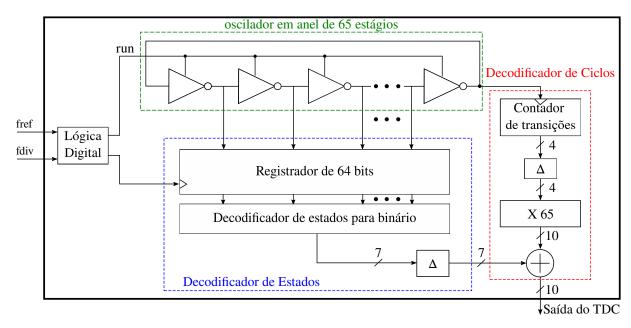

| Figura 23 – Diagrama de blocos do TDC sem o bloco de ajuste grosso                 | 46 |

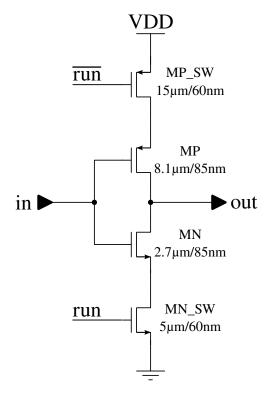

| Figura 24 – Elemento de atraso do oscilador em anel                                | 47 |

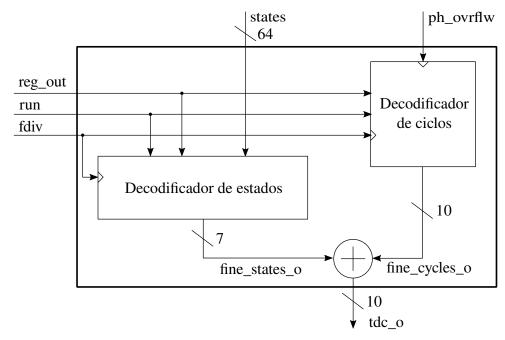

| Figura 25 – Diagrama de blocos do TDC                                              | 49 |

| Figura 26 – Circuito de ajuste FINO                                                | 50 |

| Figura 27 – Diagrama de blocos do decodificador de estados                         | 50 |

| Figura 28 – Decodificador de ciclos                                                | 51 |

| Figura 29 – Circuito de ajuste grosso                                              | 52 |

| Figura 30 – Circuito gerador dos sinais de controle                                | 52 |

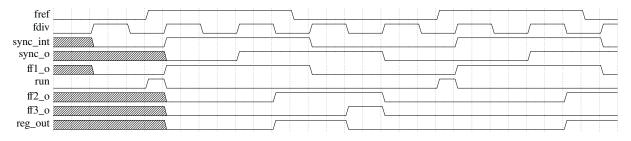

| Figura 31 – Formas de onda do circuito de controle                                 | 52 |

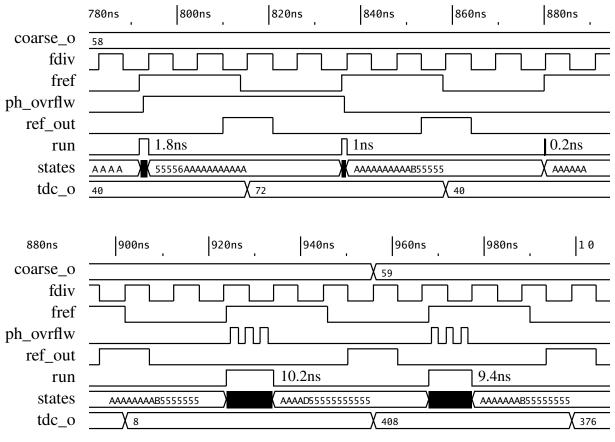

| Figura 32 – Sinais do TDC                                                          | 53 |

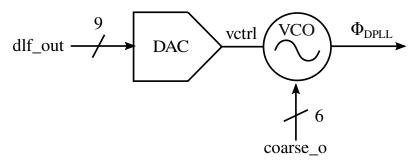

| Figura 33 – Diagrama de blocos do DCO                                              | 55 |

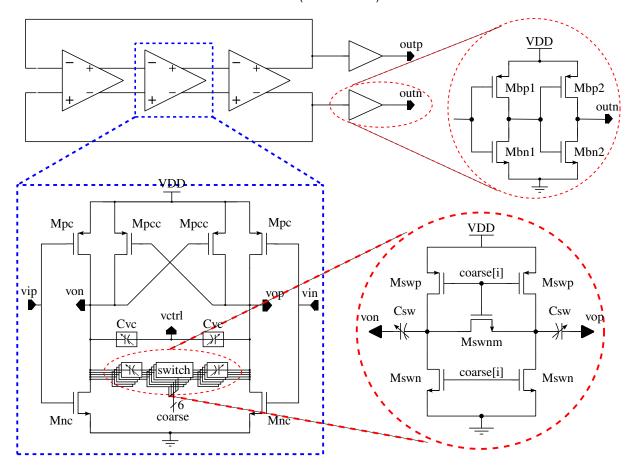

| Figura 34 – VCO à esquerda e a chave de controle grosso da frequência à direita     | 55 |

|-------------------------------------------------------------------------------------|----|

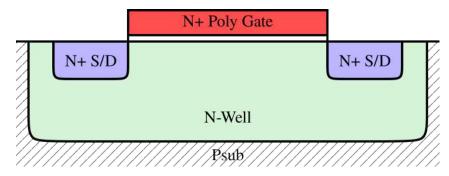

| Figura 35 – Secção transversal do varactor                                          | 56 |

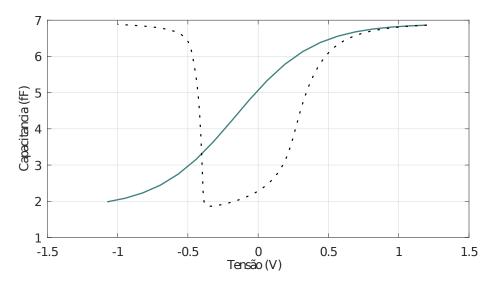

| Figura 36 – Comparação entre (linha sólida) capacitância do varactor em funçao      |    |

| da tensão entre os terminais e (linha tracejada) capacitancia de um                 |    |

| capacitor Poly (P+) sobre <i>N-Well</i>                                             | 56 |

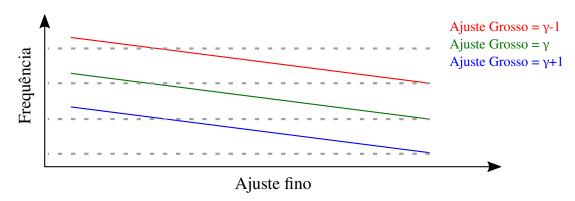

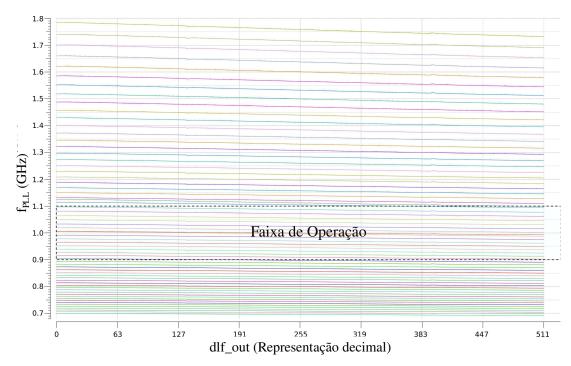

| Figura 37 – Exemplo de sobreposição de frequências para valores adjacentes do       |    |

| ajuste grosso                                                                       | 57 |

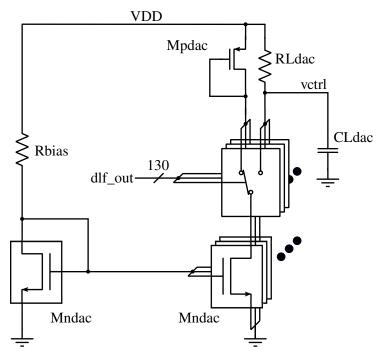

| Figura 38 – Conversor D/A                                                           | 58 |

| Figura 39 – Possível comportamento de um conversor D/A com a presença de            |    |

| descasamento                                                                        | 59 |

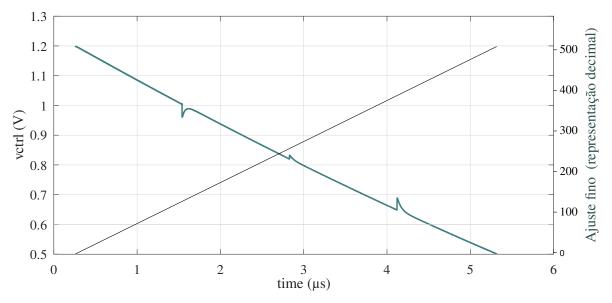

| Figura 40 – vctrl versus ajuste fino no domínio do tempo                            | 60 |

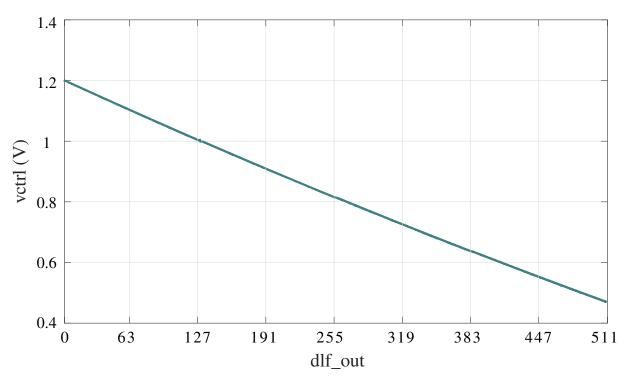

| Figura 41 – vctrl versus ajuste fino                                                | 61 |

| Figura 42 – Frequência do DPLL versus ajuste fino para diferentes códigos de        |    |

| ajuste grosso                                                                       | 62 |

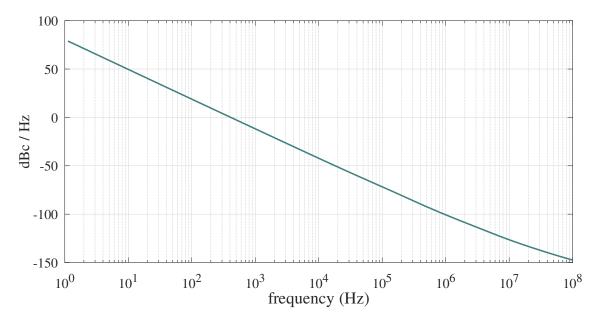

| Figura 43 – Ruído de fase do DCO ( dBc / Hz ) operando em 1 GHz                     | 63 |

| Figura 44 – Divisor de frequência 14/15/16/17                                       | 63 |

| Figura 45 – Resposta do filtro digital                                              | 65 |

| Figura 46 – Diagrama de blocos de PLL digital para análise de malha                 | 65 |

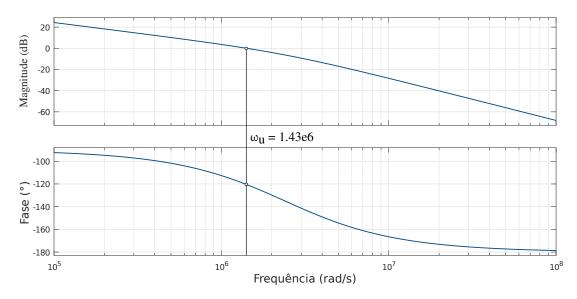

| Figura 47 – Diagrama de Bode projetado do DPLL tipo I                               | 67 |

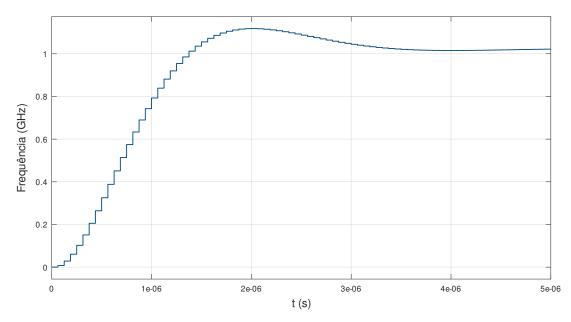

| Figura 48 – Resposta ao degrau do DPLL tipo I projetado                             | 68 |

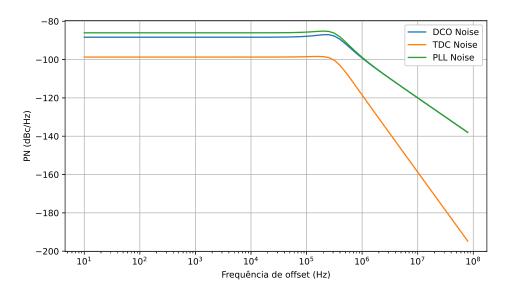

| Figura 49 – Estimativa do ruído do DPLL projetado                                   | 69 |

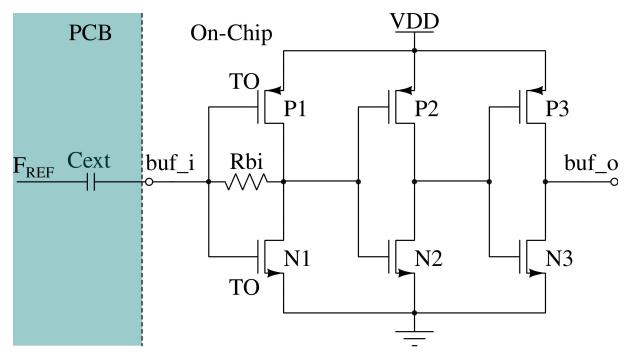

| Figura 50 – Buffer de entrada do sinal de referência                                | 70 |

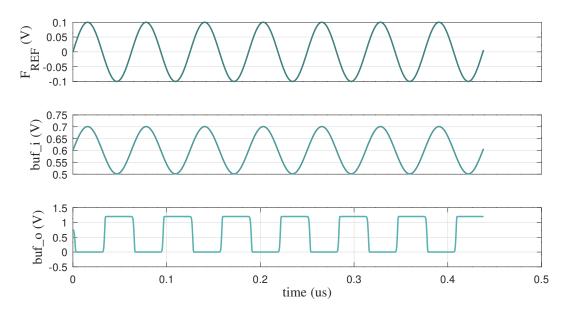

| Figura 51 – Sinais do <i>buffer</i> de entrada para o sinal de referência de 16 MHz | 71 |

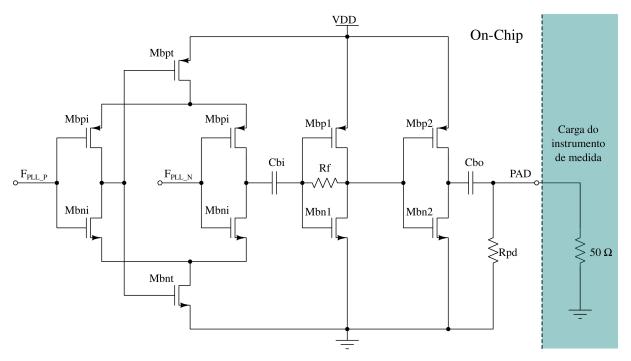

| Figura 52 – Buffer de saída do PLL                                                  | 72 |

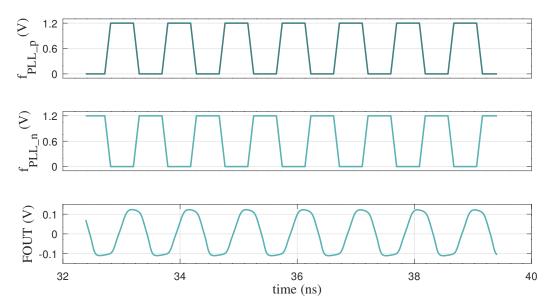

| Figura 53 – Sinais do <i>buffer</i> de saída do chip                                | 73 |

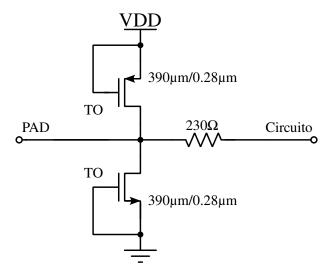

| Figura 54 – Proteção ESD primária                                                   | 74 |

| Figura 55 – Buffer analógico para medição da tensão de controle                     | 74 |

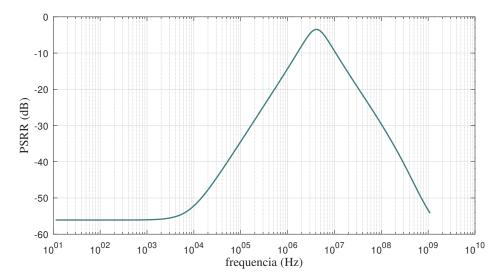

| Figura 56 – Simulação de PSRR do <i>buffer</i> analógico                            | 75 |

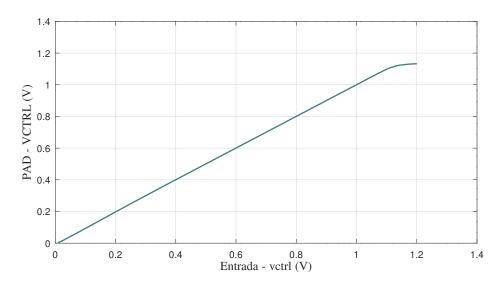

| Figura 57 – Função de transferência DC do <i>buffer</i> analógico                   | 75 |

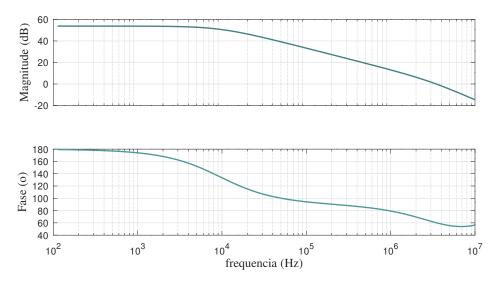

| Figura 58 – Diagrama de Bode do <i>buffer</i> analógico                             | 76 |

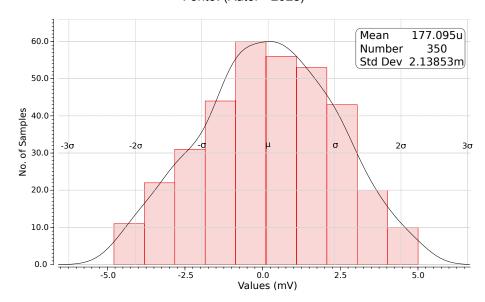

| Figura 59 – Histograma da tensão de <i>offset</i> - MC 350 amostras                 | 76 |

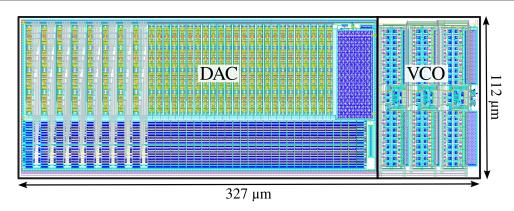

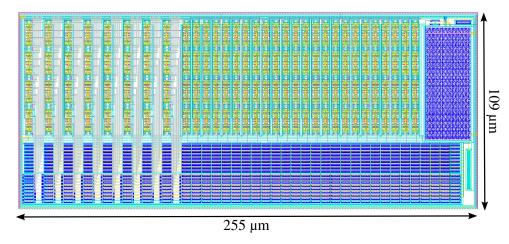

| Figura 60 – Leiaute do oscilador controlado digitalmente                            | 77 |

| Figura 61 – Leiaute do DAC                                                          | 78 |

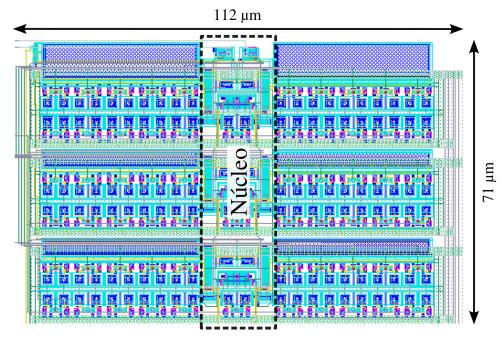

| Figura 62 – Leiaute do oscilador controlado por tensão                              | 78 |

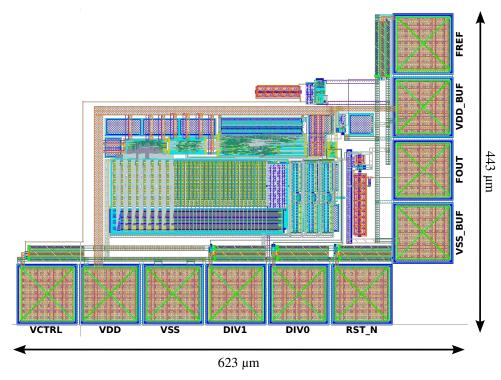

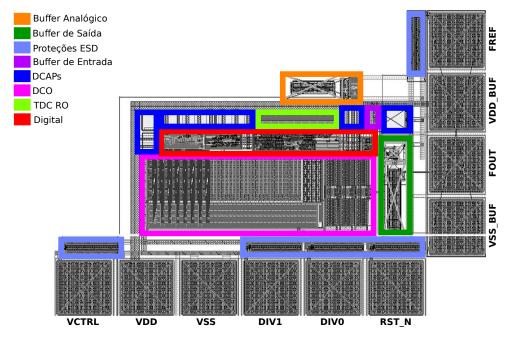

| Figura 63 – Leiaute do DPLL                                                         | 79 |

| Figura 64 – Leiaute do DPLL com divisões dos blocos                                 | 80 |

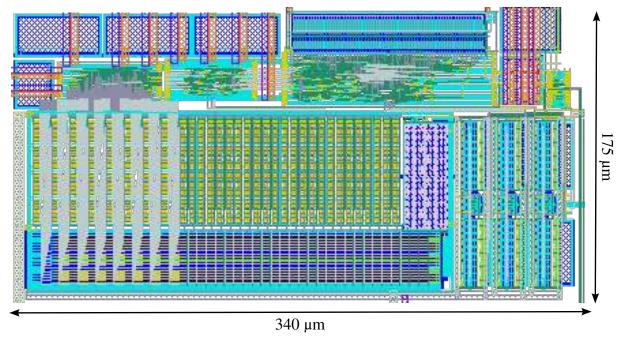

| Figura 65 – Leiaute do DPLL sem estruturas de depuração, PADs e <i>buffers</i>      | 80 |

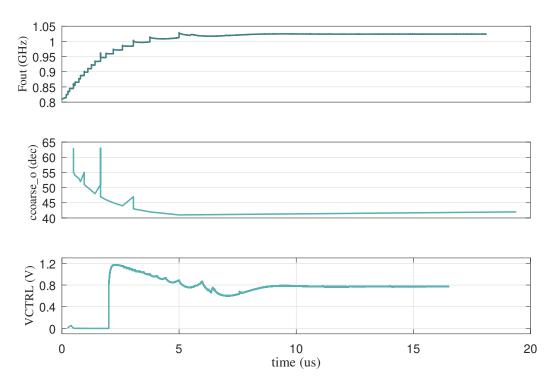

| Figura 66 - Comportamento da frequência da saída e tensão de controle na            |    |

| inicialização do DPLL                                                               | 82 |

| Figura 67 – Comportamento da frequência de saída e sinal de controle para uma |    |  |  |

|-------------------------------------------------------------------------------|----|--|--|

| mudança no valor do divisor multi módulo de 16 para 14                        | 83 |  |  |

| Figura 68 – Circuito melhorado para o DAC                                     | 88 |  |  |

| Figura 69 – Imagem da placa de circuito impresso usada nas medições           | 94 |  |  |

#### Lista de tabelas

| Tabela 1 – Comparação com Estado da Arte                                            | 23 |

|-------------------------------------------------------------------------------------|----|

| Tabela 2 - Contribuição dos ruídos dos blocos no ruído de fase para PLL tipo I      | 28 |

| Tabela 3 - Contribuição dos ruídos dos blocos no ruído de fase para PLL tipo II     | 33 |

| Tabela 4 - Exemplo de funcionamento do decodificador de estados com número          |    |

| de bits reduzidos                                                                   | 51 |

| Tabela 5 - Tamanho e valor dos componentes utilizados no DCO                        | 59 |

| Tabela 6 - Tabela verdade para o projeto do circuito combinacional                  | 63 |

| Tabela 7 - Tamanho e valor dos componentes utilizados no <i>buffer</i> de entrada . | 71 |

| Tabela 8 - Tamanho e valor dos componentes utilizados no <i>buffer</i> de saída     | 73 |

| Tabela 9 - Tamanho e valor dos componentes utilizados no buffer analógico .         | 77 |

| Tabela 10 – Contribuição aproximada dos blocos na área do DPLL                      | 81 |

| Tabela 11 – Comparação com Estado da Arte                                           | 84 |

#### Lista de abreviaturas e siglas

AMS Analog and Mixed-Signal

BBPFD Bang-Bang Phase and Frequency Detector

BEC Bubble Error Correction

CFTL Continuous Frequency Tracking Loop

CMOS Complementary Metal Oxide Semiconductor

CP Charge Pump

DAC Digital to Analog Converter

DC Direct Current

DCDL Digital Controlled Delay Line

DCO Digitally Controlled Oscillator

DECAP Decoupling Capacitor

DLF Digital Loop Filter

DPLL Digital Phase Locked Loop

DTC Digital to Time Converter

DZF Dead-Zone Free

EMI Electromagnetic interference

ESD Electrostatic Discharge

FPC Feed-forward Phase-error Cancellation

FPEC Fast Phase Error Correction

GND Ground

IIR Infinite Impulse Response

IJC Injection Controller

IoT Internet of Things

LF Loop Filter

LO Local Oscillator

LSB Least Significant Bit

MOS Metal Oxide Semiconductor

OTTDC Optimized Threshold Time to Digital Converter

PA Power Amplifier

PCB Printed Circuit Board

PD Phase Detector

PFD Phase and Frequency Detector

PLL Phase Locked Loop

PM Phase Margin

PN Phase Noise

PVT Process, Voltage and Temperature

RFID Radio Frequency Identification

RO Ring Oscillator

TDC Time to Digital Converter

VCO Voltage Controlled Oscillator

WPT Wireless Power Transfer

ZOH Zero Order Hold

#### Lista de símbolos

$f_0$  Frequência fundamental do transmissor WPT

$\Phi_{REF}$  Fase do sinal de referência

$\Phi_{DIV}$  Fase do sinal de realimentação

$\Delta \Phi$  Diferença entre as fases de realimentação e referência

vctrl Tensão analógica de controle do VCO

$\Phi_{PII}$  Fase do sinal de saída do PLL

N Valor do módulo de divisão de frequência

T<sub>DIV F</sub> Período do pulso em estado estacionário do sinal de realimentação

*T<sub>RFF</sub>* Período do sinal de referência

$K_{PD}$  Constante de ganho proporcional do detector de fase

$K_{VCO}$  Constante de ganho do VCO

A<sub>Cl</sub> Função de transferência em malha fechada

*t<sub>s</sub>* Tempo de acomodação

S<sub>N.PLL</sub> Densidade espectral de ruído do PLL

*S<sub>N.REF</sub>* Densidade espectral de ruído da referência

$S_{N,DIV}$  Densidade espectral de ruído do divisor de frequência

$S_{N,PD}$  Densidade espectral de ruído do detector de fase

*S<sub>N,VCO</sub>* Densidade espectral de ruído do oscilador controlado por tensão

$S_N$  Densidade espectral de ruído

$\omega_{comp}$  Frequência angular dos polos complexos  $I_{CP}$  Corrente de carga e descarga do CP

Up Sinal proveniente do PFD para uma diferença positiva de faseDown Sinal proveniente do PFD para uma diferença negativa de fase

$S_{N,CP}$  Densidade espectral de ruído da bomba de carga  $K_{CP}$  Constante de ganho proporcional da bomba de carga  $N_{DIV}$  Número de bits do barramento do controle de frequência

$N_{TDC}$  Número de bits do barramento da saída do TDC  $N_{DLF}$  Número de bits do barramento da saída do DLF

VP Tensão de saída do VCO positivaVN Tensão de saída do VCO negativa

I<sub>VDD</sub> Corrente da alimentaçãoVDD Tensão de alimentação

f<sub>ro</sub> Frequência de oscilação de um oscilador em anel

au Tempo de propagação da célula de atraso

CLdac Capacitância total na saída do DAC

$\omega_{pdac}$  Frequência angular do polo na saída do DAC

Cpar Capacitância parasita total entre o nó vctrl e terra AC  $\omega_u$  Frequência angular de ganho unitário em malha aberta

$K_{DLF}$  Constante de ganho proporcional do DLF  $K_{LF}$  Constante de ganho proporcional do LF

*Err*[*k*] Valor discreto do erro da fase

ctr/[k] Valor discreto do controle da frequência C(z) Valor discreto do controle da frequência

T Período de amostragem do TDC  $\omega_{REF}$  Frequência angular de referência  $\zeta$  Fator de amortecimento da malha

$\omega_Z$  Frequência angular do zero  $K_{TDC}$  Constante de ganho do TDC

$\omega_n$  Frequência angular natural da malha

$\omega_{\it bw}$  Frequência angular da largura de banda do DPLL

$S_{vctrl}$  Ruído de quantização na tensão de controle  $K_{DAC}$  Variação de 1 LSB na tensão de controle

$P_{REFspurs}$  Potência dos *spurs* da referência  $K_{DCO}$  Constante de ganho do DCO  $R_f$  Resistor de realimentação

C<sub>bi</sub> Capacitor de desacoplamento DC de entradaC<sub>bo</sub> Capacitor de desacoplamento DC de saída

R<sub>pd</sub> Resistor de *pull-down*

*R*<sub>ab</sub> Resistor para polarização de corrente

C<sub>C</sub> Capacitor de compensação

R<sub>C</sub> Resistor para anular RHP zero

PSRR Power Supply Rejection Ratio

#### Sumário

| 1         | INTRODUÇÃO                                             | 18 |

|-----------|--------------------------------------------------------|----|

| 1.1       | MOTIVAÇÃO                                              | 18 |

| 1.2       | ESTADO DA ARTE                                         | 23 |

| 1.3       | OBJETIVOS                                              | 24 |

| 1.4       | ORGANIZAÇÃO DO DOCUMENTO                               | 24 |

| 2         | FUNDAMENTAÇÃO TEÓRICA                                  | 25 |

| 2.1       | MALHA DE CONTROLE DE FASE (PHASE LOCKED LOOP)          | 25 |

| 2.1.1     | Classificação de PLLs                                  | 25 |

| 2.1.1.1   | PLL Tipo I                                             | 25 |

| 2.1.1.1.1 | Ruído em PLL Tipo I                                    | 27 |

| 2.1.1.2   | PLL Tipo II                                            | 29 |

| 2.1.1.2.1 | Ruído em PLL Tipo II                                   | 31 |

| 2.1.1.3   | PLL N-Inteiro                                          | 32 |

| 2.1.1.4   | PLL N Fracionário                                      | 33 |

| 2.2       | PLLS COM COMPENSAÇÃO DIGITAL (DPLLS)                   | 34 |

| 2.2.1     | Elementos básicos                                      | 34 |

| 2.2.2     | Vantagens e Desvantagens Comparado ao PLL Convencional | 35 |

| 2.3       | TOPOLOGIAS DOS BLOCOS                                  | 36 |

| 2.3.1     | Oscilador Controlado Digitalmente                      | 36 |

| 2.3.2     | Filtro de Malha Digital                                | 38 |

| 2.3.3     | Conversor de tempo para digital                        | 38 |

| 2.3.3.1   | Detector de Fase Bang-Bang                             | 39 |

| 2.3.3.2   | Conversor de Tempo Para Digital Convencional           | 40 |

| 2.3.3.3   | Arquitetura Vernier                                    | 40 |

| 2.3.3.4   | Ring Oscillator TDC (RO-TDC)                           | 41 |

| 2.3.4     | Divisor de Frequência                                  | 42 |

| 3         | PROJETO DO PLL DIGITAL                                 | 44 |

| 3.1       | MALHA DE CONTROLE DE FASE COM COMPENSAÇÃO DIGITAL      |    |

|           | (DPLL)                                                 | 44 |

| 3.2       | CONVERSOR DE TEMPO PARA DIGITAL (TDC)                  | 45 |

| 3.2.1     | Função de Transferência                                | 53 |

| 3.2.2     | Formas de onda                                         | 53 |

| 3.3       | OSCILADOR CONTROLADO DIGITALMENTE (DCO)                | 54 |

| 3.3.1     | VCO                                                    | 54 |

| 3.3.2     | DAC                                                    | 57 |

| 3.3.3     | Função de Transferência                                | 60 |

| 3.3.4     | Formas de Onda                                         | 60 |

| 3.4    | DIVISOR DE FREQUÊNCIA                             | 62 |

|--------|---------------------------------------------------|----|

| 3.5    | FILTRO DIGITAL DA MALHA (DLF)                     | 64 |

| 3.5.1  | Formas de onda                                    | 64 |

| 3.6    | PROJETO DE MALHA DO DPLL                          | 64 |

| 3.6.1  | Projeto de malha para DPLL Tipo I                 | 66 |

| 3.6.2  | Projeto de malha para DPLL Tipo II                | 68 |

| 3.7    | BUFFER DE ENTRADA                                 | 70 |

| 3.7.1  | Formas de Onda                                    | 71 |

| 3.8    | BUFFER DE SAÍDA                                   | 71 |

| 3.8.1  | Formas de Onda                                    | 72 |

| 3.9    | PROTEÇÃO PRIMÁRIA                                 | 72 |

| 3.10   | CIRCUITO PARA MONITORAR A TENSÃO DE CONTROLE      | 73 |

| 3.11   | LEIAUTE                                           | 76 |

| 3.11.1 | Blocos internos                                   | 76 |

| 3.11.2 | DPLL                                              | 78 |

| 3.11.3 | DPLL Com Marcações Diferenciando Blocos           | 79 |

| 3.11.4 | Núcleo do DPLL                                    | 79 |

| 4      | RESULTADOS                                        | 82 |

| 4.1    | SIMULAÇÕES                                        | 82 |

| 4.1.1  | <b>DPLL</b>                                       | 82 |

| 4.1.2  | Resumo Dos Resultados                             | 84 |

| 5      | CONCLUSÃO E RECOMENDAÇÕES                         | 85 |

| 5.1    | CONCLUSÃO                                         | 85 |

| 5.2    | RECOMENDAÇÕES                                     | 86 |

|        | REFERÊNCIAS                                       | 89 |

|        | APÊNDICE A – RELAÇÃO ENTRE MARGEM DE FASE E FATOR |    |

|        | DE AMORTECIMENTO PARA PLL TIPO I DE SE-           |    |

|        | GUNDA ORDEM                                       | 92 |

|        | APÊNDICE B – RELAÇÃO ENTRE BANDA DA MALHA E FATOR |    |

|        | DE AMORTECIMENTO                                  | 93 |

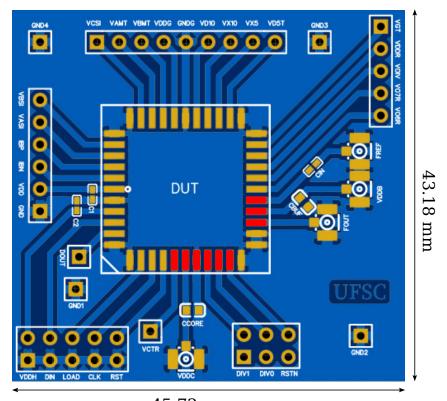

|        | APÊNDICE C – PLACA DE CIRCUITO IMPRESSO           | 94 |

|        | ANEXO A – CÓDIGO VERILOG PARA EMULAR O COMPORTA-  |    |

|        | MENTO DO OSCILADOR NA SIMULAÇÃO DO TDC .          | 95 |

|        | ANEXO B – SCRIPT OCTAVE PARA MALHA DE DPLL TIPO-I | 96 |

#### 1 Introdução

#### 1.1 Motivação

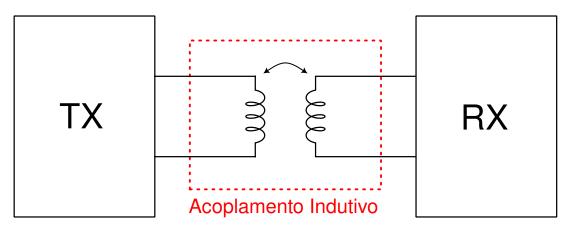

Com o avanço da tecnologia, é evidente o crescimento no desenvolvimento de dispositivos da denominada "Internet das Coisas" (*Internet of Things* - IoT) (DING *et al.*, 2020). Um dos desafios enfrentados por esses dispositivos é a alimentação dos circuitos, devido à necessidade de autonomia energética. Dentre as diversas soluções existentes para esse problema, destaca-se a transferência de energia sem fio (*Wireless Power Transfer* - WPT). Um sistema WPT consiste em um dispositivo transmissor, um receptor e um acoplamento, conforme ilustrado na Figura 1. O funcionamento básico de um sistema WPT ocorre da seguinte forma: o transmissor possui uma fonte própria de energia elétrica, a partir da qual é gerado um sinal variante no tempo que é injetado no lado primário do acoplamento. Esse sinal oscilatório gera um campo magnético no indutor primário, induzindo, por sua vez, uma tensão elétrica no indutor secundário. No lado secundário, o receptor pode retificar e utilizar a energia recebida.

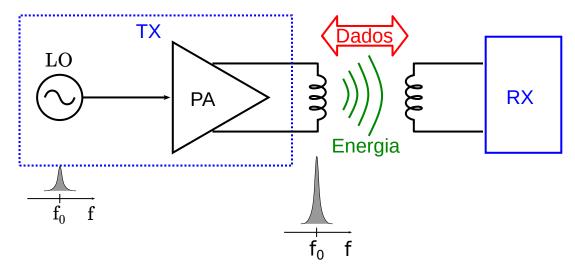

A eficiência na transferência de energia depende principalmente da frequência do sinal utilizado e das características geométricas dos indutores. Especificamente, há uma frequência ótima na qual o fator de qualidade dos indutores é maximizado. Essa frequência ( $f_0$  na Figura 2) deve ser gerada pelo bloco denominado Oscilador Local (Local Oscillator - LO) no transmissor. O sinal do LO é fortalecido pelo amplificador de potência (Power Amplifier - PA), o qual gera a amplitude necessária para alimentar o indutor primário. O mesmo canal de comunicação usado para transferir energia pode, eventualmente, ser utilizado para comunicação de dados de forma bidirecional (do primário para o secundário e vice-versa). A modulação de dados no transmissor geralmente é aplicada no PA (modulação em amplitude). Por outro lado, as informações recebidas de volta podem ser encontradas na envoltória do sinal nos terminais do indutor. Isso ocorre porque o lado secundário realiza a modulação de carga para se

Figura 1 – Exemplo básico de transferência de energia sem fio Fonte: (Autor - 2023)

Figura 2 – Sistema WPT com detalhes do transmissor Fonte: (Autor - 2023)

comunicar com o lado primário do acoplamento. Portanto, a recuperação dos dados no transmissor é realizada utilizando um bloco detector de envoltória.

A partir da descrição fornecida no parágrafo anterior, é possível inferir a importância do bloco LO, uma vez que sua função é gerar uma frequência estável e de boa pureza espectral, especificada em termos de ruído de fase e componentes indesejados de frequência fixa (*spurs*).

O sistema WPT é inerentemente relacionado com a energização de *tags* de Identificação por Radiofrequência (*Radio Frequency Identification* - RFID) (ROSELLI *et al.*, 2013). Embora a maioria dessas aplicações opere na frequência de 13,56 MHz, têm sido demonstradas aplicações em frequências consideravelmente mais altas, visando uma maior eficiência energética. Por exemplo, em (CABRERA; RANGEL DE SOUSA, 2014) foi demonstrado um sistema WPT com eficiência ótima alcançada em uma frequência de aproximadamente 1 GHz.

Para frequências de algumas dezenas de MHz, é possível implementar o LO com osciladores a cristal, os quais fornecem frequências altamente precisas (com variações na ordem de ppm - partes por milhão) e excelente qualidade espectral. Já para frequências na faixa de centenas de MHz e superiores, é possível implementar osciladores em circuito integrado, por exemplo osciladores em anel ou osciladores LC. No entanto, as frequências desses osciladores integrados podem variar em dezenas de pontos percentuais e exibem ruído de fase consideravelmente alto. Com o objetivo de combinar as vantagens da alta frequência nos osciladores integrados com a alta precisão dos osciladores de cristal, é necessário projetar uma Malha de Controle de Fase (*Phase Locked Loop* - PLL).

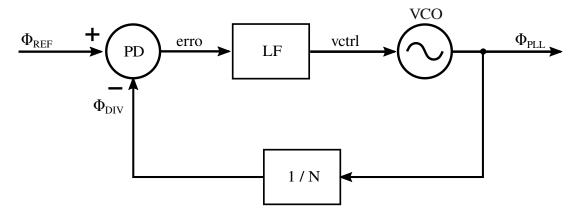

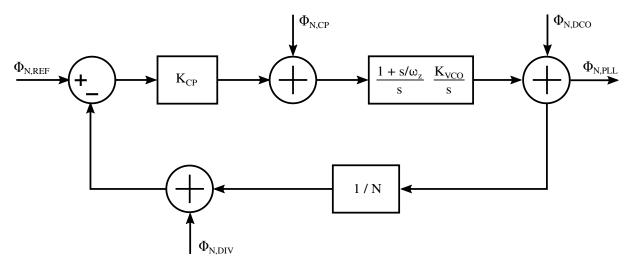

Um PLL convencional possui a arquitetura mostrada na Figura 3. Ele é composto pelos blocos: Detector de Fase (*Phase Detector -* PD), Filtro de Malha (*Loop Filter -* LF), Oscilador Controlado por Tensão (*Voltage Controlled Oscillator -* VCO) e Divisor

Figura 3 – Diagrama de blocos de um PLL convencional Fonte: (Autor - 2023)

de Frequência.

O PLL pode ser estudado como um sistema de controle, onde a variável controlada é a fase de saída. Quando o PLL opera em estado estacionário, o sinal de erro depende do bloco de compensação (filtro) usado. A escolha do tipo de filtro pode levar uma diferença entre fases igual a zero. Em outros casos, a diferença entre fases é inversamente proporcional ao ganho de malha. Em PLLs como na Figura 3, a tensão na saída do LF (vctrl) é proporcional a essa diferença entre as fases. Essa tensão atua na frequência de saída do PLL através do VCO. Se o PLL for projetado corretamente, tomando os cuidados para sempre levar o circuito até a frequência desejada (condição de lock), então a frequência em  $\Phi_{DIV}$  é a mesma frequência que em  $\Phi_{REF}$ , sendo assim, a frequência em  $\Phi_{PLL}$  é N vezes maior que a frequência em  $\Phi_{REF}$ .

O funcionamento de cada um dos blocos, mostrado na Figura 3, é explicado como segue.

#### 1. Detector de Fase

Há diferentes formas de implementar o detector de fase (porta XOR, *flip-flop*, multiplicador analógico). Cada uma delas é caracterizada por uma função de transferência específica, mas em todos os casos a informação da diferença entre as fases ( $\Phi_{REF}$  e  $\Phi_{DIV}$ ) está em baixas frequências. No entanto, há também componentes residuais em frequências mais altas, as quais devem ser atenuadas pelo filtro de malha.

Uma abordagem mais completa pode ser realizada com um Detector de Fase e Frequência (*Phase and Frequency Detector* - PFD) que, além de detectar a diferença de fases, é capaz de discriminar a diferença entre as frequências. Esse bloco é utilizado em conjunto com a bomba de carga, que injeta ou extrai carga do filtro com base na diferença de fases ( $\Delta \Phi$ ). Existem circuitos que ampliam a faixa de operação do PFD, como mencionado em (CABRERA; ROA; NOIJE, 2008), evitando assim efeitos indesejáveis, como o *Cycle Slipping*.

#### 2. Filtro de Malha

O filtro passa-baixa atenua as componentes de alta frequência geradas pelo PD e define as características estáticas (ruído de fase e *spurs*) e dinâmicas (tempo de acomodação) da malha. Tais características dependem da localização dos polos e zeros, influenciando a estabilidade do sistema.

Para o projeto do filtro junto com o circuito PD, ou PFD+Bomba de Carga (*Charge Pump* - CP), é necessário considerar também a magnitude das interferências geradas na tensão de controle, pois essas interferências aparecem no espectro de saída do PLL como *spurs*.

Em PLLs convencionais, o filtro é implementado com dispositivos passivos (resistores e capacitores). Geralmente esses componentes causam um grande impacto na área utilizada em Silício, para gerar polos/zero no sistema em determinadas frequências. Uma técnica para reduzir a área do LF é fazer a compensação da malha no domínio digital como mostrado nessa dissertação. Algumas vantagens de usar compensação digital são maior grau de liberdade para a geração de polos e zeros no sistema; Polos/zeros podem ser adicionados sem a necessidade de grandes capacitores; Tornar o projeto mais rápido com a capacidade de portar um projeto de uma tecnologia para outra, principalmente em tecnologias mais avançadas.

#### 3. Oscilador Controlado por Tensão

O VCO é encarregado de gerar o sinal de saída do PLL, sendo que a frequência em sua saída é diretamente proporcional à tensão de controle em sua entrada (*vctrl*). Geralmente, em circuitos integrados, ele é implementado com osciladores em anel ou osciladores LC. Os osciladores LC são os maiores responsáveis pelo impacto na área em silício, pois estes usam grandes indutores integrados dentro do chip. No entanto, muitas vezes eles são preferidos por apresentar melhor compromisso entre potência e ruído de fase comparado aos osciladores em anel.

Ao projetar a faixa de operação do VCO é importante considerar variações de processo, tensão e temperatura (*Process, Voltage and Temperature* - PVT) desse circuito, a fim de garantir que a frequência de oscilação seja atingida para todas as condições de operação.

#### 4. Divisor de Frequência

A malha assegura que, em estado estacionário, a frequência do sinal de realimentação ( $\Phi_{DIV}$ ) seja igual à frequência no sinal de referência ( $\Phi_{REF}$ ). Portanto, a divisão de frequência no ramo da realimentação ( $\Phi_{DIV} = \Phi_{PLL} / N$ ) resulta em uma frequência de saída N vezes maior que a frequência de referência.

Divisores de frequência são normalmente implementados por meio de circuitos digitais sequenciais, o qual também simplifica o controle do módulo de divisão usando uma palavra digital.

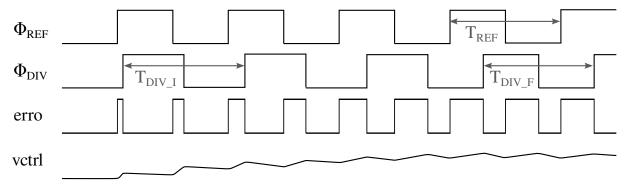

A Figura 4 mostra um exemplo do comportamento de um PLL com o intuito de explicar o funcionamento da malha. Neste exemplo, o circuito PD utilizado é uma porta XOR, sendo sua saída nível lógico '1' sempre que houver uma diferença entre o nível lógico de suas entradas e '0' caso contrário. É assumido um filtro RC de primeira ordem.

Inicialmente, a frequência em  $\Phi_{DIV}$  é menor do que a frequência em  $\Phi_{REF}$ . A diferença entre as fases, evidente na figura, causa aumento na largura dos pulsos no sinal de erro, o que por sua vez aumenta a tensão de controle *vctrl*. Ao aumentar a tensão de controle também aumenta a frequência de saída do PLL e, consequentemente a frequência em  $\Phi_{DIV}$ . Dessa forma, no estado estacionário  $T_{DIV}$   $_F$  é igual à  $T_{REF}$ .

O funcionamento em PLLs digitais é similar ao explicado acima. A diferença é que os blocos, PD, LF e VCO são substituídos pelos blocos Conversor de Tempo para Digital (Time to Digital Converter - TDC), Filtro de Malha Digital (Digital Loop Filter - DLF) e Oscilador Controlado Digitalmente (Digitally Controlled Oscillator - DCO), respectivamente. Em (STASZEWSKI *et al.*, 2004) é detalhada a viabilidade de usar um PLL digital em tecnologias mais recentes (*deep-submicron* CMOS), uma vez que a resolução no domínio do tempo melhora em detrimento da resolução no domínio da tensão, causado pela diminuição na tensão de alimentação.

O estado da arte mostra que há uma tendência para o uso de circuitos PLL com compensação digital (chamados nesse documento de DPLL). Técnicas como em (HO; CHEN, M. S.-W., 2019) são utilizadas para aumentar o desempenho dos DPLLs.

Neste contexto, o projeto proposto é de um DPLL na frequência de 1 GHz em tecnologia CMOS 65 nm, para ser usado em transferência de energia sem fio.

Figura 4 – Exemplo de um PLL tipo I entrando na condição de *lock* Fonte: (Autor - 2023)

#### 1.2 Estado da Arte

É apresentado nesta seção o estado da arte dos DPLLs. A tabela 1 mostra alguns trabalhos recentemente publicados sendo todos de DPLLs com nó tecnológico entre 40 nm e 65 nm.

|                          | (UN <i>et al.</i> ,<br>2019) | (SEONG <i>et al.</i> ,<br>2019) | (KANG; LIU,<br>2022) | (REHMAN<br>et al., 2021) |

|--------------------------|------------------------------|---------------------------------|----------------------|--------------------------|

| Ano                      | 2019                         | 2019                            | 2022                 | 2021                     |

| Nó Tecnológico           | 65 nm                        | 65 nm                           | 40 nm                | 55 nm                    |

| Topologia                | Bang-Bang<br>DPLL            | FPEC DPLL                       | FPC PLL              | CFTL PLL                 |

| Tipo do VCO/DCO          | Anel                         | Anel                            | Anel                 | LC                       |

| F <sub>ref</sub> (MHz)   | 50                           | 75                              | 50                   | 32                       |

| F <sub>out</sub> (GHz)   | 1,3-2,65                     | 2,4 (2,3-2,55)                  | 1,6                  | 2,402-2,48               |

| PN@1MHz (dBc / Hz)       | -90 <sup>(1)</sup>           | -119,8                          | -118,25              | -110,78                  |

| Tempo de acomodação (µs) | 8 <sup>(2)</sup>             | < 1500 <sup>(3)</sup>           | -                    | 38 <sup>(1)</sup>        |

| Alimentação (V)          | 1                            | 1,2                             | 1,1                  | 0,5 para o DCO           |

| Potência dissipada (mW)  | 2,4@2,4 GHz                  | 6                               | 5                    | 0,46                     |

| Área ( <i>mm</i> ²)      | 0,12                         | 0,055 <sup>(4)</sup>            | 0,05 <sup>(4)</sup>  | 0,129                    |

Tabela 1 – Comparação com Estado da Arte

Em (UN *et al.*, 2019) é proposto um DPLL com a implementação de um detector de fase *Bang-Bang* (essa topologia é melhor explicada no Capítulo 2). Para conseguir um rápido tempo de acomodação duas técnicas são propostas, (i) Um esquema de calibração do ganho do Conversor Digital para Tempo (*Digital to Time Converter - DTC*) livre do efeito de descasamento; (ii) Duas malhas separadas para o ajuste grosso e ajuste fino. Um oscilador gera a frequência de saída. O projeto apresenta o menor tempo de estabilização entre os projetos comparados (8 µs para um erro inicial de 82 MHz), e possui uma área de 0,12 *mm*<sup>2</sup>.

O segundo projeto em comparação é (SEONG *et al.*, 2019). O autor propõe um DPLL com oscilador em anel. Para diminuir a desvantagem desta topologia de oscilador (ruído de fase) é usado um circuito de Correção Rápida do Erro de Fase (*Fast Phase-Error Correction* - FPEC) que faz uma rápida correção de fase atuando diretamente no DCO. Além disso, para minimizar o erro de quantização utiliza um TDC com Limiar Otimizado (*Optimized Threshold Time-to-Digital Converter* - OTTDC), em que os atrasos do DTCs são calibrados. Possui um alto valor para frequência de referência, o que pode dificultar a utilização de um oscilador a cristal.

O trabalho em (KANG; LIU, 2022) propõe um PLL com oscilador em anel com *Feed-forward Phase-error Cancellation* (FPC) para melhorar o ruído de fase de osciladores em anel. O autor descreve que usando essa técnica o erro de fase pode ser

<sup>&</sup>lt;sup>1</sup> Estimado a partir de dados apresentados.

<sup>&</sup>lt;sup>2</sup> Tempo de acomodação para um erro inicial de 82 MHz.

<sup>&</sup>lt;sup>3</sup> Tempo de acomodação considerando a calibração dos parâmetros do circuito.

<sup>&</sup>lt;sup>4</sup> Considerando área ativa.

rapidamente compensado pelo *Digital Controlled Delay Line* (DCDL). Também propõe um *Dead-Zone Free Bang-Bang Phase and Frequency Detector* (DZF BBPFD) eliminando a histerese do BBPFD, causada por tempos de *setup* e *hold*, e melhorando a resolução deste (consequentemente melhor ruído de fase em banda).

Em (REHMAN *et al.*, 2021) é proposto um DPLL que foca em baixo consumo e baixo custo em aplicações IoT. Consiste em utilizar uma malha de *track* contínuo (CFTL) para ajustar a frequência de saída próximo ao valor desejado, após o *track*, é habilitado um bloco de controle de injeção IJC para ajustar a fase do DCO. Uma baixa tensão de alimentação é usada para o oscilador LC para baixo consumo de potência. Valor de tempo de acomodação extraído dos resultados apresentados é de 38 µs.

#### 1.3 Objetivos

- Projetar um DPLL operando em 1 GHz buscando um melhor compromisso entre área, ruído de fase, spurs, tempo de estabilização e consumo de potência.

- Fazer o leiaute do DPLL em ambos os domínios analógico e digital.

- Preparar o circuito para ser enviado à fabricação na tecnologia CMOS 65 nm.

- Verificar o desempenho do circuito através de simulação.

#### 1.4 Organização do Documento

No Capítulo 1 é apresentada a motivação para o uso de PLLs, destacando sua funcionalidade básica e a tendência em adotar a compensação digital. Além disso, é feita uma revisão do estado da arte dos DPLLs e são estabelecidos os objetivos deste trabalho.

No Capítulo 2 é discutida a fundamentação teórica, abordando diferentes tipos de PLLs, com ênfase nos DPLLs, e apresentando algumas topologias comumente utilizadas.

O projeto do DPLL e de seus blocos constituintes, detalhando as etapas de projeto e os parâmetros considerados, é apresentado no Capítulo 3.

No Capítulo 4 são apresentados os resultados obtidos a partir da implementação do DPLL, destacando métricas relevantes.

Por fim, no Capítulo 5, são apresentadas as conclusões e recomendações derivadas deste estudo, enfatizando os principais resultados alcançados, as contribuições do trabalho e possíveis direções futuras para a pesquisa na área.

#### 2 Fundamentação Teórica

#### 2.1 Malha de Controle de Fase (Phase Locked Loop)

Nesta seção são mostrados alguns detalhes de implementação dos PLLs. É exibida a classificação dos PLLs dependendo do tipo de filtro usado e dependendo do fator de divisão. Também é feita uma análise de estabilidade da malha e de ruído para cada tipo de PLL.

#### 2.1.1 Classificação de PLLs

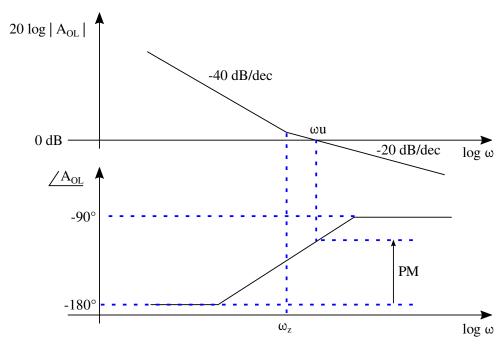

De acordo com o filtro de malha, os PLLs podem ser tipo I ou tipo II. A nomenclatura é devida à função de transferência em malha aberta, onde o PLL tipo I apresenta um polo na origem e o PLL tipo II apresenta dois polos na origem (RAZAVI, 2011).

#### 2.1.1.1 PLL Tipo I

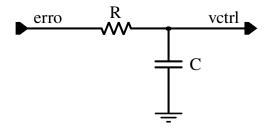

O PLL tipo I é formado pelos seguintes blocos: PD, filtro passa-baixa, VCO e divisor de frequência. Essa composição pode ser vista na Figura 3, sendo que o bloco LF é um filtro RC de primeira ordem como mostrado na Figura 5.

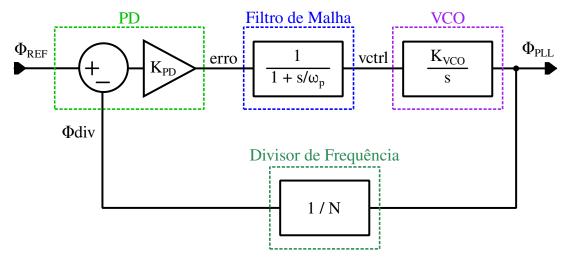

Para fazer uma análise da malha é necessário considerar o modelo exposto na Figura 6. No filtro de malha,  $\omega_p$  representa o módulo da frequência do polo sendo  $\omega_p = 1/RC$ . No Detector de Fase  $K_{PD}$  representa o ganho proporcional do bloco. Já no VCO,  $K_{VCO}$  representa o ganho de frequência por unidade na tensão de controle (rad/[s.V]).

Como a variável controlada é a fase e não a frequência, o VCO é representado por um integrador, pois um passo de tensão na entrada ocasiona um acúmulo de fase na saída, ou em outras palavras, um passo de tensão na entrada gera um passo de frequência na saída. Como resultado, a função de transferência em malha aberta  $(A_{OL})$  é mostrada a seguir.

$$A_{OL}(s) = \frac{K_{PD}K_{VCO}}{s(1 + s/\omega_D)N}$$

(1)

O diagrama de Bode é mostrado na Figura 7. Nota-se que o PLL possui dois polos, um localizado na origem e outro igual ao polo do LF.

Figura 5 – Filtro de malha em PLL tipo I Fonte: (Autor - 2023)

Figura 6 – Modelo para PLL tipo I Fonte: (Autor - 2023)

Figura 7 – Comportamento da função de transferência em malha aberta do PLL tipo I Fonte: (Autor - 2023)

Neste tipo de PLL, quanto maior for o ganho de malha menor a margem de fase (PM), pois a frequência de ganho unitário em malha aberta ( $\omega_u$ ) aumenta e a fase nessa frequência se aproxima de  $-180^\circ$ . Consequentemente, esse tipo de PLL está limitado quanto a ganho de malha elevado.

A função de transferência em malha fechada  $(A_{CL})$  é mostrada na equação abaixo.

$$A_{CL}(s) = \frac{K_{PD}K_{VCO}}{\frac{s^2}{\omega_p} + s + \frac{K_{PD}K_{VCO}}{N}}$$

(2)

A função de transferência mostrada na equação (2) pode ser escrita na seguinte

Figura 8 – Modelo de ruído do PLL tipo I Fonte: (Autor - 2023)

forma,

$$A_{CL}(s) = \frac{N\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(3)

onde  $\omega_n$  é a frequência natural e  $\zeta$  é o fator de amortecimento.

Com as equações (2) e (3) podemos chegar nas seguintes expressões para  $\omega_n$  e  $\zeta$ .

$$\omega_n = \sqrt{\frac{K_{PD}K_{VCO}\omega_p}{N}} \tag{4}$$

$$\zeta = \frac{1}{2} \sqrt{\frac{N\omega_p}{K_{PD}K_{VCO}}} \tag{5}$$

Desconsiderando efeitos não-lineares, o tempo de acomodação é inversamente proporcional a  $\zeta \omega_n$ ; sendo assim, o tempo de acomodação  $(t_s)$  é  $t_s \propto \frac{1}{\omega_p}$ .

Uma outra limitação desse tipo de PLL é com relação ao capacitor C do filtro de malha. Para diminuir os *spurs* na saída, valores altos para essa capacitância são preferidos, pois os componentes de alta frequência em vctrl são atenuados. Porém, fazendo isso, o polo  $\omega_p$ , mostrado na Figura 7, fica localizado em frequências mais baixas e, quanto menor a frequência de um polo não dominante menor é PM. Além disso, diminuir  $\omega_p$  incrementa o tempo de acomodação.

#### 2.1.1.1.1 Ruído em PLL Tipo I

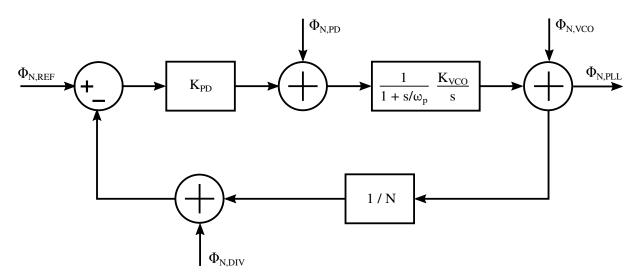

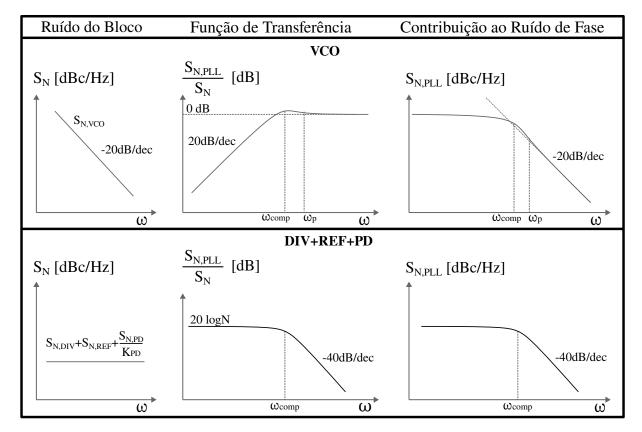

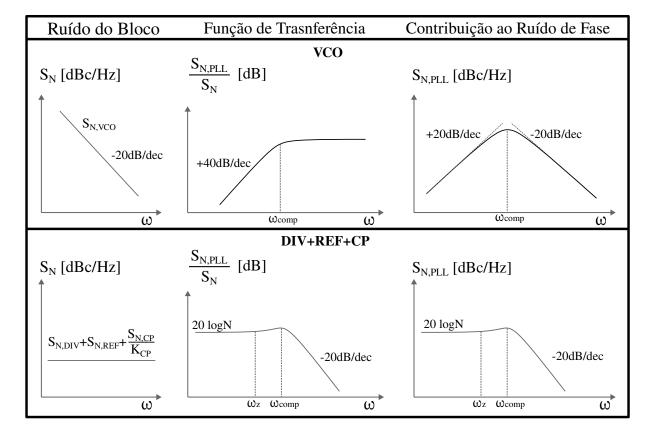

Para a análise do ruído de fase no PLL tipo I, o modelo da Figura 8 é usado. Neste modelo os principais contribuidores ao ruído são considerados. O ruído na saída do PLL é composto pela soma dos contribuidores, sendo cada um deles mostrado nas equações de (6) a (9).

$$\frac{S_{N,PLL}}{S_{N,REF}} = \left| A_{CL}(j\omega) \right|^2 \tag{6}$$

Tabela 2 – Contribuição dos ruídos dos blocos no ruído de fase para PLL tipo I

$$\frac{S_{N,PLL}}{S_{N,DIV}} = \left| A_{CL}(j\omega) \right|^2 \tag{7}$$

$$\frac{S_{N,PLL}}{S_{N,PD}} = \left| \frac{A_{CL}(j\omega)}{K_{PD}} \right|^2 \tag{8}$$

$$\frac{S_{N,PLL}}{S_{N,VCO}} = \left| 1 - \frac{A_{CL}(j\omega)}{N} \right|^2 \tag{9}$$

onde,  $S_N$  é a densidade espectral do ruído e o subscrito corresponde a sua origem. Para o caso particular  $S_{N,PLL}$  é a densidade espectral do ruído na saída do PLL.

Pode ser visto, pelas equações de (6) a (8), que o ruído do respectivo bloco é atenuado em altas frequências pela característica passa-baixa de  $A_{CL}(s)$ . Por outro lado, a equação (9), mostra que o ruído proveniente do VCO é atenuado em baixas frequências.

A Tabela 2 resume as contribuições dos blocos no ruído de fase do PLL em função da frequência de *offset*. Na primeira coluna da tabela é mostrada a densidade espectral do ruído do respectivo bloco indicado  $(S_N)$ . A coluna central mostra a função de transferência relativa ao respectivo ruído. Na terceira coluna está a densidade

Figura 9 – Diagrama de blocos de PFD+CP+LF Fonte: (Autor - 2023)

espectral do ruído gerado na saída ( $S_{N,PLL}$ ) referente ao respectivo bloco. Na imagem,  $\omega_{comp}$  representa a magnitude dos polos complexos existentes quando  $\zeta$  < 1.

Em baixas frequências da função de transferência do ruído do PLL em relação ao ruído do VCO, a magnitude tem uma inclinação de +20*dB/dec*, isso se deve ao fato de a equação (9) apresentar um zero na origem.

Para simplificação da análise, o ruído do oscilador tem uma inclinação constante de -20*dB/dec* e o ruído proveniente do divisor de frequência, referência e PD foi considerado um ruído branco.

Para uma mesma margem de fase, a relação  $\frac{\omega_{comp}}{\omega p}$  é constante, portanto, há um compromisso com relação à frequência do polo do filtro de malha. Esse compromisso é de quanto ruído é atenuado do VCO e quanto ruído é atenuado do PD+Divisor+Referência. Quanto mais crítico o ruído da combinação PD+Divisor+Referência melhor uma frequência mais baixa para  $\omega_p$ . Por outro lado, se mais crítico o ruído do VCO,  $\omega_p$  deve ser aumentado.

#### 2.1.1.2 PLL Tipo II

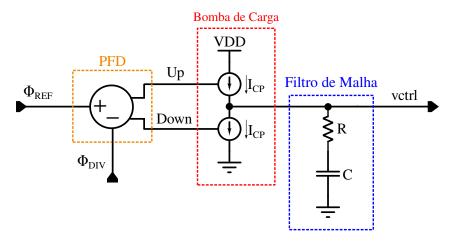

Esse tipo de PLL possui os seguintes blocos: PFD, CP, LF, VCO e divisor de frequência. As diferenças entre esse tipo de PLL e o tipo I estão nos blocos PD e LF que são substituídos pelos blocos PFD+CP e uma outra construção para o LF como pode ser visto na Figura 9.

Os blocos VCO e divisor de frequência podem ser os mesmos utilizados no PLL tipo I. O PFD gera dois sinais chamados up e down que carregam e descarregam o nó vctrl com a corrente do CP ( $I_{CP}$ ). Esse bloco, além de informar a diferença entres as fases, também mostra se a diferença é positiva ou negativa. É necessário atenção no projeto desses blocos em relação ao descasamento entre esses sinais (Up e Down) e entre essas correntes  $I_{CP}$  de carga e de descarga, pois esse é um grande fator que causa os spurs da referência no PLL tipo II.

Figura 10 – Modelo para PLL tipo II Fonte: (Autor - 2023)

Para a análise da malha, o modelo na Figura 10 é utilizado neste trabalho.

A combinação do CP + LF gera um polo adicional na origem em malha aberta, sendo esse um PLL tipo II. Essa combinação opera como um integrador fazendo com que o erro de fase em estado estacionário seja nulo, diferentemente do PLL tipo I. A função de transferência do PFD + CP + LF, derivada em (RAZAVI, 2011) pode ser vista abaixo.

$$\frac{vctrl}{\Lambda\Phi} = K_{CP} \frac{\frac{s}{\omega_z} + 1}{s} \tag{10}$$

onde,  $K_{CP} = \frac{I_{cp}}{2\pi C}$  e  $\omega_Z = 1/(RC)$  é o módulo da frequência angular do zero. <sup>1</sup> A função de transferência em malha aberta  $(A_{OL})$  é,

$$A_{OL}(s) = K_{CP} K_{VCO} \frac{1 + s/\omega_Z}{s^2 N}$$

(11)

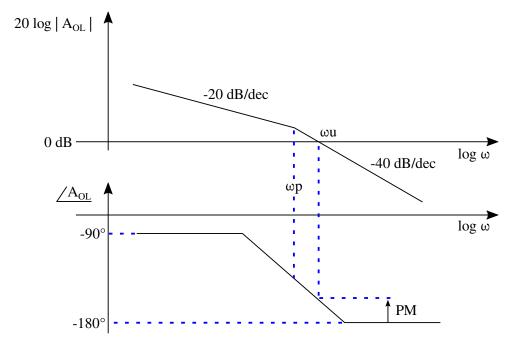

O diagrama de Bode é representado pelas assíntotas na Figura 11.

A inclinação de -40 dB/dec na magnitude do ganho em baixas frequências é causado pelos dois polos localizados na origem. Ao contrário do PLL tipo I, quanto maior o ganho de malha melhor é a estabilidade do sistema, pois  $\omega_u$  aumenta, e isso implica em uma maior margem de fase como mostrado na figura<sup>2</sup>. Aumentando também o valor da capacitância do filtro de malha, resulta em uma diminuição na frequência do zero; consequentemente, melhora a estabilidade do sistema. Logo, não temos um compromisso entre o valor da capacitância do filtro e estabilidade do sistema como para o PLL tipo I.

$<sup>^{1}</sup>$ Em termos de projeto é mais útil escrever as equações em função das variáveis de projeto ( $I_{CP}$ , R e C), porém o foco nesta seção é ter uma ideia geral do sistema; então, optou-se por escrever em termos de ganhos, polos e zeros.

<sup>&</sup>lt;sup>2</sup>Na verdade há um limite para ganho de malha muito elevado, pois isso aumentaria a banda do PLL acarretando em uma piora na aproximação do tempo contínuo

Figura 11 – Comportamento da função de transferência em malha aberta do PLL tipo II

Fonte: (Autor - 2023)

A função de transferência em malha fechada  $(A_{CL})$  é mostrada na equação abaixo.

$$A_{CL}(s) = \frac{K_{CP}K_{VCO}\left(\frac{s}{\omega_z} + 1\right)}{s^2 + \frac{K_{CP}K_{VCO}}{\omega_z N}s + \frac{K_{CP}K_{VCO}}{N}}$$

(12)

Escrevendo o denominador na forma  $s^2 + 2\zeta \omega_n s + \omega_n^2$  é possível chegar nas equações abaixo.

$$\zeta = \frac{1}{2\omega_z} \sqrt{\frac{K_{CP} K_{VCO}}{N}} \tag{13}$$

$$\omega_n = \sqrt{\frac{K_{CP}K_{VCO}}{N}} \tag{14}$$

Os valores para  $\zeta$  e  $\omega_n$  afetam a constante de tempo da malha que é entre  $1/(2\zeta\omega_n)$  e  $1/(\zeta\omega_n)$  como descrito em (RAZAVI, 2011).

#### 2.1.1.2.1 Ruído em PLL Tipo II

A mesma análise de ruído feita para o PLL tipo I também pode ser feita para o PLL tipo II. Neste trabalho, essa análise é feita usando o modelo de ruído mostrado na Figura 12.

Os principais contribuidores ao ruído são considerados neste modelo. O ruído na saída do PLL é composto pela soma dos contribuidores, sendo cada um deles

Figura 12 – Modelo de ruído do PLL tipo-II Fonte: (Autor - 2023)

mostrado nas equações de (15) a (18).

$$\frac{S_{N,PLL}}{S_{N,REF}} = \left| A_{CL}(j\omega) \right|^2 \tag{15}$$

$$\frac{S_{N,PLL}}{S_{N,DIV}} = \left| A_{CL}(j\omega) \right|^2 \tag{16}$$

$$\frac{S_{N,PLL}}{S_{N,CP}} = \left| \frac{A_{CL}(j\omega)}{K_{CP}} \right|^2 \tag{17}$$

$$\frac{S_{N,PLL}}{S_{N,VCO}} = \left| 1 - \frac{A_{CL}(j\omega)}{N} \right|^2 \tag{18}$$

As funções de transferência e a contribuição ao ruído estão desenhadas na Tabela 3 em função da frequência de *offset*. A magnitude da frequência dos polos complexos  $\omega_{comp}$  estão presentes em sistemas onde  $\zeta$  < 1. Note que em baixas frequências, o ruído do VCO é fortemente atenuado neste tipo de PLL se comparado ao PLL tipo I; isso é devido à característica da malha.

Análogo ao PLL tipo I, existe um compromisso com relação a quanto de ruído dos blocos Divisor+PFD+CP é atenuado e quanto de ruído do VCO é atenuado para a contribuição do ruído de fase na saída do PLL.

Os PLLs também podem ser divididos com relação ao valor que podem multiplicar a frequência de referência. Eles são chamados de PLL N inteiro e PLL N fracionário. A seguir é mostrada a diferença entre essas arquiteturas e como cada uma delas opera.

#### 2.1.1.3 PLL N-Inteiro

PLL N inteiros são aqueles em que a divisão da frequência é feita por um valor inteiro. Dessa forma o valor da frequência de saída consegue atingir somente valores

Tabela 3 – Contribuição dos ruídos dos blocos no ruído de fase para PLL tipo II

múltiplos da frequência de referência.

Como a banda do PLL é limitada a aproximadamente um décimo da frequência de referência, não é viável para PLL N inteiro ter um passo de frequência pequeno, entre um canal e outro, pois seria necessário um baixo valor para a frequência de referência e consequentemente, uma banda muito pequena para este PLL. Outra desvantagem para uma frequência de referência baixa é a contribuição do ruído dos blocos: referência, PFD+CP e divisor, pois estes são multiplicados por N, o que resulta em uma maior contribuição ao ruído de fase no PLL. Neste caso, PLL N fracionário é empregado.

#### 2.1.1.4 PLL N Fracionário

O PLL N fracionário tem a capacidade de multiplicar a frequência por uma fração do valor da frequência de referência. O jeito simples de fazer essa fração é dividir a frequência ora por um valor e ora por outro. Se, por exemplo, metade do tempo o PLL divide a frequência por 64 e outra metade por 65 o resultado final será de uma divisão por 64,5.

Pelo fato de a malha do PLL ter uma característica passa-baixa, essa variação entre 64 e 65 é filtrada. Porém, a filtragem natural da malha não é suficiente e são gerados *spurs da referência*, pois essa variação apresenta uma periodicidade igual ao

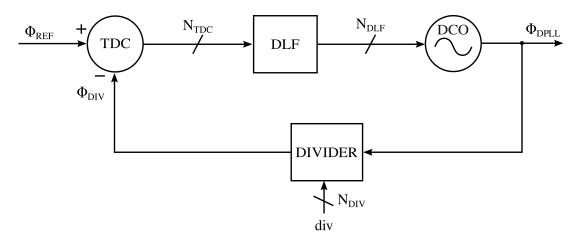

Figura 13 – Diagrama de blocos de um DPLL convencional Fonte: (Autor - 2023)

valor da referência. Por isso técnicas como modulação sigma delta pode ser empregada como em (RIANO, 2010) fazendo a randomização de divisão fracionária.

Mesmo com a randomização, o PLL N fracionário apresenta os chamados *spurs* fracionários. Isso acontece por causa dessa divisão parcial ainda possuir componentes periódicos. Portanto, técnicas como *dithering* podem ser empregadas para minimizar tais *spurs* (HO; CHEN, M. S.-W., 2019).

#### 2.2 PLLs com Compensação Digital (DPLLs)

Os PLLs podem ser com compensação analógica, como aqueles PLLs convencionais que temos detalhado até esse ponto. Há também os PLLs híbridos (KIM; CHO, 2019), onde temos blocos analógicos e digitais para fazer a compensação da malha, PLLs com compensação no domínio digital, chamados nesse projeto de DPLLs, e também os PLLs puramente digitais, sendo seu projeto geralmente feito totalmente no domínio digital como em (KHALIRBAGINOV, 2021).

#### 2.2.1 Elementos básicos

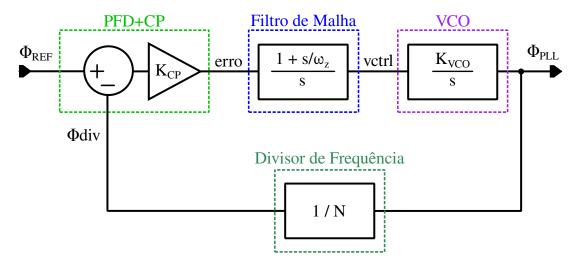

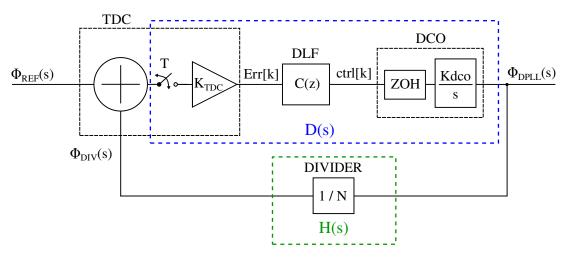

O DPLL é composto basicamente dos blocos: TDC, DLF, DCO e divisor de frequência. Seu diagrama de blocos em alto nível pode ser visto na Figura 13.

O TDC é o circuito que gera em sua saída um valor proporcional à diferença entre a fase do sinal de referência e a fase do sinal de retorno. Essa saída, conhecida como erro, é representada por uma palavra digital.

DLF é um circuito inteiramente digital responsável pela geração dos polos e zeros para a compensação da malha. O projeto deste circuito afeta diretamente as características do DPLL como ruído, tempo de acomodação e estabilidade. Nesta dissertação é mostrado um exemplo de como projetar esse bloco para um DPLL tipo I e a base teórica para o projeto desse bloco para DPLL tipo II.

O DCO é o circuito que faz a conversão da palavra digital gerada pelo DLF em um sinal de frequência proporcional ao valor da palavra digital.

O divisor de frequência funciona exatamente como nos PLLs convencionais, a frequência em  $\Phi_{div}$  é N vezes menor que a frequência em  $\Phi_{out}$ .

Na Figura 13 os símbolos  $N_{DIV}$ ,  $N_{TDC}$  e  $N_{DLF}$  representam o número de bits dos barramentos digitais existentes no DPLL, definidos de acordo com as especificações do DPLL. O  $N_{DIV}$  é escolhido de acordo com a faixa de frequência em que o DPLL deve operar e também o valor do passo entre as frequências. O  $N_{TDC}$  é definido de acordo com o ruído de quantização projetado no TDC. E  $N_{DLF}$  é de acordo com o número de bits presentes no DCO.

#### 2.2.2 Vantagens e Desvantagens Comparado ao PLL Convencional

Existem algumas vantagens do PLL compensado digitalmente comparado com o PLL convencional com malha analógica.

As vantagens são:

- Flexibilidade: Os DPLLs são mais flexíveis em relação à implementação dos polos e zeros da malha.

- Portabilidade: Uma vez que há um projeto existente eles são mais fáceis e rápidos de portar entre um projeto e outro e, até mesmo, entre tecnologias diferentes.

- Variações de processo: Circuitos digitais são mais resilientes a variações de processo comparados aos blocos analógicos do PLL convencional, deixando assim o projeto mais robusto.

- Consumo de potência: Circuitos digitais conseguem trabalhar com uma tensão de alimentação menor que circuitos analógicos; consequentemente, menor o consumo de potência utilizado.

#### E as desvantagens são:

- Ruído de quantização: Por causa da natureza dos circuitos digitais existem os ruídos de quantização. Esses ruídos são menos impactantes em tecnologias mais avançadas, pois a resolução no domínio do tempo de transições dos sinais digitais é maior e comparável à de sinais analógicos (STASZEWSKI et al., 2004).

- Limitação de velocidade: Circuitos digitais apresentam limitações quanto à máxima frequência de operação; porém, em menor grau em tecnologias mais avançadas.

- Complexidade: Para os DPLLs obter uma boa performance, utilizam técnicas avançadas no projeto que, geralmente, aumentam a complexidade.

• Complexidade: Os DPLLs possuem uma complexidade maior para obter uma boa performance, pois utilizam de técnicas avançadas no projeto.

Em resumo, os DPLL são muito vantajosos comparado ao PLL convencional quando utilizados em tecnologias mais avançadas, onde as desvantagens do DPLL são minimizadas. Porém a complexidade deste aumenta tanto no projeto quanto na verificação.

### 2.3 Topologias dos Blocos

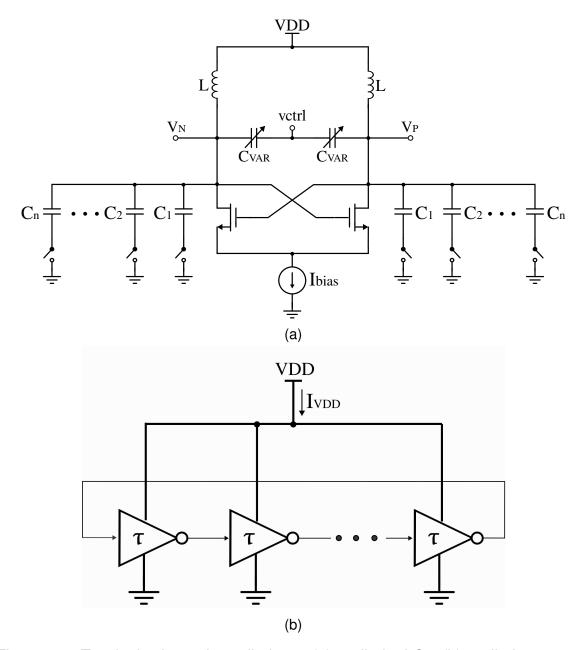

# 2.3.1 Oscilador Controlado Digitalmente

Nesta seção são mostrados os tipos de DCO mais comuns apresentados em projetos de circuitos integrados. Os dois principais tipos de DCOs são divididos em: DCOs baseados em osciladores LC e baseados em osciladores em anel, mostrados na Figura 14a e 14b, respectivamente. Para cada um desses tipos de DCOs existem diversas topologias, cada uma com suas vantagens e desvantagens. Aqui serão explicadas apenas as duas configurações apresentadas na Figura 14.

Os DCOs baseados em oscilador em anel, além da possibilidade de utilizar múltiplas fases, têm menor impacto em área comparado aos DCOs baseados em oscilador LC. Entretanto, estes últimos apresentam melhor compromisso entre ruído de fase e consumo de potência.

Um dos desafios no projeto de DCOs, além das especificações de ruído e consumo, é cobrir uma faixa necessária de frequência (considerando variações PVT), com alta resolução e, acima disso, que a variação da frequência em função da palavra digital na entrada seja o mais linear possível.

Algumas técnicas para o controle da frequência são mostradas a seguir.

- 1. Chaves para adicionar capacitâncias nos nós

- DCOs com essa técnica podem ser tanto os osciladores LC quanto os osciladores em anel. A Figura 14a mostra uma opção de como adicionar os capacitores nos nós em osciladores LC. Quanto mais capacitâncias conectadas ao nó menor é a frequência de oscilação. A condição de cada chave (aberta ou fechada) conectada a esses capacitores é determinada pelo valor da palavra digital de entrada do DCO. Outro método pode ser utilizado mudando a capacitância entre os nós *VP* e *VN* do oscilador como em (ZHANG; OTTO, 2017).

- 2. Controlar a corrente que alimenta o oscilador ou a tensão de alimentação Esse ajuste é feito na corrente I<sub>VDD</sub> ou na tensão de alimentação VDD como mostra a Figura 14b. Esta é uma técnica utilizada em oscilador em anel. Quanto maior a corrente entregue para o oscilador ou sua tensão de

Figura 14 – Topologias base de osciladores, (a) oscilador LC e (b) oscilador em anel Fonte: (Autor - 2023)

alimentação, maior é sua frequência de oscilação. A variação dessa corrente, ou tensão, é feita através da palavra digital de entrada. Com relação ao controle por corrente, ela também pode ser feita pelo GND ao invés de VDD como em (SELVARAJ; BAYRAM; NEGRA, 2020).

# 3. Modificar a constante de tempo $(\tau)$ nas células de atraso

No caso de osciladores em anel, também há a possibilidade de controlar a frequência alterando a constante de tempo de cada célula. Um jeito de implementar isso é modificar a força dos transistores da célula de atraso. Um exemplo do uso desse método é proposto em (LIN; LU; CHEN, Y.-J. E., 2019).

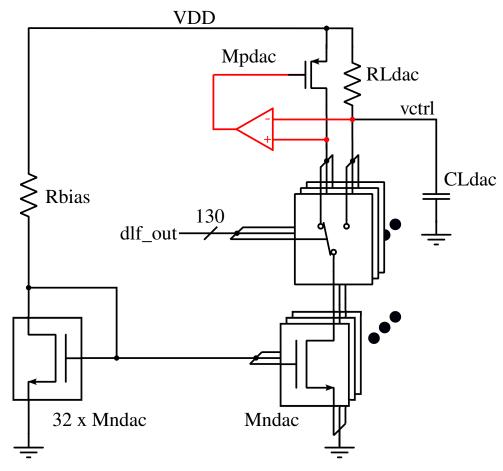

4. Usar um Conversor Digital-Analógico (*Digital to Analog Converter -* DAC) junto com VCO

O uso do DAC pode ser feito separadamente do VCO como em (BHANDARI; KOTABAGI; NAYAK, 2021). A principal vantagem dessa escolha está na diminuição dos *spurs* na saída, pois o polo gerado na saída do DAC pode ser projetado para atenuar componentes de interferência na tensão de controle do DPLL.

# 2.3.2 Filtro de Malha Digital

O filtro digital tem que ser adequadamente projetado examinando o lugar dos polos e zeros, que afetam a performance do DPLL.

Dentre as variedades de filtros digitais, o projeto pode ser feito considerando os polos e zeros de forma similar à de um PLL tipo I ou tipo II.

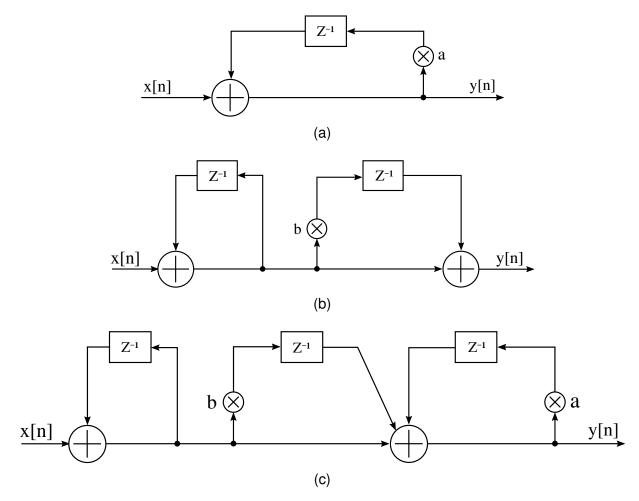

Nesta seção são apresentados os filtros conhecidos como *Infinite Impulse Response* (IIR). As Figuras 15a e 15b mostram como pode ser feita a implementação de tais filtros para PLL tipo I e tipo II, respectivamente. Um exemplo adicional pode ser visto na Figura 15c sendo uma implementação de um filtro digital para DPLL tipo II de terceira ordem.

Na Figura 15a é gerado somente um polo no filtro, a Figura 15b é gerado polo na origem e um zero, enquanto na Figura 15c são gerados dois polos, sendo um deles na origem, e um zero.

A equação de transferência de cada um desses exemplos segue abaixo.

$$\frac{y}{x} = \frac{1}{1 - az^{-1}} \tag{19}$$

$$\frac{y}{x} = \frac{1 + bz^{-1}}{1 - z^{-1}} \tag{20}$$

$$\frac{y}{x} = \frac{1}{1 - z^{-1}} \cdot \frac{1 + bz^{-1}}{1 - az^{-1}} \tag{21}$$

Nestes filtros, as malhas de *feedforward* representam os zeros do filtro e as malhas de retorno representam os polos. Dessa forma, com específicos coeficientes "a" e "b" e também específicos atrasos, os polos e zeros podem ser devidamente projetados.

O projeto do filtro digital utilizado no projeto pode ser visto na seção 3.5.

# 2.3.3 Conversor de tempo para digital

Nesta seção são apresentadas as topologias mais comuns do TDC encontradas na literatura.

Figura 15 – Exemplo de filtro digital para DPLL (a) tipo I, (b) tipo II de segunda ordem e (c) tipo II de terceira ordem

Fonte: (Autor - 2023)

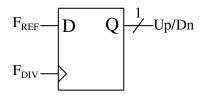

# 2.3.3.1 Detector de Fase Bang-Bang

O detector de fase *Bang-Bang* é uma topologia geralmente simples. A construção mais simples é com um *flip-flop* tipo D como na Figura 16. Esta figura mostra um detector de fase *Bang-Bang* de 1 bit. Sua saída mostra quando a borda de subida do sinal de realimentação ocorre antes ou depois da borda de subida do sinal de referência. Por não apresentar uma resolução boa, a desvantagem dessa topologia é o ruído de quantização que geralmente influencia no ruído em banda do DPLL.

Existem outras topologias de detectores de fase Bang-Bang, onde a saída pode

Figura 16 – Detector de fase *Bang-Bang* de 1 bit Fonte: (Autor - 2023)

Figura 17 – TDC convencional Fonte: (Autor - 2023)

atingir mais que dois valores, informando a posição da fase de retorno em relação à fase da referência e também se o erro está dentro de uma faixa aceitável.

Existem publicações apresentando o detector *Bang-Bang* com mais possíveis valores em sua saída como em (KANG; LIU, 2022).

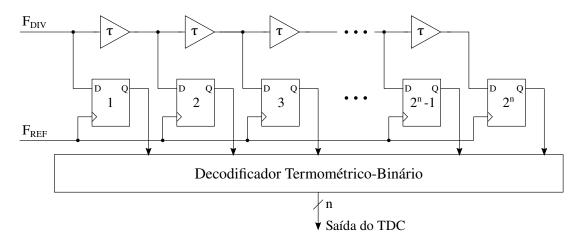

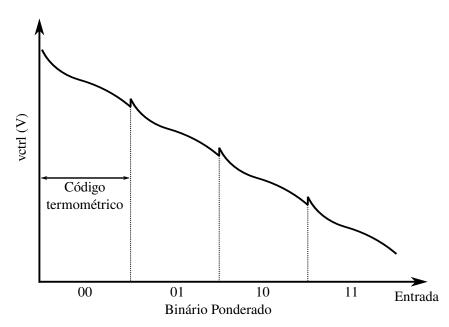

# 2.3.3.2 Conversor de Tempo Para Digital Convencional

Esta topologia consiste em N *buffers* em cascata, cada saída de um *buffer* conecta à entrada D de um *flip-flop* (Figura 17). O sinal da saída do divisor de frequência é conectado na entrada do primeiro *buffer* enquanto o sinal de referência é conectado no terminal de relógio dos *flip-flops*. O sinal do divisor se propaga na cadeia de *buffers*; quando o sinal da referência faz a transição de subida, as saídas dos *flip-flops* recebem o valor de suas entradas. Dessa forma, a combinação da saída dos *flip-flops* é de código termométrico <sup>3</sup> representando a diferença no tempo entre o sinal do divisor e o sinal da referência.

Uma característica dessa topologia é que o erro de quantização é limitado pelo atraso  $(\tau)$  da célula do *buffer*. A topologia a seguir apresenta uma melhoria com relação a essa limitação. Outra desvantagem é que o número de estágios pode ficar muito grande se o período da referência for muito maior que o atraso do *buffer*, ocasionando maior área no silício.

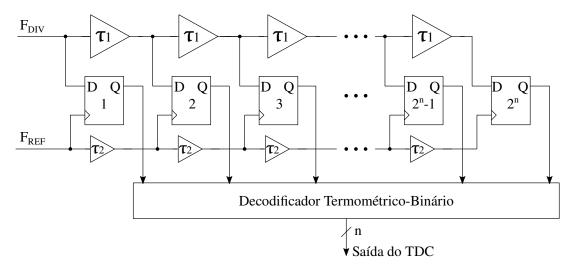

### 2.3.3.3 Arquitetura Vernier

Essa topologia é similar à topologia convencional com a diferença que outra rede de *buffers* é colocada em cascata também no sinal de relógio entre um *flip-flop*

<sup>&</sup>lt;sup>3</sup>Código termométrico representa os valores binários com uma sequência de 0s e 1s de forma que não há nenhuma intercalação entre 0 e 1. Por exemplo, o número decimal 3 pode ser representado por 111, o decimal 2 por 011, 1 por 001 e 0 por 000. Também existe o código bolha, que é a mesma representação, porém invertendo o valor de todos os bits.

Figura 18 – TDC Vernier Fonte: (Autor - 2023)

e outro, como mostrado na Figura 18. Mantendo uma diferença entre os atrasos dos *buffers* das entradas dos *flip-flops* em relação ao atraso dos *buffers* do sinal de relógio, a resolução não é mais limitada pelo atraso do *buffer* de entrada e sim pela diferença entre os atrasos dos *buffers* de entrada e os *buffers* do sinal de relógio  $(\tau_1 - \tau_2)$ .

Apesar de essa topologia ter uma melhoria grande com relação ao erro de quantização, ela sofre ainda mais para conseguir cobrir toda a faixa do período do sinal de referência. Existem estratégias para melhorar isso, uma delas é combinar essa topologia com a topologia convencional em cascata diminuindo o número de estágios e mantendo a resolução da arquitetura.

O bloco a seguir apresenta a vantagem de cobrir uma maior faixa do período do sinal da referência sem aumentar a área do circuito.

# 2.3.3.4 Ring Oscillator TDC (RO-TDC)

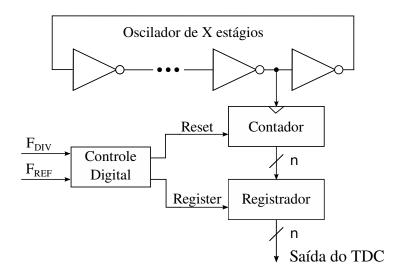

Essa topologia pode ser vista na Figura 19. Ao invés de usar uma cadeia de inversores com um número relativamente grande para cobrir a faixa do período do sinal da referência, essa topologia apresenta um oscilador em anel com X estágios; logo, o sinal que se propaga até o último inversor retorna ao primeiro. Um contador é empregado para contar as transições que ocorrem em um dos estágios do oscilador.

A desvantagem desse circuito é que a resolução do TDC é  $(2 \times X)$  vezes menor do que a resolução de uma transição da célula de atraso do oscilador, considerando que o contador funciona apenas nas bordas de subida ou de descida. Sendo assim, quanto maior o número de estágios do oscilador, menor é a resolução deste. Uma forma de melhorar isso é usar contadores em todos os estágios do oscilador, porém isso aumenta muito a área e o consumo de potência do circuito.

Em (HSU; STRAAYER; PERROTT, 2008) é proposto um circuito adicional que faz a leitura do estado do oscilador, melhorando a resolução do TDC e também a sua

Figura 19 – TDC baseado em oscilador em anel Fonte: (Autor - 2023)

eficiência.

No trabalho desta dissertação, a ideia de usar um bloco para obter a informação do estado do oscilador também é empregada, como detalhado no Capítulo 3.

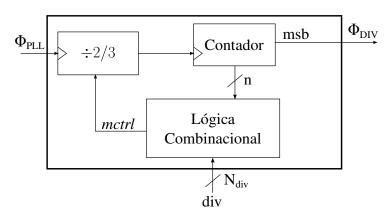

# 2.3.4 Divisor de Frequência

Circuitos sequenciais são comuns para o projeto do divisor de frequência. Para uma divisão fixa, um divisor utilizando somente *flip-flops* pode ser uma solução. Porém, na maioria das aplicações, o PLL deve oscilar em mais de uma frequência e, para isso, é necessário um circuito que faça a divisão da frequência por valores diferentes de acordo com o valor da palavra digital que recebe como entrada.

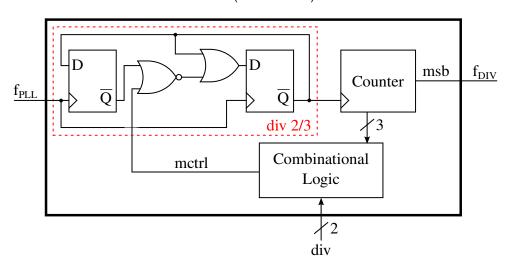

Um circuito que realiza tal tarefa é o divisor multi módulo. Um método simples para o projeto deste circuito é com o uso de um contador, uma lógica combinacional e um divisor 2/3 como mostrado na Figura 20. O bit representado por "mctrl" na figura, controla se o divisor 2/3 funciona como um divisor por 2 ou por 3. A lógica combinacional controla o sinal "mctrl" de acordo com o valor da palavra digital "div", consequentemente o valor do sinal "mctrl" é '0' para um valor específico de pulsos na entrada e '1' para o restante, controlando o valor da divisão total do divisor multi módulo.

No caso de PLLs N fracionário, algumas técnicas são necessárias para conseguir um fator de divisão, como o nome já diz, fracionário. Para implementar tal divisão, é necessário que parte dos pulsos seja dividido por um módulo e a outra parte por outro módulo, resultando em um valor médio para a divisão. O maior problema disso está na geração de sinais periódicos na malha, ocasionando os *spurs* na saída.

Figura 20 – Estrutura de exemplo de um divisor multi módulo Fonte: (Autor - 2023)

# 3 Projeto do PLL Digital

Neste capítulo é apresentado o circuito projetado para o DPLL. Também é mostrada a topologia utilizada em cada bloco usado.

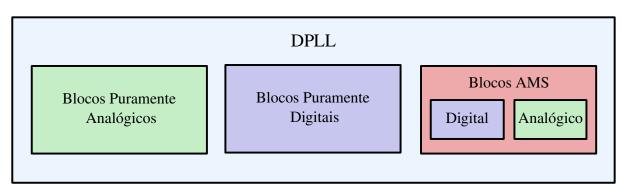

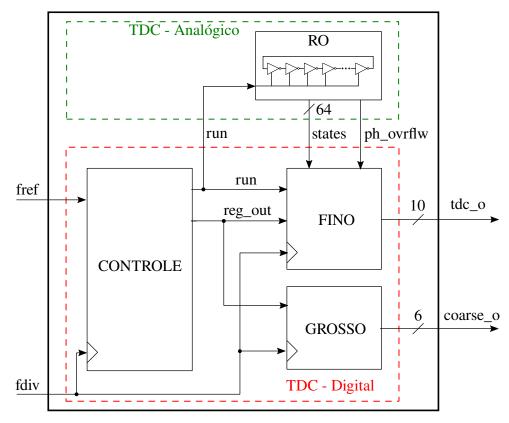

A Figura 21 ilustra os domínios dos blocos usados no DPLL. Nesta figura está evidente que o DPLL possui três tipos diferentes de blocos, (i) analógicos como DAC, VCO e estruturas de depuração; (ii) blocos digitais como DLF e divisor de frequências; e (iii) bloco AMS (*Analog and Mixed-Signal*) como o caso do TDC que possui um oscilador interno analógico e decodificadores digitais.

Para a simulação em nível de sistema, uma *view* para a configuração das instâncias que o DPLL contém foi criada. Por meio dessa *view*, é possível configurar qual bloco vai ser simulado com modelo Verilog, com um *netlist* em nível de transistor, com uma *view* com os componentes parasitas do leiaute ou com um *netlist* extraído do esquema elétrico (entre outras opções).

# 3.1 Malha de Controle de Fase com Compensação Digital (DPLL)

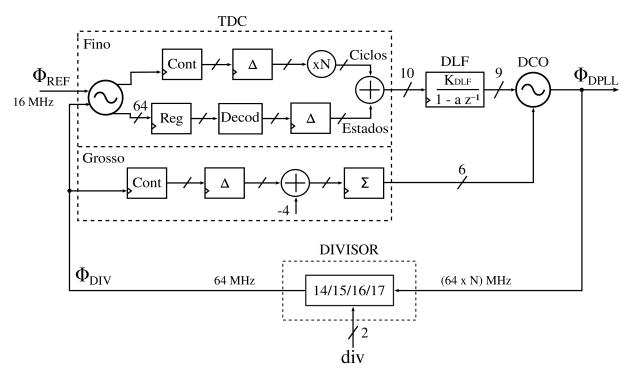

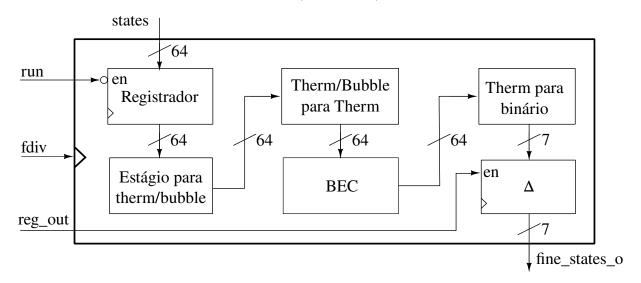

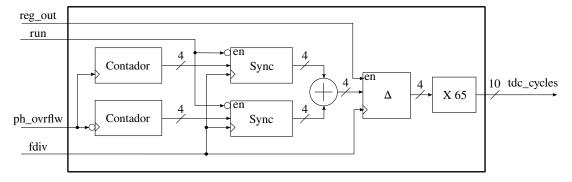

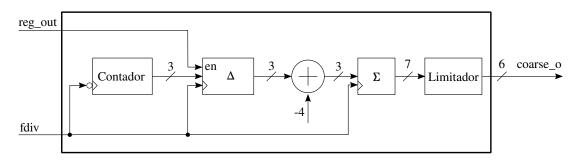

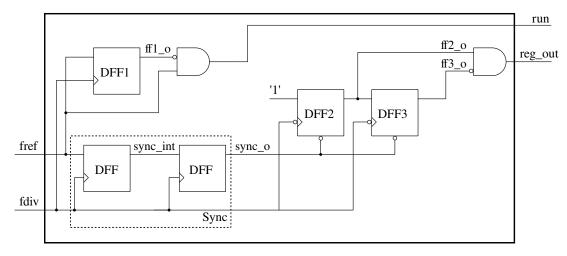

Nesta seção são explicadas detalhes de cada parte do circuito proposto ilustrado na Figura 22.

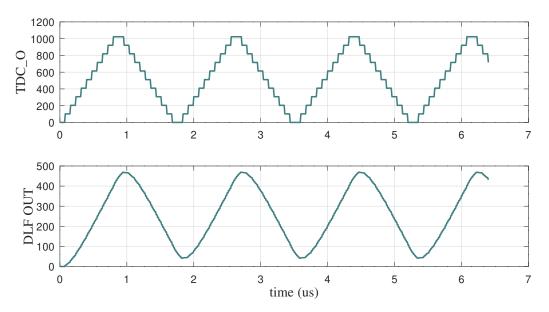

Ele consiste em um TDC que é dividido em duas partes, uma faz o controle automático de ajuste grosso e a outra faz o ajuste fino. O DLF está com sua representação no domínio z. O DCO recebe duas palavras digitais de entrada, sendo uma proveniente do controle grosso e a outra do ajuste fino. O divisor de frequências recebe uma palavra de dois bits para a escolha do módulo da divisão.

O DCO é composto por dois blocos internamente, DAC e VCO. O DAC converte a palavra digital de sua entrada e transforma em uma tensão de controle para o VCO. O VCO utiliza essa tensão como um ajuste fino da frequência e também possui uma estrutura para o controle grosso da frequência. Usando essa mistura de controle fino e controle grosso, torna-se mais fácil atingir uma faixa ampla de frequências e, ao mesmo tempo, conseguir uma boa resolução.

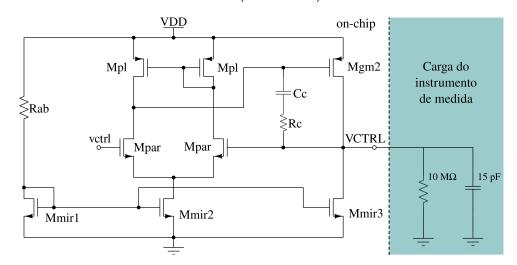

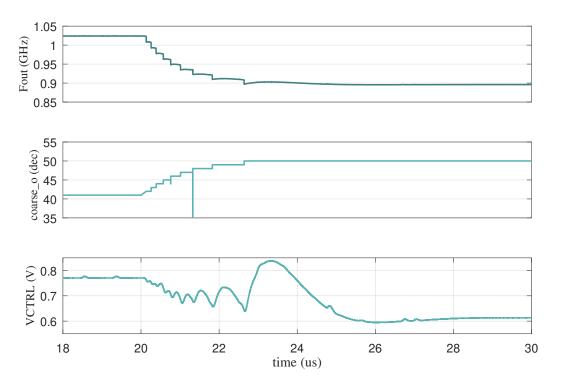

Figura 21 – Domínio dos blocos existentes no DPLL Fonte: (Autor - 2023)