# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO DEPARTAMENTO DE ENGENHARIA ELÉTRICA E ELETRÔNICA CURSO DE ENGENHARIA ELÉTRICA

|                                 | Caio Yugo Hanada Akir    | naga                         |

|---------------------------------|--------------------------|------------------------------|

| Validação em <i>Hardware-in</i> | e-the-loop para Sistemas | de Gerenciamento de Baterias |

|                                 |                          |                              |

| Caio Yugo Hanada Akinaga                 |                                                                                                                                                                                                                                                                                  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                          |                                                                                                                                                                                                                                                                                  |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

| Validação em Hardware-in-the-loop para S | Sistemas de Gerenciamento de Baterias                                                                                                                                                                                                                                            |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

| Eng<br>Un<br>par<br>Elé<br>Ori           | abalho Conclusão do Curso de Graduação em genharia Elétrica do Centro Tecnológico da iversidade Federal de Santa Catarina como requisito ra a obtenção do título de Bacharel em Engenharia étrica. ientador: Prof. Gierri Waltrich, Dr. orientador: Gabriel Manoel da Silva, Me. |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

|                                          |                                                                                                                                                                                                                                                                                  |  |

| Florianóp<br>2024                        |                                                                                                                                                                                                                                                                                  |  |

Ficha catalográfica gerada por meio de sistema automatizado gerenciado pela BU/UFSC.

Dados inseridos pelo próprio autor.

Akinaga, Caio Yugo Hanada

Validação em Hardware-in-the-loop para Sistemas de

Gerenciamento de Baterias / Caio Yugo Hanada Akinaga;

orientador, Gierri Waltrich, coorientador, Gabriel Manoel

da Silva, 2024.

117 p.

Trabalho de Conclusão de Curso (graduação) -Universidade Federal de Santa Catarina, Centro Tecnológico, Graduação em Engenharia Elétrica, Florianópolis, 2024.

Inclui referências.

1. Engenharia Elétrica. 2. Hardware-in-the-loop. 3. Gerenciador de Baterias. 4. Interface HIL-BMS. I. Waltrich, Gierri. II. da Silva, Gabriel Manoel. III. Universidade Federal de Santa Catarina. Graduação em Engenharia Elétrica. IV. Título.

#### Caio Yugo Hanada Akinaga

### Validação em Hardware-in-the-loop para Sistemas de Gerenciamento de Baterias

Este Trabalho Conclusão de Curso foi julgado adequado para obtenção do Título de Bacharel em Engenharia Elétrica e aprovado em sua forma final pelo Curso de Engenharia Elétrica.

| Florianópolis, 12 de julho de 2024.                      |

|----------------------------------------------------------|

|                                                          |

|                                                          |

|                                                          |

| Prof. Miguel Moreto, Dr.                                 |

| Coordenador do Curso de Graduação em Engenharia Elétrica |

| Banca Examinadora:                                       |

| <del></del>                                              |

Prof. Gierri Waltrich, Dr.

Orientador

Universidade Federal de Santa Catarina

Prof. André Luís Kirsten, Dr.

Avaliador

Universidade Federal de Santa Catarina

Thiago Fonseca Rech, Me.

Avaliador

Universidade Federal de Santa Catarina

Este trabalho é dedicado aos meus amigos da Waldorf, universidade e da monitoria e, principalmente, aos meus queridos pais, irmãs e avós.

#### **AGRADECIMENTOS**

Primeiramente, agradeço ao Prof. Gierri que me guiou ao longo da graduação na iniciação científica e no TCC oferecendo suporte e conhecimento. Também agradeço ao Thiago, Gabriel e Antonio Pacheco bem como ao INEP e Atlas Power que acreditaram no projeto oferecendo suporte durante todo o percurso desse TCC.

A qualidade desse trabalho não seria possível sem a confiança do Eduardo que, em nome da WEG Drives & Controls, acreditou no potencial do projeto e ajudou diretamente nos protótipos finais. Agradeço ao conhecimento de eletrônica, layout de PCI e afins passados pelo Adriano e Marcos durante o período de estágio que contribuíram significantemente no resultado do trabalho.

Gostaria de agradecer a todos que puderam contribuir durante o percurso da minha trajetória. Em especial, aos meus amigos da Waldorf que, por anos, cultivaram a amizade, aos meus colegas de faculdade, da monitoria inclusos, que, sem o imensurável companheirismo nada seria possível, e aos meus professores que instigaram a curiosidade em mim para desbravar o conhecimento do mundo.

Agradeço, principalmente, aos meus pais que acreditaram nos meus objetivos e sempre proporcionaram tudo para pudesse alcançá-los. Às minhas irmãs, agradeço a convivência e experiências juntos. Não menos importante, aos meus queridos avós que participaram da minha vida e cuidaram de mim desde pequeno.

Por fim, ressalto a contribuição dos cidadãos dessa nação que, por meio de seu árduo trabalho, puderam custear meu aprendizado.

Novamente, obrigado a todos.

"There is perhaps no better demonstration of the folly of human conceits than this distant image of our tiny world. To me, it underscores our responsibility to deal more kindly with one another, and to preserve and cherish the pale blue dot, the only home we've ever known." (Sagan, 1994)

#### **RESUMO**

Dispositivos de gerenciamento de baterias (BMS) ganharam destaque nas últimas décadas com o crescente interesse no desenvolvimento de tecnologias de fontes sustentáveis de energia elétrica combinados à demanda por aparelhos móveis e veículos elétricos cada vez mais eficientes e robustos. Com a popularização da validação em hardware-in-the-loop (HIL), nos quais complexos módulos elétricos podem ser simulados em tempo real via microcontrolares a fim de testar a funcionalidade de um dispositivo físico. Em HIL, extensos packs de baterias são representados por modelos matemáticos difundidos na área acadêmica e industrial. No entanto, limitações nas características elétricas desses dispositivos de simulação impõem desafios à replicação de tensões ou potência dos módulos reais. O presente trabalho, portanto, estabelece uma estratégia à conexão entre um dispositivo HIL e um BMS. Para tornar isso possível, foi desenvolvido uma interface física em placa de circuito integrada que, além de possibilitar a simulação de baterias em série, fornece sinais de estado tais como temperatura das baterias, corrente circulante e comunicação, controladas em tempo real pelo algoritmo desenvolvido no software Typhoon HIL Control Center. Para comprovação do método criado, propôs-se testes para validação da interface projetada e da integração entre BMS e o HIL. Os resultados obtidos mostram que a interface teve sucesso na simulação de pack de bateria e demais parâmetros e comprovam compatibilidade com BMS comercial. Este trabalho contribui para a área de sistemas de supervisão de armazenadores de energia fornecendo de inspiração a novos trabalhos.

**Palavras-chave:** *Hardware-in-the-loop.* Gerenciador de Baterias. Interface HIL-BMS.

#### **ABSTRACT**

Battery Management Systems (BMS) have gained prominence in recent decades due to the growing interest in developing sustainable electrical energy source technologies combined with the demand for increasingly efficient and robust mobile devices and electric vehicles. With the popularization of hardware-in-the-loop (HIL) validation, in which complex electrical modules can be simulated in real-time via microcontrollers to test the functionality of a physical device, HIL extensively represents battery packs through mathematical models widely recognized in academic and industrial fields. However, limitations in the electrical characteristics of these simulation devices pose challenges to replicating the voltages or power of actual modules. This work, therefore, establishes a strategy for the connection between an HIL device and a BMS. To make this possible, a physical interface was developed on an integrated circuit board that, in addition to enabling the simulation of batteries in series, provides state signals such as battery temperature, circulating current and communication, controlled in real-time by the algorithm developed in the Typhoon HIL Control Center software. To validate the created method, tests were proposed to validate the designed interface and the integration between the BMS and the HIL. The results obtained show that the interface successfully simulated the battery pack and other parameters and proved compatibility with commercial BMS. This work contributes to the field of energy storage supervision systems by providing inspiration for new research.

**Keywords:** Hardware-in-the-loop. Battery Management System. HIL-BMS Interface.

## LISTA DE FIGURAS

| Figura 1- Pilha tipo D, espécie de bateria. Terminal positivo em destaque por cor, escrita e |

|----------------------------------------------------------------------------------------------|

| mecânica23                                                                                   |

| Figura 2 – Esquemático da configuração dos orbitais tipo s, p, d e f de cima para baixo 24   |

| Figura 3 - Diagrama de Linus Pauling. A seta vermelha indica a ordem da configuração         |

| eletrônica do átomo de acordo com o princípio de Aufbau                                      |

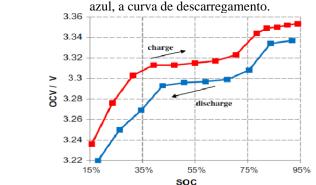

| Figura 4 - Representação gráfica do estado de carga de uma bateria, em vermelho, curva de    |

| carregamento, em azul, a curva de descarregamento                                            |

| Figura 5 - Diagrama esquemático do modelo de Tensão de Circuito Aberto para células de       |

| bateria32                                                                                    |

| Figura 6 - Diagrama esquemático do modelo de Tensão de Circuito Aberto Variável para         |

| células de bateria                                                                           |

| Figura 7 – Diagrama esquemático do modelo de Resistência Série Equivalente para células de   |

| bateria                                                                                      |

| Figura 8 – Curva típica de célula de bateria sob pulso de corrente de descarga               |

| Figura 9 - Diagrama esquemático do modelo de Tensão na Célula por Thévenin para células      |

| de bateria                                                                                   |

| Figura 10 - Diagrama esquemático do modelo de Impedância de Warburg com Circuito de          |

| Randles para células de bateria                                                              |

| Figura 11 - Diagrama esquemático do modelo de rede em série de capacitor-resistor em         |

| paralelo para células de bateria40                                                           |

| Figura 12 - Representação gráfica do fluxo de trabalho do modelo em cascata conforme o       |

| andamento do projeto                                                                         |

| Figura 13 - Representação gráfica do fluxo de trabalho do modelo em V conforme o             |

| andamento do projeto                                                                         |

| Figura 14 - Diagrama básico do BMS constituído dos módulos AFE, MCU e demais                 |

| periféricos44                                                                                |

| Figura 15 – Diagrama da entrada de tensão do BMS posicionado entre os polos de cada célula   |

| de bateria para levantamento de parâmetros e proteção dos componentes                        |

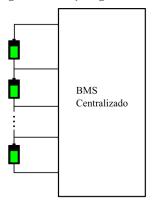

| Figura 16 – Representação gráfica da topologia de BMS de sistema centralizado47              |

| Figura 17 – Representação gráfica da topologia de BMS de sistema modular 47                  |

| Figura 18 - Representação gráfica do fluxo de trabalho do modelo em V conforme o           |

|--------------------------------------------------------------------------------------------|

| andamento do projeto com relação aos processos de validação                                |

| Figura 19 – Typhoon HIL modelo 404                                                         |

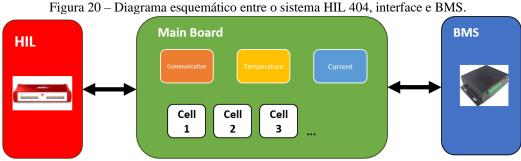

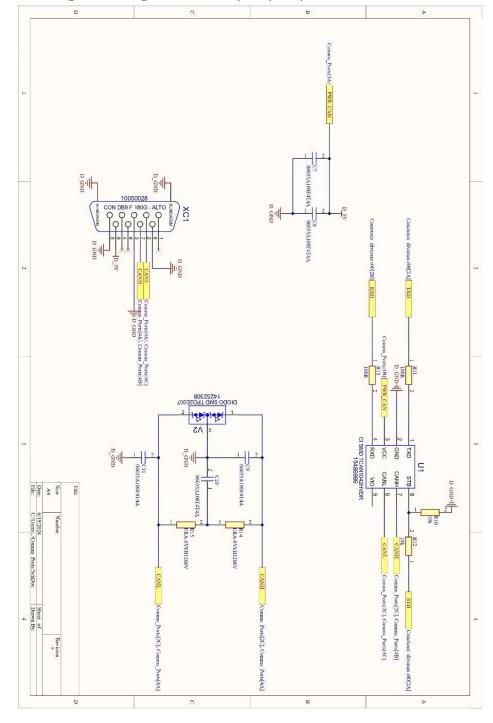

| Figura 20 – Diagrama esquemático entre o sistema HIL 404, interface e BMS55                |

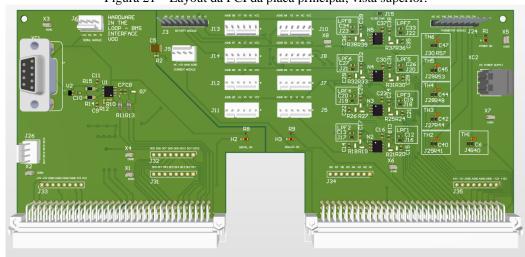

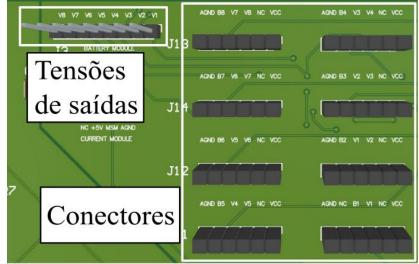

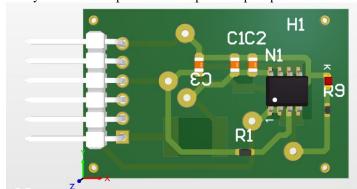

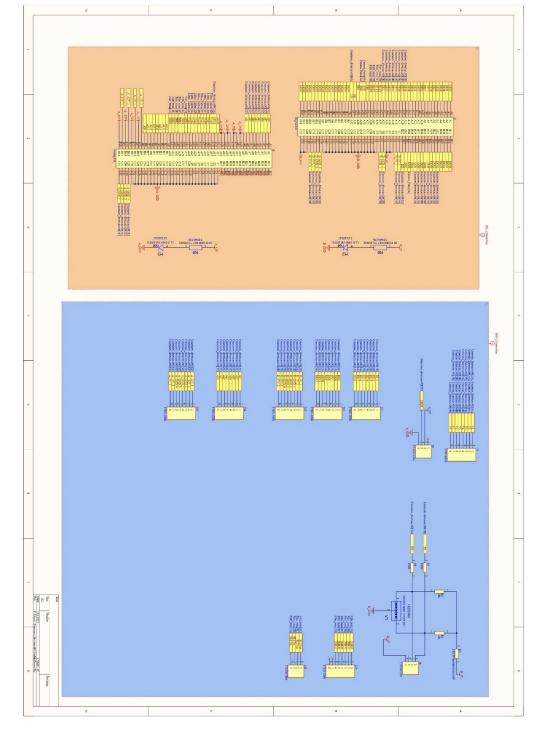

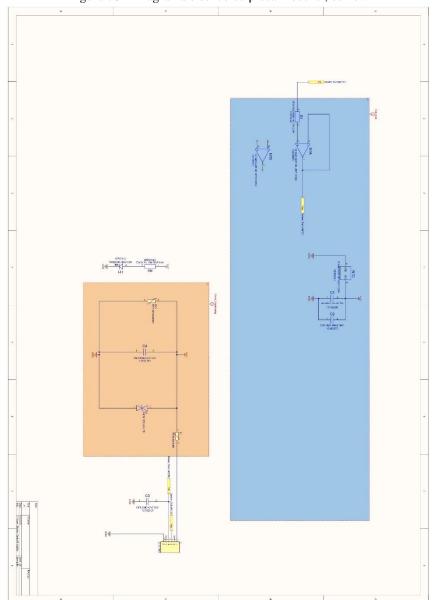

| Figura 21 – Layout da PCI da placa principal, vista superior                               |

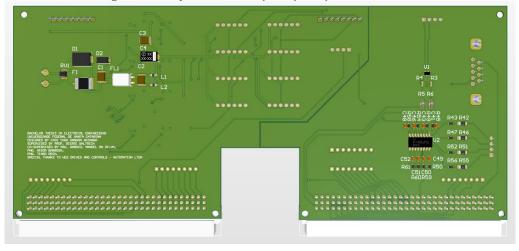

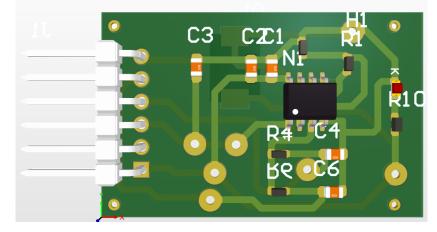

| Figura 22 – Layout da PCI da placa principal, vista inferior                               |

| Figura $23$ – Amostra de componentes PTH, à esquerda, e SMD, à direita, soldados em PCI de |

| FR-460                                                                                     |

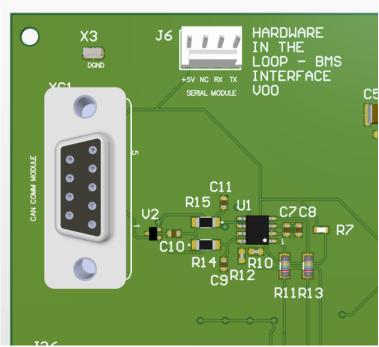

| Figura 24 - Conector para conexão serial em BMS. Pinos necessários para compor o           |

| protocolo de comunicação na camada física61                                                |

| Figura 25 - Conector para conexão CAN em BMS. Pinos necessários para compor o              |

| protocolo de comunicação na camada física                                                  |

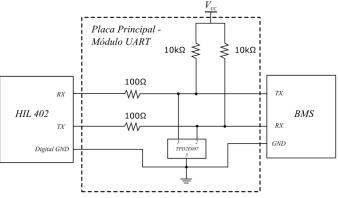

| Figura 26 – Diagrama esquemático do circuito elétrico de comunicação serial, vias TX e RX, |

| projetado na interface HIL-BMS                                                             |

| Figura 27 – Esquema de módulos CAN para estabelecer rede CAN em barramento                 |

| compartilhado. 64                                                                          |

| Figura 28 – Layout da PCI da placa principal do módulo de comunicação CAN64                |

| Figura 29 – Layout da PCI da placa principal com destaque ao lado analógico e digital      |

| definido pelo conector do HIL 404                                                          |

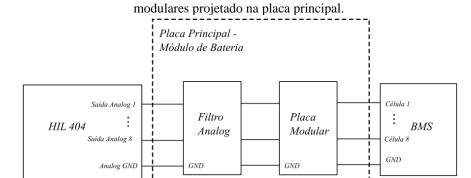

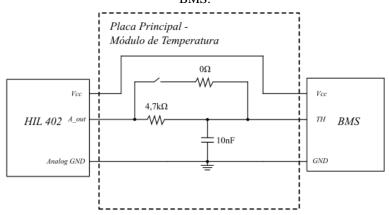

| Figura 30 – Diagrama esquemático do módulo de baterias com filtragem analógica e a         |

| inserção das placas modulares projetado na placa principal66                               |

|                                                                                            |

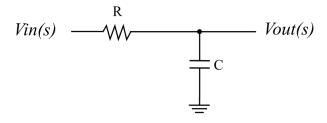

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

|                                                                                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

| Figura 31 – Esquema elétrico do filtro RC passa-baixa analógico                            |

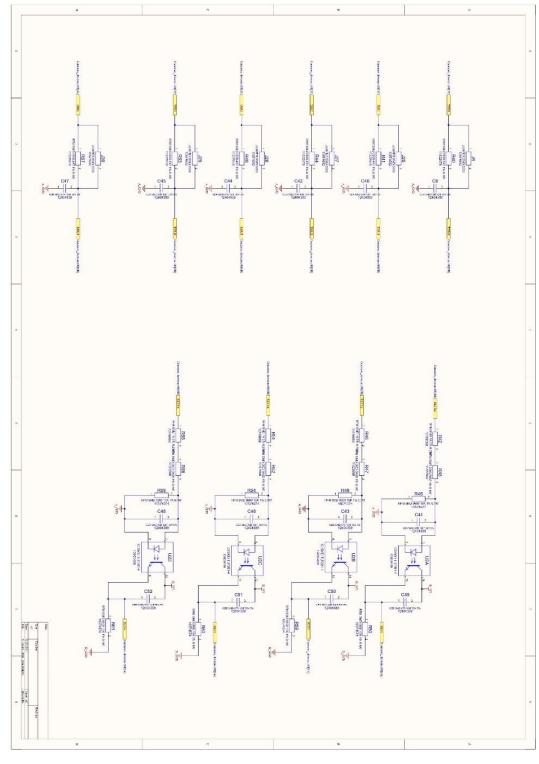

| Figura 40 - Diagrama esquemático do circuito elétrico do módulo de tensão para simulação      |

|-----------------------------------------------------------------------------------------------|

| de células de baterias em série com placas modulares projetado na interface HIL-BMS77         |

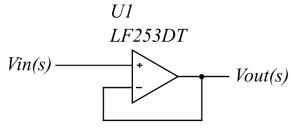

| Figura 41 – Esquema elétrico do seguidor de tensão, buffer, com amplificador operacional77    |

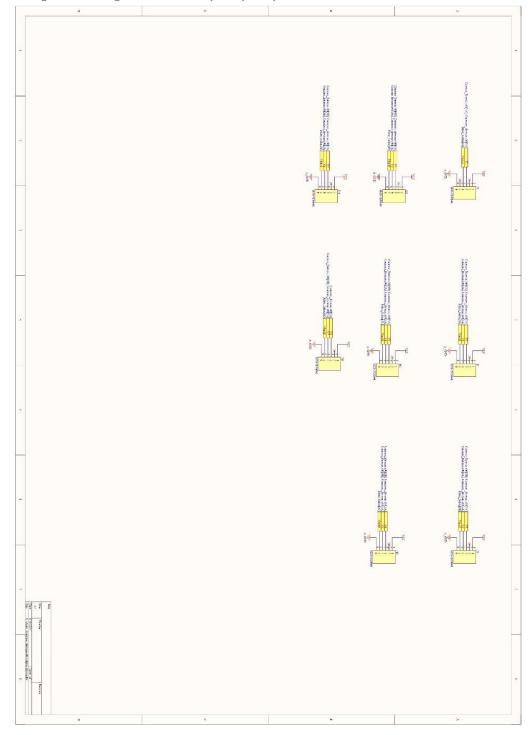

| Figura 42 – Layout da PCI da placa modular primária para primeira célula de bateria78         |

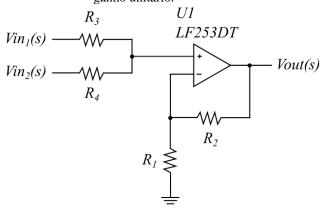

| Figura 43 – Esquema elétrico do somador de tensão com amplificador operacional para soma      |

| de duas tensões e ganho unitário                                                              |

| Figura 44 – Layout da PCI da placa modular somadora para demais células de bateria79          |

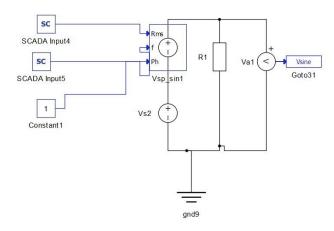

| Figura 45 – Circuito elétrico e lógica de sinais digitais para integração com o sistema SCADA |

| do HIL 404                                                                                    |

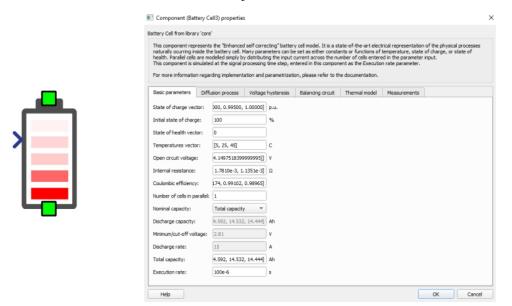

| Figura 46 - Componente da célula de bateria do editor de esquemático do Typhoon HIL           |

| Control Center. À esquerda, a representação visual do componente, à direita, a janela de      |

| configuração de acordo com o modelo desejado                                                  |

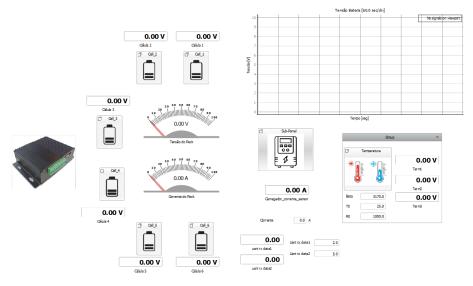

| Figura 47 – Painel de controle para simulação de baterias                                     |

| Figura 48 – Janela para configuração individual de cada célula de bateria                     |

| Figura 49 - Janelas para configuração de tensões de saída do HIL 404 de acordo com o tipo     |

| de sinal, analógico (esquerda) e digital (direita)                                            |

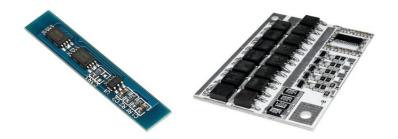

| Figura 50 - BMS comerciais testados com a interface HIL-BMS. À esquerda, FDC-2S-02, à         |

| direita, a placa BMS de 12 V84                                                                |

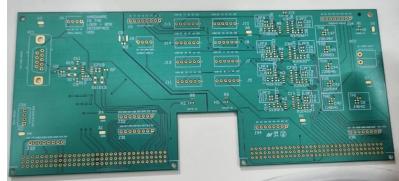

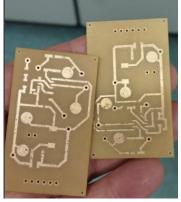

| Figura 51 – PCI sem componentes da placa principal projetada e discutida na seção 3.185       |

| Figura 52 – PCI sem componentes das placas modulares projetadas e discutidas na seção 3.2.    |

| 86                                                                                            |

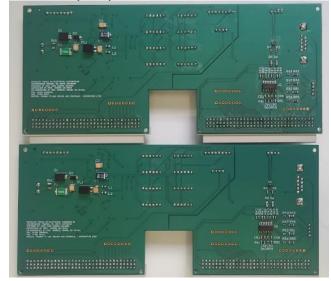

| Figura 53- Placa principal montada em PCI, vista da camada de cima                            |

| Figura 54 – Placa principal montada em PCI, vista da camada debaixo                           |

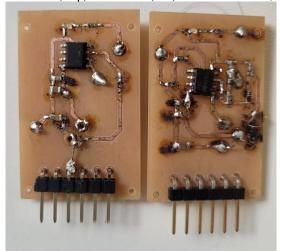

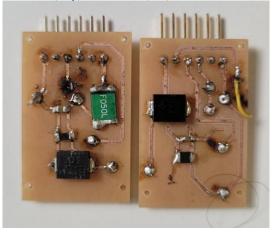

| Figura 55 – Placas modular buffer (esq.) e somador (dir.) montada em PCI, vista da camada     |

| de cima                                                                                       |

| Figura 56 - Placas modular buffer (esq.) e somador (dir.) montada em PCI, vista da camada     |

| debaixo.                                                                                      |

| Figura 57 – Placa principal conectada ao HIL 404.                                             |

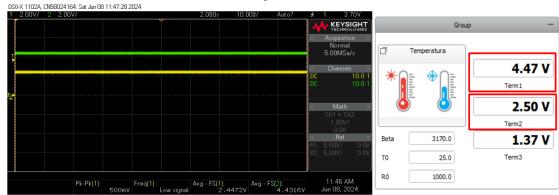

| Figura 58 – Teste do módulo de temperatura. À esquerda, tensões no osciloscópio extraídas     |

| dos pinos 1, em verde, e 2, em amarelo. À direita, o módulo de temperatura no SCADA           |

| indicando a tensão fornecida ao módulo de temperatura físico90                                |

|                                                                                               |

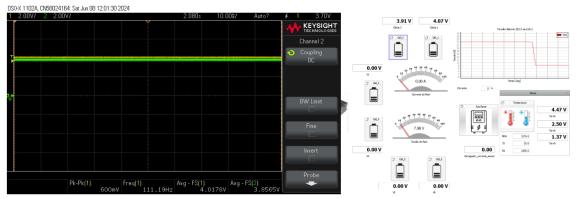

| Figura 59 - Teste do módulo de tensão de células de bateria sem elevação de tensão. À         |

|-----------------------------------------------------------------------------------------------|

| esquerda, tensões no extraídas dos pinos 1, em amarelo, e 2, em verde. À direita, o módulo no |

| SCADA indicando a tensão fornecida90                                                          |

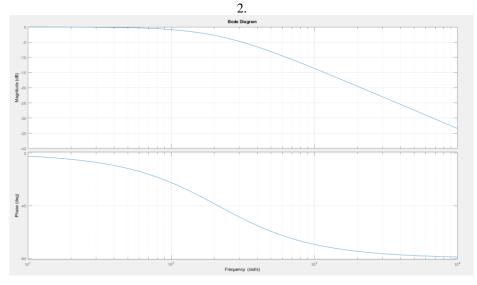

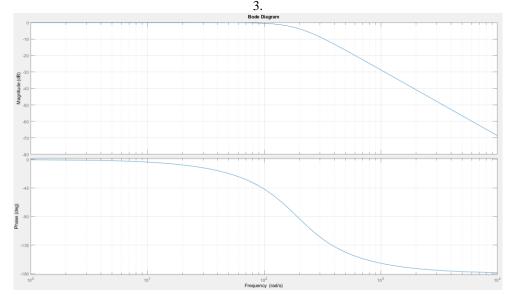

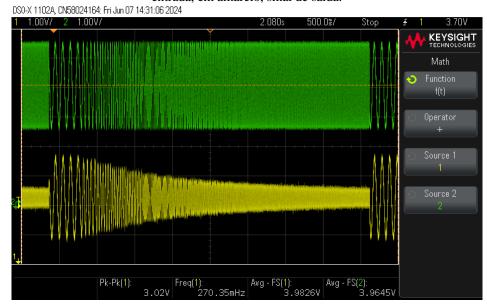

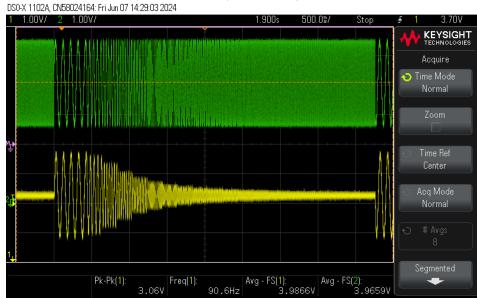

| Figura 60 – Teste do filtro passivo RC passa-baixa com gerador de varredura senoidal. Em      |

| verde, sinal de entrada, em amarelo, sinal de saída91                                         |

| Figura 61 – Teste do filtro ativo Butterworth Sallen-Key passa-baixa com gerador de           |

| varredura senoidal. Em verde, sinal de entrada, em amarelo, sinal de saída92                  |

| Figura 62 – Comparação dos filtros com gerador de varredura senoidal. Em amarelo, sinal de    |

| saída do filtro ativo Butterworth Sallen-Key passa-baixa, em verde, sinal de saída do filtro  |

| passivo RC passa-baixa92                                                                      |

| Figura 63 – Placas modulares acopladas à placa principal e conectadas ao HIL 40493            |

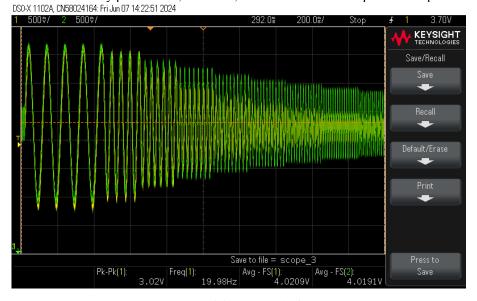

| Figura 64 – Teste do módulo de tensão de células de bateria com elevação de tensão. À         |

| esquerda, tensões no extraídas dos pinos 1, em amarelo, e 2, em verde. À direita, o módulo no |

| SCADA indicando a tensão fornecida                                                            |

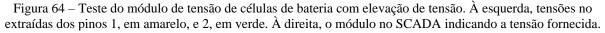

| Figura 65 – Teste do módulo de tensão de células de bateria com elevação de tensão            |

| descarregadas. À esquerda, tensão da célula 1, em amarelo, tensão da célula 2, em verde. À    |

| direita, o módulo no SCADA com as informações expostas                                        |

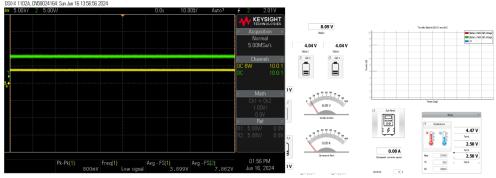

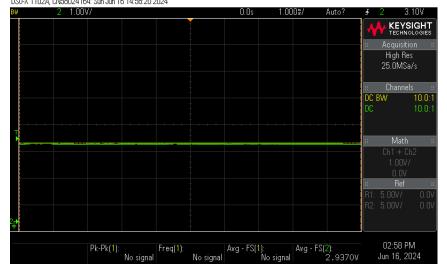

| Figura 66 - Teste em BMS FDC-2S-02, tensão de sobre-tensão aplicada, sinal do gate do         |

| MOSFET da placa95                                                                             |

| Figura 67 – Teste em BMS FDC-2S-02, tensão de 3V aplicada, sinal do gate do MOSFET da         |

| placa95                                                                                       |

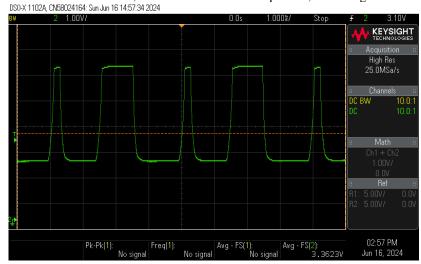

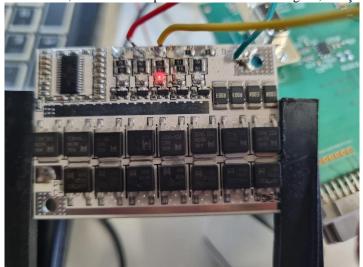

| Figura 68 – Teste em BMS 12 V, tensão de 5V aplicada. BMS com LED ligada, atuação de          |

| proteção ligada96                                                                             |

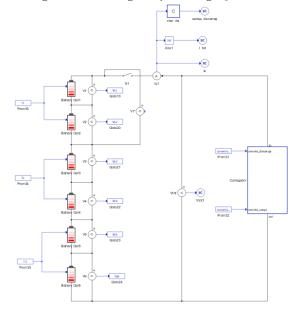

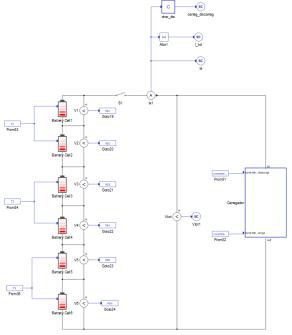

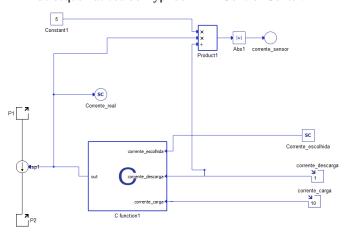

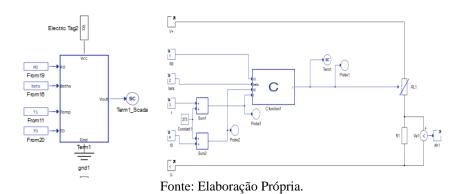

| Figura 69 – Diagrama de circuito de células de bateria em série controlados por fonte de      |

| corrente ajustável no subsistema "Carregador" realizado no editor de esquemáticos do          |

| Typhoon HIL Control Center                                                                    |

| Figura 70 – Diagrama do subsistema "Carregador" utilizado com células de bateria em série     |

| realizado no editor de esquemáticos do Typhoon HIL Control Center102                          |

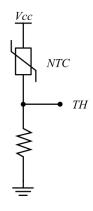

| Figura 71 – Diagrama do bloco do termistor (esq.) e do subsistema (dir.) para modelagem da    |

| Eq. (37) no editor de esquemáticos do Typhoon HIL Control Center                              |

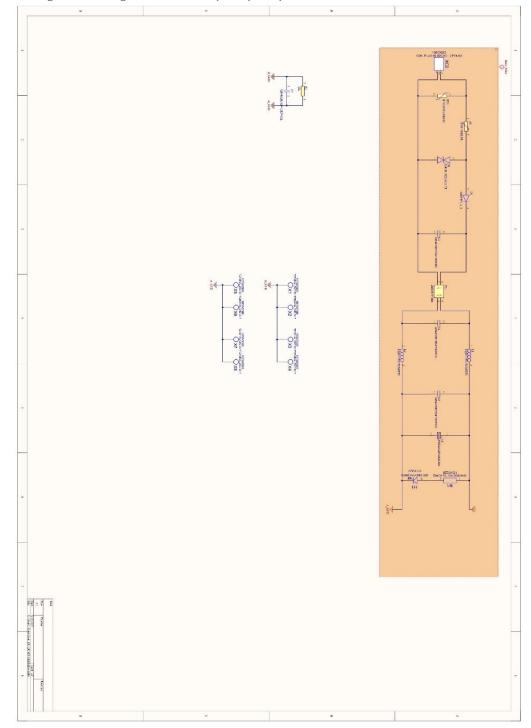

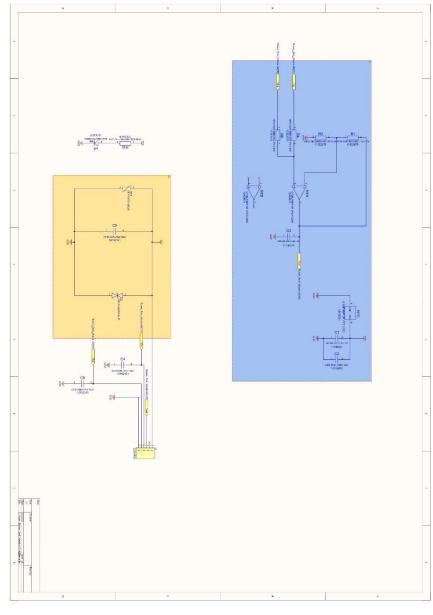

| Figura 72 – Diagrama elétrico da placa principal, módulo de entrada de tensão, folha 1 104    |

| Figura 73 – Diagrama elétrico da placa principal, entradas e saídas com BMS e HIL 404,        |

| folha 2105                                                                                    |

| Figura 74 – Diagrama elétrico da placa principal, filtro analógico do módulo de temperatura   | a e |

|-----------------------------------------------------------------------------------------------|-----|

| módulo de relés (não sucedido), folha 3.                                                      | 06  |

| Figura 75 – Diagrama elétrico da placa principal, conectores do módulo baterias, folha 41     | 07  |

| Figura 76 – Diagrama elétrico da placa principal, módulo CAN, folha 5                         | 08  |

| Figura 77 – Diagrama elétrico da placa principal, filtro analógico do módulo de baterias, fol | ha  |

| 6                                                                                             | 09  |

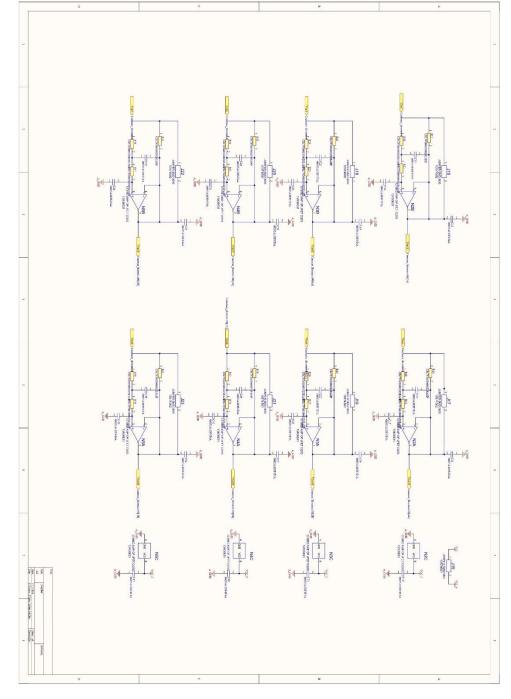

| Figura 78 – Diagrama elétrico da placa modular, buffer                                        | 10  |

| Figura 79 – Diagrama elétrico da placa modular, somador                                       | 11  |

| Figura 80 – Diagrama elétrico para varredura de frequência no Schematic Editor1               | 12  |

| Figura 81 – Widget para varredura de frequência no SCADA                                      | 12  |

|                                                                                               |     |

## LISTA DE QUADROS

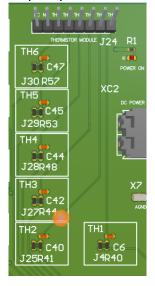

| Quadro 1 – Descrição dos pinos dos conectores do módulo de tensão de baterias72 |  |  |  |

|---------------------------------------------------------------------------------|--|--|--|

|                                                                                 |  |  |  |

|                                                                                 |  |  |  |

|                                                                                 |  |  |  |

|                                                                                 |  |  |  |

|                                                                                 |  |  |  |

|                                                                                 |  |  |  |

## LISTA DE TABELAS

| Tabela 1- Número de elétrons por subnível de orbital quântico                                   |

|-------------------------------------------------------------------------------------------------|

| Tabela 2 - Parâmetros para confecção de filtro RC passa-baixa para frequência de corte de       |

| 33,86 Hz68                                                                                      |

| Tabela 3 - Parâmetros para confecção de filtro RC passa-baixa para frequência de corte de       |

| 30,12 Hz70                                                                                      |

| Tabela 4 – Teste do módulo de temperatura. À direita, tensões nos pinos da placa principal. À   |

| direita, tensões do módulo de temperatura nas saídas do HIL90                                   |

| Tabela 5 – Teste do módulo de tensão de células de bateria sem elevação de tensão. À direita,   |

| tensões nos pinos da placa principal. À direita, tensões do módulo de bateria nas saídas do     |

| HIL91                                                                                           |

| Tabela 6 - Teste do módulo de tensão de células de bateria com elevação de tensão               |

| carregadas. À direita, tensões nos pinos da placa principal. À direita, tensões do módulo de    |

| bateria nas saídas do HIL                                                                       |

| Tabela 7 - Teste do módulo de tensão de células de bateria com elevação de tensão               |

| descarregadas. À direita, tensões nos pinos da placa principal. À direita, tensões do módulo de |

| bateria nas saídas do HIL94                                                                     |

#### LISTA DE ABREVIATURAS E SIGLAS

BMS – Battery Management System

EV – Electric Vehicle

HIL – *Hardware-in-the-loop*

TVS – Transient Voltage Supressor

TCC - Trabalho de Conclusão de Curso

SoC – *State of Charge*

OCV - Open Circuit Voltage

SoH – State of Health

DoD – Depth of Discharge

IEC – International Electrotechnical Commission

TTL-Transistor-Transistor-Logic

SMD – Surface-Mount Device

PTH – Pin Through-Hole

CAN – Controller Area Network

UART – Universal Asychronous Receiver/Transmitter

BESS – Battery Energy Storage System

NTC – Negative Temperature Coeficient

UPS – *Uninterruptible Power Supply*

SIL – Safety Integrity Level

PCI – Placa de Circuito Impresso

NR – Norma Regulamentadora

SCADA - Supervisory Control and Data Acquisition

ABNT – Associação Brasileira de Normas e Técnicas

# SUMÁRIO

| 1       | Introdução                                             | 17 |

|---------|--------------------------------------------------------|----|

| 1.1     | Objetivos                                              | 18 |

| 1.1.1   | Objetivo Geral                                         | 18 |

| 1.1.2   | Objetivos Específicos                                  | 18 |

| 2       | Fundamentação Teórica                                  | 20 |

| 2.1     | Células de Bateria                                     | 21 |

| 2.1.1   | Modelo e aspectos contrutivos                          | 22 |

| 2.1.2   | Modelos Células de Bateria                             | 28 |

| 2.1.2.1 | Estado de Carga (SoC) e Profundidade de Descarga (DoD) | 29 |

| 2.1.2.2 | Estado de Saúde                                        | 31 |

| 2.1.3   | Modelo de Tensão de Circuito Aberto (OCV)              | 31 |

| 2.1.4   | Modelo de Tensão de Circuito Aberto (OCV) Variável     | 32 |

| 2.1.5   | Modelo Resistência Série Equivalente, "Rint"           | 34 |

| 2.1.6   | Modelo da Tensão na Célula por Thévenin                | 36 |

| 2.1.7   | Circuito de Randles e Modelo Impedância de Warburg     | 38 |

| 2.2     | Método de desenvolvimento em "V" e teste de produtos   | 40 |

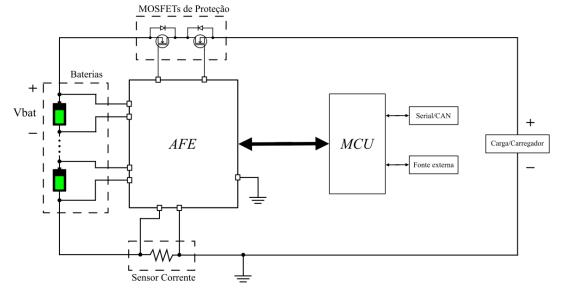

| 2.3     | Battery management system (BMS)                        | 42 |

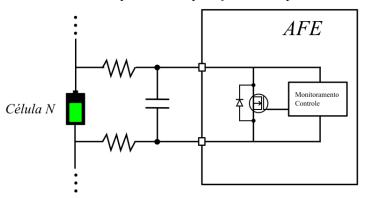

| 2.3.1   | Sistema de Proteção do BMS                             | 45 |

| 2.3.2   | Balanceamento de Células                               | 45 |

| 2.3.3   | Topologias de BMS                                      | 46 |

| 2.4     | Normas aplicáveis                                      | 48 |

| 2.4.1   | Controle de sobrecarga da tensão                       | 49 |

| 2.4.2   | Controle de sobrecarga da corrente                     | 49 |

| 2.4.3   | Controle de sobreaquecimento                           | 49 |

| 2.5     | Hardware-in-the-loop                                   | 50 |

| 2.5.1   | Typhoon HIL 404                                               | 52        |

|---------|---------------------------------------------------------------|-----------|

| 3       | Desenvolvimento                                               | 54        |

| 3.1     | Projeto da placa principal: interface entre hardwares         | 57        |

| 3.1.1   | Confecção das Placas de Circuito Impresso                     | 59        |

| 3.1.2   | Módulo de Comunicação serial UART                             | 60        |

| 3.1.3   | Módulos de Transmissão de Tensões de Estado                   | 65        |

| 3.1.3.1 | Projeto de Filtros Analógicos                                 | 66        |

| 3.1.3.2 | Módulo de Bateria                                             | 71        |

| 3.1.3.3 | Módulo de Temperatura                                         | 73        |

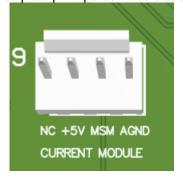

| 3.1.3.4 | Módulo de Corrente                                            | 75        |

| 3.2     | Projeto Placa Modular: Módulos de Tensão de Baterias em Série | 76        |

| 3.3     | Software Typhoon HIL Control Center                           | 79        |

| 3.4     | Teste com BMS                                                 | 84        |

| 4       | Resultados                                                    | 85        |

| 4.1     | Resultados Preliminares                                       | 85        |

| 4.1.1   | Placa Principal                                               | 86        |

| 4.1.2   | Placas Modulares                                              | 87        |

| 4.2     | Resultados Definitivos                                        | 88        |

| 5       | CONCLUSÃO                                                     | 96        |

|         | REFERÊNCIAS                                                   | 98        |

|         | APÊNDICE A – Detalhamento sobre os Módulos Elétricos do l     | Editor de |

|         | Esquemáticos                                                  | 102       |

|         | APÊNDICE B – Esquemas Elétricos da Placa Principal            | 103       |

|         | APÊNDICE C – Esquemas Elétricos das Placas Modulares          | 110       |

|         | APÊNDICE D – Código do programa                               | 111       |

## 1 INTRODUÇÃO

Desde o fim do século passado, a questão da emissão de gases do efeito estufa e sua relação com o alarmante aumento das médias de temperatura global tem sido enfatizada por diversos órgãos internacionais (EKWURZEL, 2017). A atual matriz energética global é majoritariamente centrada no consumo de combustíveis fósseis, cerca de 70% em 2022 (INTERNATIONAL ENERGY AGENCY, 2023), e deve sofrer uma drástica mudança para que os impactos ambientais sejam reduzidos.

Para atender essas exigências, a demanda global por soluções energéticas provindas de fontes alternativas dominou o ramo do desenvolvimento científico da engenharia elétrica. Logo, uma das linhas de pesquisa mais proeminentes é o desenvolvimento de tecnologias relacionadas a mobilidade pela eletrificação de veículos automotores (CLEMENTNYS; HAESEN; DRIESEN, 2010), sistemas eficientes de geração de energia *off-grid* fotovoltaicos (SUBUDHI; PRADHAN, 2013), entre outros métodos energéticos visando a diminuição de emissão de carbono (KOURO et al, 2015).

Nos anos recentes, o avanço nos estudos em carros elétricos (EVs), e no ramo da eletrônica de potência no geral, tem possibilitado maior acessibilidade a essas tecnologias para os cidadãos comuns, além de reduzir as taxas de emissão de carbono (INTERNATIONAL ENERGY AGENCY, 2023). Esses veículos, assim como diversas outras aplicações energéticas, dependem de bancos de baterias como fonte de energia móvel, garantindo a autonomia necessária para suas funções designadas.

Para tanto, os bancos de baterias modernos são acompanhados de sistemas de controle, BMS, que gerenciam e monitoram o estado das células de bateria conforme a necessidade e para garantir a eficiência energética.

O BMS de um banco de baterias é de suma importância para a vida útil de uma bateria, uma vez que, fatores como temperatura e picos de corrente degradam o estado de saúde das baterias e, consequentemente, reduzem o tempo de funcionamento (HAN et al., 2019).

A degradação de baterias é um iminente problema do ponto de vista ambiental e econômico, uma vez que desses dispositivos é contaminante ao solo e mananciais. Ainda, o banco de baterias para EVs são componentes de alto custo e, consequentemente, devem ter uma longa vida útil.

Portanto, com a problemática exposta, o desenvolvimento de diferentes BMSs está popularizando-se nas áreas do conhecimento científico e industrial e a demanda por sistemas complexos, baratos e eficientes torna-se cada vez maior. Além disso, como os bancos de bateria são componentes de alto valor monetário se comparados ao BMS, esses materiais tornam-se um grande gargalo no desenvolvimento desses dispositivos de controle.

A dinâmica do desenvolvimento tecnológico deve acompanhar o imediatismo por produtos cada vez mais eficientes. Faz-se necessário novas metodologias para acelerar esses processos produtivos tais como o desenvolvimento em V. Além disso, com a utilização de hardwares para emulação de módulos elétricos, houve uma grande revolução no desenvolvimento da engenharia.

#### 1.1 OBJETIVOS

Visando um melhor entendimento das metas do trabalho proposto neste TCC, decidiu-se dividir em duas subcategorias dispostas nos tópicos sequentes. Deve-se observar, no entanto, que os objetivos não necessariamente serão cumpridos à risca, mas devem ser entendidos como um patamar a ser atingido durante o decorrer deste trabalho.

#### 1.1.1 Objetivo Geral

O objetivo principal do TCC a ser realizado é implementar um modelo de interface de teste e validação utilizando *Hardware-in-the-loop* (HIL) para sistemas de gerenciamento de baterias (BMS).

#### 1.1.2 Objetivos Específicos

Os objetivos específicos do TCC estão listados a seguir:

- Revisão teórica acerca de células de bateria e BMS;

- Projetar e simular modelos de células de baterias e BMS;

- Desenvolver um sistema de simulação baseado em HIL para teste do BMS;

- Desenvolver uma interface física entre BMS e hardware de simulação;

• Implementação, teste e validação do modelo proposto via HIL com o software *Typhoon HIL*.

## 2 FUNDAMENTAÇÃO TEÓRICA

Nesta seção serão discutidos os princípios teóricos para o desenvolvimento deste trabalho. Serão apresentados os conceitos de células de bateria, do sistema de gerenciamento de baterias e dos fundamentos eletromagnéticos e eletroquímicos necessários para fundamentar todos os aspectos construtivos deste TCC.

A importância de dispositivos armazenadores de energia resume-se na própria existência da sociedade moderna (CLEMENTS, 2019). A capacidade de estocar energia eletroquímica para conversão em energia elétrica, é vital para todos os dispositivos eletrônicos móveis sem conexão com uma fonte elétrica externa. A tendência é que o assunto ocupe cada vez mais importância no futuro devido aos avanços das tecnologias de materiais e da eficiência de sistemas de controle para atender à crescente demanda de componentes com maior densidade energética.

Embora essenciais para dispositivos móveis, baterias ainda requerem melhorias de robustez e *performance*. Não obstante, a área da eletrônica de potência também possui alta demanda em sistemas armazenadores de energia (JARBRATT et al., 2023). Nesse caso, busca-se estratégias que favoreçam sistemas energéticos cada vez mais eficientes e materiais com características com maior densidade energética, uma vez que a necessidade de estratégias de geração elétrica *off-grid* e de veículos elétricos popularizam-se a cada ano e devem se tornar mais atrativos, economicamente e ecologicamente, ao mercado consumidor global.

Segundo o Parlamento Europeu (2023), a comissão europeia fez o comprometimento do encerramento da venda de carros movidos à combustão até 2035. Portanto, somente veículos elétricos deverão ser comercializados em território dos países integrantes da União Europeia conforme anúncio público durante o encontro da 27ª Conferência das Partes da UNFCCC (COP27). A frota veicular dos países integrantes da União Europeia deve sofrer uma abrupta mudança no perfil da mobilidade urbana e deve preparar a necessária infraestrutura para que esse audacioso plano funcione adequadamente.

Concomitantemente, não somente restrito a países do bloco europeu, deve-se esperar incentivos fiscais tais como redução de imposto de industrialização e importação de componentes, oferta de crédito financeiro e amortização acelerada que irão baratear os custos de fabricação dessa futura demanda e, consequentemente, os produtos devem cair de preço ao consumidor final. Desse modo, considerando iniciativas e comprometimentos dessa natureza além do necessário preparo do contexto infraestrutural a fim de suportar essa demanda, o

avanço tecnológico também deve acompanhar esse ritmo acelerado com propostas inovadoras e responsáveis seguindo a tendência global em ações menos lesivas ao meio-ambiente e bemestar da população global.

Atualmente, um dos ramos do desenvolvimento tecnológico em baterias está centrado na compreensão e reprodução do comportamento fidedigno descritos em modelos teóricos em simulações computacionais. No entanto, deve-se notar que o uso de *softwares* é apenas uma ferramenta para auxiliar o indivíduo e não deve substituir o pleno entendimento realização prática sobre o assunto. Em muitos casos, as simulações são realizadas em ambientes controlados, que desconsideram os efeitos não-ideias resultando em situações intangíveis na realidade.

O discernimento de forma a distinguir entre possíveis alarmes-falsos e verdadeiros avanços na área depende do conhecimento sobre o assunto. Dessa forma, neste documento serão expostos e explicados com certo nível de complexidade os principais conceitos associados a baterias abordando os diferentes modelos teóricos, parametrização de estados e uma pincelada sobre a estimação de parâmetros acerca do estado delas.

Ressalta-se que o desenvolvimento tecnológico também é acompanhado pela inovação dos equipamentos e pelo aprofundamento no entendimento dos fenômenos físicos da natureza. Um dos novos processos que compõem o desenvolvimento de produto é o método do HIL (TUMASOV et al., 2019; LI et al., 2022), no qual reproduz comportamentos de módulos ou componentes sem a necessidade de tê-los fisicamente. Neste TCC, discorrer-se-á brevemente sobre o modelo HIL 404 projetado e manufaturado pela empresa americana Typhoon HIL que é o dispositivo utilizado no decorrer do projeto.

Adicionalmente, devido a sua importância para a indústria, discute-se acerca do modelo de desenvolvimento em V que acomoda a metodologia do HIL no desenvolvimento de produtos. Durante o processo de desenvolvimento de um equipamento, o escopo do projeto deve considerar a segurança, padrões energéticos e ambientais estabelecidos pelo órgão certificador do país em que irá ser usado.

#### 2.1 CÉLULAS DE BATERIA

A bateria é um componente fundamental à revolução energética contemporânea (THE EVOLUTION OF ENERGY STORAGE SYSTEMS). Ela é um dispositivo que possibilita a conversão de energia química em energia elétrica a partir de células

eletroquímicas que servem como fonte energética a dispositivos eletroeletrônicos. Tais dispositivos armazenadores de energia elétrica são essenciais para as aplicações da modernidade pois atendem às necessidades cotidianas tais como mobilidade e portabilidade de variadas aplicações tornando-se um recurso intrínseco e essencial a maioria das atividades tecnológicas. O encapsulamento da energia elétrica em compactos recipientes possibilitou à humanidade imprimir um ritmo acelerado na vida e trouxe comodidade nas tarefas diárias.

Toma-se, por exemplo, o celular cuja bateria possui dimensões diminutas se comparado a mecânica externa do aparelho e deve reter energia em forma de potencial eletroquímico para uso contínuo por várias horas seguidas. O celular, assim como diversos aparelhos munidos de baterias, é uma ferramenta que dinamizou todas as relações humanas. Portanto, na palma da mão, o portador do tele móvel tem acesso ao escritório de trabalho, a conta bancária, a televisão, entre outros.

Historicamente, as primeiras baterias criadas são datadas do século 16 com a invenção da Pilha de Daniel (ATKINS; JONES, 2011, p. 523), na Itália, e da bateria de Leclanché, na França (COMMERCIAL GALVANIC CELLS, 2023). Esses dispositivos eram constituídos de placas metálicas de cobre e latão intercaladas e submersas em solução ácida. A conexão desse dispositivo a uma lâmpada, por exemplo, gerava luz a partir da conversão eletroquímica. Este foi um dos grandes avanços que originaram a descobertas e fascinação nessa área da elétrica devido ao seu alto valor tecnológico. Além de que a disponibilidade de recursos a época garantia a repetibilidade para produção em escala.

Nesta seção, portanto, devido ao impacto do tema para esse documento, dever-se-á expor em linhas gerais o funcionamento químico por detrás das baterias, quais os tipos de modelos teóricos que a célula pode ser interpretada, os principais parâmetros de uma bateria e, por fim, sobre a estimação desses estados do material a partir de medições anteriores. É possível predizer valiosas informações sobre a saúde da bateria apenas com valores amostrados no tempo de uso.

#### 2.1.1 Modelo e aspectos contrutivos

Primeiramente, deve-se entender que baterias são constituídas de dois terminais, um positivo (cátodo) e um negativo (ânodo), nomeados referentes ao potencial elétrico disponível em cada um deles. Ao conectar os terminais a um circuito externo constituído de um condutor elétrico, a partir do ânodo, os elétrons provenientes do processo de conversão química fluem

até o cátodo fornecendo um fluxo de cargas elétricas, conhecida como corrente elétrica. A origem desse fluxo de elétrons é dada pelo fenômeno da oxirredução, reação físico-química caracterizada pela transferência de elétrons entre duas espécies elementares.

A Figura 1 mostra uma foto de uma pilha D, um tipo de bateria amplamente utilizado em dispositivos portáteis de baixa potência. Observa-se que os terminais do componente são, geralmente, diferenciados por algum tipo de sinalização escrita, faixa de coloração ou formato de terminal. Geralmente, o terminal positivo é destacado com uma protuberância metálica, sinalização e/ou faixa de cor.

Figura 1- Pilha tipo D, espécie de bateria. Terminal positivo em destaque por cor, escrita e mecânica.

Fonte: Ryan, V. 2020.

A reação de oxirredução (ATKINS; JONES, 2011, p. 515–522), ou simplesmente redox, é um processo químico no qual um reagente sofre a oxidação química. Neste processo, o material oxidado, o cátion, perde elétrons de sua estrutura eletrônica, e o outro reagente sofre a redução química, o ânion, que recebe estes elétrons livres provenientes do elemento oxidado. No decorrer do processo, os reagentes encontram-se na forma de íons livre e se ligam quimicamente, combinados por ligações iônicas, para formar um composto estável, conforme dita a regra do octeto.

É importante salientar que esse fenômeno ocorre concomitantemente, ou seja, ambos os reagentes estão oxidando e reduzindo ao mesmo tempo. Os eletrodos que são oxidados ou reduzidos não necessariamente necessitam estar espacialmente juntos, aparelhos tais como pilhas possuem uma a película separadora porosa composta de um material polimérico que permite o transporte de íons entre os terminais mantendo a ocorrência da reação até o esgotamento dos reagentes.

Na estrutura molecular da matéria, segundo o princípio de Aufbau (PAULING, 1988), os elementos químicos preferenciam os menores estados energéticos para garantir a maior estabilidade, em outras palavras, corpos inseridos na natureza buscam configurações

menos ativas de forma a obter o estado mais estável possível. Ainda, considerando a moderna definição do orbital atômico, onde devido a interação do núcleo do átomo e dos elétrons somando o comportamento ondulatório dos elétrons, haverá definidas regiões ao redor do núcleo atômico de alta densidade probabilística da posição do elétron. Cada região é categorizada em camada, chamado de número quântico principal que varia de 1 a 7, e subnível, chamado também de número quântico secundário que pode conter os orbitais tipo s, p, d e f. Cada subnível pode assumir números diferentes de simetrias, 1, 3, 5 e 7, respectivamente, dependendo dos lóbulos disponíveis em cada tipo de orbital. A Figura 2 demonstra todas as simetrias de cada tipo de orbital.

Figura 2 – Esquemático da configuração dos orbitais tipo s, p, d e f de cima para baixo.

Fonte: UCDavis Chemwiki,

Portanto, considerando o princípio de exclusão de Pauli onde se concluiu que o número de elétrons em cada orbital pode ser até de dois, os tipos de orbitais podem conter no máximo um número definido de elétrons, descriminados na Tabela 1.

Tabela 1- Número de elétrons por subnível de orbital quântico

| Subnível | Número de elétrons por subnível |

|----------|---------------------------------|

| S        | 2 elétrons                      |

| p        | <b>6</b> elétrons               |

| d        | 10 elétrons                     |

| f        | 14 elétrons                     |

Fonte: Elaboração Própria.

Logo, com o auxílio do diagrama de Linus Pauling (JEWETT; SERWAY, 2013), na Figura 3, e com a lógica da estabilidade do átomo, a configuração eletrônica de cada átomo pode ser estatisticamente descrita. Além disso, é possível entender que, devido a geometria dos orbitais, a estabilidade entre configurações eletrônicas prefere estados com números de elétrons completos na camada mais externa, chamada de camada de valência do átomo, de sua configuração eletrônica. Isto é, o conjunto dos vetores de força eletrostática, entre elétrons e núcleo, que mantém o átomo estável formam uma rede robusta de modo que é mais difícil retirar um elétron desse sistema balanceado de cargas do que em configurações com as camadas incompletas. A esse fenômeno denomina-se de regra do octeto. Segundo Atkins e Jones (2011), a regra do octeto possui algumas exceções e, como no caso do lítio (Li) que é essencial na produção de baterias modernas, o elemento encontra-se com sua camada de valência completa com 2 elétrons na camada 1 e subnível s.

Assim, os átomos podem se ligar de três diferentes formas: ligações iônicas, ligações covalentes e ligação metálica. Na ligação iônica, os átomos ligam-se por meio da doação de elétrons entre íons, cátions e ânions, onde o ânion doa elétrons ao cátion para completar a camada de valência segundo a regra do octeto. Para que esse tipo de fenômeno ocorra, os elementos possuem tendências opostas: um possui capacidade de perder carga e o outro, de ganhar cargas. As baterias funcionam a partir de compostos iônicos para formar esse fluxo de cargas. Ligações covalentes são descritas detalhadamente pela teoria do orbital atômico. Contudo, como não tem relevância direta com o tema deste trabalho, segundo Ayala (2003), pode-se entendê-las como o compartilhamento de elétrons entre átomos a fim de completar sua camada de valência e garantir a estabilidade da molécula. Por fim, não menos importante, as ligações metálicas são compostas de ligas metálicas que apresentam características de boa condutibilidade elétrica e térmica.

Figura 3 – Diagrama de Linus Pauling. A seta vermelha indica a ordem da configuração eletrônica do átomo de acordo com o princípio de Aufbau.

Fonte: Passeidireto, 2015.

Portanto, dependendo das características químicas do material, a qualidade energética é afetada. Apesar de elementos possuírem tendência em perder ou doar mais de um elétron, não necessariamente são os materiais mais adequados para se utilizar em baterias. Há vários fatores que devem ser inseridos nessa análise. Os principais elementos utilizados em baterias são os elementos: lítio (Li), cádmio (Cd), chumbo (Pb), zinco (Zn), níquel (Ni) e prata (Ag). Cada metal combinado com seu íon correspondente irá formar um composto iônico com características únicas e benéficas dependendo da aplicação na integração de baterias. Ainda, a utilização de um eletrólito é peça fundamental nas baterias (KAINAT et al, 2024). O eletrólito, tanto líquido quanto em pasta, vai possibilitar que os íons sejam transferidos de um eletrodo a outro para que a reação de oxirredução ocorra. Não obstante, a utilização de outros compostos associados as baterias de forma a otimizar o seu funcionamento é comum, catalisadores de platina ou níquel aceleraram as reações químicas de compostos como oxigênio e hidrogênio.

O fornecimento de energia pela bateria ocorre em detrimento da quantidade dos reagentes remanescentes de qualquer eletrodo. Quando ocorre o consumo da bateria, a diferença de potencial entre os terminais diminui até que os potenciais elétricos se igualem. Há dois tipos de bateria: primária, onde o componente não é recarregável, e secundária, onde o componente é recarregável. Baterias recarregáveis além de apresentarem as capacidades das baterias primárias, podem ser conectadas a uma fonte de alimentação elétrica que, idealmente,

recupera às condições iniciais do componente antes do uso da carga. Ao se aplicar uma tensão igual a nominal da bateria, o eletrodo consumido é regenerado pelo processo reverso do descarregamento da componente. Já as baterias primárias devem ser descartadas após o esgotamento de sua carga. Baterias não possuem comportamento de carga e descarga linear, cada composto utilizado na constituição do componente irá apresentar uma curva característica. Além disso, há diversos parâmetros que devem ser considerados ao se estimar uma bateria tais como: estado de carga, estado de saúde, tensão dos terminais, tensão de circuito aberto, entre outros. Em alguns modelos teóricos, visando o exato perfil realístico da bateria, os parâmetros serão dependentes de vários outros fatores. Nas seções subsequentes, os principais modelos para o levantamento das características da bateria serão apontados detalhadamente.

Tipicamente, células de baterias não passam de 12 V por célula (MONOLITHIC POWER SYSTEMS, 2023) e, portanto, a ligação em série e paralelo é empregada para adequá-las a aplicação em que se destinam. A ligação em série consiste em conectar os polos opostos de células adjacentes para que a tensão final do conjunto seja a soma aritmética das tensões individuais das células ligadas entre si. A ligação em paralelo é utilizada para suprir demanda de potência e duração na aplicação pois se aumenta o limite de corrente e a carga elétrica disponível.

Um exemplo da utilização de uma configuração de células, ou até mesmo da combinação de módulos de baterias, são os UPS (do inglês *Uninterruptible Power System*, em tradução livre Sistema de Potência Ininterrupto), também conhecidos como Nobreaks. Esses aparelhos, ao detectar falta de fornecimento de energia, ativa um sistema completo com conversor, controlador e inversor de potência de modo a não interromper o fornecimento de energia aos aparelhos conectados a ele, que pode ser uma residência, fábrica ou escritório. Nesse caso, aplicações desse porte comumente necessitam de potências elevadas e, portanto, realisticamente, baterias de chumbo/ácido em ligadas em paralelo são utilizadas.

Para ilustrar o processo químico, analise-se o processo de oxirredução em baterias de chumbo/ácido como descritos no exemplo anterior. Esse tipo de bateria secundária é comumente encontrado em carros, caminhões e UPS devido ao seu moderado custo monetário, densidade energética e autodescarga. No interior dessas baterias, portanto, são encontrados o chumbo (Pb) metálico, no ânodo, dióxido de chumbo (PbO<sub>2</sub>), no cátodo, imersos em solução aquosa de ácido sulfúrico (H<sub>2</sub>SO<sub>4 (aq)</sub>). Deve-se recordar que ácidos em

soluções aquosas sofrem dissociação ácido-base e, logo, têm íons livres. Analisa-se a reação em cada um dos eletrodos.

No ânodo, ocorre o acúmulo de cargas negativas, 2 elétrons por reação, dando origem a um campo elétrico que irá fazer com que essas cargas fluam até o cátodo. Além disso, esse mesmo campo elétrico atrai os íons de hidrogênio e bloqueia os íons sulfato que aos poucos interrompe a reação necessitando do carregamento da bateria:

$$Pb(s) + HSO_{4}^{-}(aq) \to PbSO_{4}(s) + H^{+} + 2e^{-}$$

(1)

No cátodo, dióxido de chumbo auxilia a condutividade devido as propriedades elétricas, a reação é descrita como:

$$PbO_2(s) + HSO_4^-(aq) + 3H^+(aq) + 2e^- \rightarrow PbSO_4(s) + 2H_2O(l)$$

(2)

A reação global pode ser descrita como:

$$Pb(s) + 2H_2SO_4(aq) \rightarrow 2PbSO_4(s) + 2H_2O(l)$$

(3)

Quando a bateria está descarregada, ambos os eletrodos viram sulfato de chumbo II, PbSO<sub>4</sub>(s), e o ácido torna-se diluído devido a água gerada como produto da reação. Ao recarregarmos a bateria, os terminais são reconstituídos novamente e estão prontos para o reuso. Uma observação é que a sobrecarga no sistema de baterias, ou seja, a aplicação de uma tensão acima da nominal entre os terminais da bateria promoverá a eletrólise na água gerando gás de hidrogênio (H<sub>2</sub>(g)) e gás de oxigênio (O<sub>2</sub>(g)) e a perda de funcionalidade da bateria.

Portanto, entendendo-se os fundamentos físico-químicos que as células de bateria funcionam, é possível discorrer sobre o assunto sob o ponto de vista da aplicação desses dispositivos na área da engenharia elétrica.

#### 2.1.2 Modelos Células de Bateria

Após uma breve, no entanto, sólida introdução sob a ótica da eletroquímica no processo da eletrificação de compostos químicos imersos em soluções salinas, é possível promover o aprofundamento teórico da aplicação das células de bateria. Nessa seção,

portanto, discutir-se-ão quais os principais pontos da modelagem de células de baterias e quais suas vantagens à medida que se acrescenta complexidade ao modelo da bateria de forma a aproximar ao comportamento desses dispositivos na realidade.

Primeiramente, deve-se ratificar que o modelo teórico da célula de bateria é o meio de descrever matematicamente e fisicamente o comportamento elétrico desses armazenadores de energia. Modelos teóricos visam facilitar o entendimento de um tópico complexo construídos a partir de conhecimentos básicos que atuam como estrutura para o domínio pleno sobre o assunto. Logo, dependendo do propósito, pode-se analisar a célula de bateria sob a influência de inúmeras condições considerando carga, descarga, temperatura, ciclo de vida, entre outros parâmetros.

Os modelos de baterias existentes são variados e cada um possui seu propósito na aplicação que estão sendo utilizados. Em alguns cenários, diferentes modelos teóricos possuem uma resposta mais apropriada quanto ao seu comportamento do que outros (LIU; LI; PENG; ZHANG, 2018). Todavia, as representações de bateria, por mais complexa que ela seja, podem ser construídas a partir dos elementos de circuito elétrico comuns. Logo, devido a simplicidade na análise e facilidade na compreensão, o circuito elétrico equivalente de baterias é representado pela combinação de agregados em série ou em paralelo de resistores, capacitores e indutores.

A aplicação dos modelos teóricos possui utilidade na simulação de performance de células de baterias, otimização de sistemas de gerenciamento de baterias (BMS), gerenciamento de energia e a previsão da vida útil da bateria. Esses temas estão intrinsecamente ligados no desenvolvimento de baterias de veículos elétricos, sistemas de armazenamento de energia renovável e dispositivos portáteis.

Antes de se ingressar nos variados modelos de células de baterias, é importante a compreensão das definições dos principais termos utilizados na parametrização no circuito equivalente dos componentes discutidos neste TCC.

#### 2.1.2.1 Estado de Carga (SoC) e Profundidade de Descarga (DoD)

O estado de carga, também conhecido pelo termo em inglês *State of Charge* (SoC), refere-se a um parâmetro de células de baterias que avalia quantitativamente a carga elétrica armazenada disponível na bateria com relação a sua carga total nominal.

O estado de carga é uma característica que varia entre os limites de 100 % a 0 %, representando carga completa e carga vazia, respectivamente. O parâmetro do estado de carga não pode ser medido de forma direta, mas pode ser estimado a partir do levantamento de diferentes dados do armazenador elétrico tais como a tensão nos terminais da bateria contagem de carga elétrica, dados eletroquímicos ou pela utilização de um filtro de Kalman.

Em linhas gerais, pode-se definir o estado de carga de uma célula de bateria pela Equação (4) expressa por:

$$SoC(t) = \frac{Q_{restante}(t)}{Q_{total}} * 100 [\%], 0 \le Q_{restante}(t) \le Q_{total}$$

(4)

No qual Q<sub>restante</sub>(t) e Q<sub>total</sub>(t) representam a carga remanescente na célula e a carga total na célula de bateria, respectivamente. O estado de carga tanto no carregamento quanto no descarregamento de uma bateria não possui característica linear e pode depender de outros parâmetros tais como o estado de saúde, resistência interna, temperatura ambiente, entre outros. A Figura 4 demonstra uma curva típica do estado de carga no carregamento e descarregamento, respectivamente.

Figura 4 – Representação gráfica do estado de carga de uma bateria, em vermelho, curva de carregamento, em

Fonte: Hariprasad e Priyanka, 2020.

Outro parâmetro amplamente usado é a profundidade de descarga (DoD) que representa o valor complementar da SoC. No caso, a DoD representa quanto de carga foi retirado do sistema em uma determinada descarga. Assim como o outro parâmetro, ela pode ser expressa na forma percentual ou em forma de energia armazenada em Amperes-hora, Ah. Matematicamente, expressa-se por:

$$DoD(t) = \left(1 - \frac{Q_{restante}(t)}{Q_{total}}\right) * 100 [\%], 0 \le Q_{restante}(t) \le Q_{total}$$

(5)

#### 2.1.2.2 Estado de Saúde

O estado de saúde, também conhecido pelo termo em inglês *State of Health* (SoH), é o parâmetro de células de bateria que caracteriza a performance do componente comparandose a capacidade de carga total nominal da célula quando nova para a capacidade de carga total disponível. Assim como a SoC, a SoH é medida em porcentagem variando-se de 0% a 100%.

O estado de saúde é um importante parâmetro de células de bateria pois descreve a degradação do componente devido a avarias com o envelhecimento do material, exposição ao clima, infraestrutura ou uso concomitante com outros equipamentos. Em tese, células de baterias saem com esse parâmetro em 100% de fábrica e, naturalmente, tem esse valor decrescido com o tempo de uso.

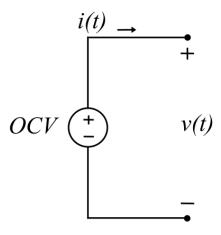

#### 2.1.3 Modelo de Tensão de Circuito Aberto (OCV)

O modelo de Tensão de Circuito Aberto (OCV), também conhecido pelo termo em inglês *Open Circuit Voltage*, é o método mais simples de representação do comportamento de uma célula de bateria. Segundo Plett (2018), esse modelo baseia-se na utilização de uma fonte de tensão constante ideal onde o comportamento da tensão do componente independe da corrente elétrica e com saída de tensão constante a OCV. Ainda, esse sistema é sem memória, isto é, suas saídas independem de valores passados. A Figura 5 mostra o esquemático elétrico do módulo de uma célula de bateria no modelo citado.

Figura 5 – Diagrama esquemático do modelo de Tensão de Circuito Aberto para células de bateria.

Fonte: Elaboração Própria.

A fórmula (6) demonstra a representação matemática desse modelo para tempo contínuo, portanto:

$$v(t) = OCV, \qquad 0 \le t \tag{6}$$

Discretizando-se o sistema para amostragens com período T, o modelo pode ser representado por:

$$\nu[n] = \nu(nT) = OCV$$

, onde  $\forall n \in \mathbb{N}: 0 \le n$  (7)

Apesar do sistema ser inadequado para representação de um modelo real, é possível notar as principais características das células de bateria que é a de fornecer uma tensão para uma carga e a de ser previsível o valor de sua tensão para uma célula em equilíbrio sem carga conectada a ela.

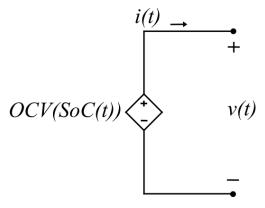

#### 2.1.4 Modelo de Tensão de Circuito Aberto (OCV) Variável

Como explicado na seção 2.1.1.1 sobre o parâmetro do estado de carga de uma célula de bateria, a carga elétrica útil da bateria é consumida para suprir energia elétrica conforme demandado. Dessa forma, o modelo de bateria ideal da seção 2.1.2 demonstra-se fisicamente impossível uma vez que se considerou uma fonte de tensão constante que, independentemente

do tempo de operação, não tem sua tensão alterada apesar da energia acumulada ser consumida até o esgotamento.

Portanto, considerando a relação entre a quantidade finita de energia armazenada no componente e uma fonte de tensão de referência, o modelo da bateria ideal (PLETT, 2018) pode ser mais bem representado por uma fonte de tensão elétrica variável, como na Figura 6.

Figura 6 – Diagrama esquemático do modelo de Tensão de Circuito Aberto Variável para células de bateria.

Fonte: Elaboração Própria.

As tensões da modelagem do circuito, em tempo contínuo e discreto, respectivamente, podem ser expressas pela relação:

$$v(t) = OCV(SoC(t)), \quad 0 \le t \tag{8}$$

$$\nu[n] = \nu(nT) = OCV(SoC[n]), \quad onde \ \forall \ n \in \mathbb{N}: 0 \le n$$

(9)

Assim, considerando a corrente elétrica i(t) que circula no circuito da Figura 6, positivo na descarga, a SoC pode ser definida como:

$$\frac{d(SoC(t))}{dt} = -\frac{i(t)}{Q_{total}} \tag{10}$$

$$SoC(t) = SoC(t_0) - \frac{1}{Q_{total}} \int_{t_0}^{t} i(\tau)d\tau$$

(11)

Em tempo discreto, assumindo corrente constante no intervalo de amostragem T, a n-ésima amostra pode ser expressa pela relação (12), logo:

$$SoC[n] = SoC[n-1] - \frac{i[n]T}{Q_{total}}$$

(12)

Como as células de baterias não podem ser consideradas componentes ideais, considerando um fator de eficiência  $\eta[n]$ , conhecido como eficiência da carga, onde  $0 \le \eta[n] \le 1$ , define-se a taxa de variação do estado de carga e o estado de carga discretizado, respectivamente, como:

$$\frac{d(SoC(t))}{dt} = -\frac{i(t)\eta(t)}{Q_{total}}$$

(13)

$$SoC[n] = SoC[n-1] - \frac{i[n]\eta[n]T}{Q_{total}}$$

(14)

Como regra prática, a eficiência na descarga pode ser considerada como  $\eta[n] \approx 1$ , na carga, no entanto, pode ser menor que a unidade devido a reações secundárias que dispersam a carga.

A eficiência supracitada não deve ser confundida com eficiência energética, nesse sentido, a perda de cargas pelas não-idealidades das reações químicas e impurezas nos compostos representam a eficiência de carga. Logo, a eficiência de carga trata exclusivamente do saldo líquido das cargas elétricas envolvidas no fenômeno.

Já a eficiência energética refere-se a energia que entra e sai do sistema e está relacionada a perdas por aquecimento, vibração, entre outros. Em células de bateria de íons de lítio, a eficiência de carga e eficiência energética são geralmente na ordem de 99% (WANG et al., 2021) e 95% (TOMAN et al., 2016), respectivamente.

Outra idealidade negligenciada é a dependência da temperatura na tensão de circuito aberto e, portanto, pode ser incluído no modelo como OCV(SoC(t), T(t)).

## 2.1.5 Modelo Resistência Série Equivalente, "Rint"

Desse modelo em diante, os circuitos equivalentes da célula de bateria possuem tensão terminal diferente do OCV devido a passagem de corrente quando a célula está conectada a carga. De maneira geral, a modelagem dos circuitos é constituída de componentes passivos que representam as perdas e comportamentos das células de bateria.

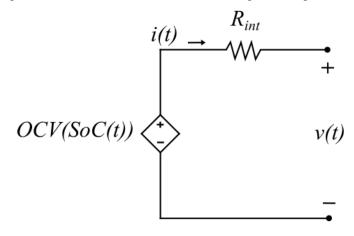

A Figura 7 mostra o circuito equivalente modelado (PLETT, 2018) com a adição de uma resistência em série com uma fonte de tensão variável.

Figura 7 – Diagrama esquemático do modelo de Resistência Série Equivalente para células de bateria.

Fonte: Elaboração Própria.

A tensão terminal em tempo contínuo pode ser expressa pela seguinte relação:

$$v(t) = OCV(SoC(t)) - i(t)R_{int}, \quad 0 \le t$$

(15)

Como é possível observar, uma parte da potência é dissipada no resistor R<sub>int</sub> em forma de calor e impossibilita a eficiência energética perfeita. Além disso, devido a simplicidade do modelo, o circuito é apropriado para simples projetos em eletrônica e falha no aspecto comportamental de sistemas de consumo mais complexos e aplicações de VE's.

Em tempo discreto, assumindo corrente constante no intervalo de amostragem T, a n-ésima amostra da tensão terminal pode ser expressa pela relação (16), logo:

$$v[n] = v(nT) = OCV(SoC[n]) - i[n]R_{int}$$

(16)

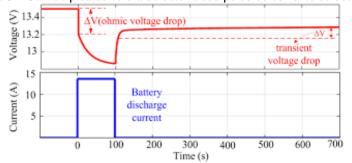

Teoricamente, a componente R<sub>int</sub> com corrente circulante modela uma resposta instantânea a um estímulo na entrada do circuito. No entanto, conforme demonstra a Figura 8, quando submetida a um degrau de descarga de corrente, pode-se verificar que a tensão possui uma resposta dinâmica (não instantânea) que desacelera a descarga.

Figura 8 – Curva típica de célula de bateria sob pulso de corrente de descarga.

Fonte: Rouholamini, 2022.

Da mesma forma, quando a célula é deixada em repouso, a tensão retorna lentamente ao OCV com um pequeno desnível. Esse fenômeno é causado pelo processo de difusão no composto da célula e se relaciona com as propriedades químicas do material. Segundo VAN DER VEN, BHATTACHARYA e BELAK (2013), em compostos intercalados, como os eletrodos de íon lítio em células de bateria, a difusão correlaciona-se com a estrutura cristalina do material e a concentração do íon. Logo, os coeficientes de difusão mostram-se intrinsecamente relacionados a esses parâmetros.

Portanto, pode-se notar que o presente modelo não consegue cobrir inteiramente o comportamento da célula e pode ser aprimorado a fim de se aproximar à realidade. Na próxima seção, portanto, atribui-se componentes transitórios que possuem a capacidade de adicionar tais propriedades na modelagem.

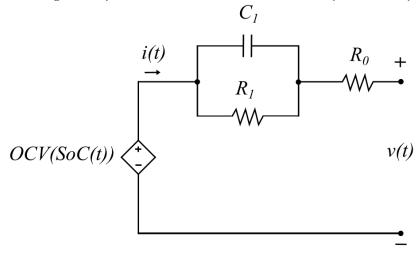

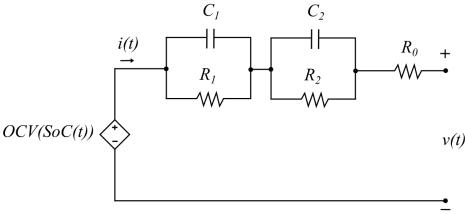

### 2.1.6 Modelo da Tensão na Célula por Thévenin

Seguindo no raciocínio da seção passada, os processos de difusão adicionam uma resposta transitória ao comportamento da célula. Desse modo, a partir da construção de modelos com componentes fundamentais de circuitos elétricos, pode-se modelar esse comportamento com um ou mais pares de resistor-capacitor em paralelo (PLETT, 2018). A Figura 8 mostra o circuito equivalente com a adição de um par do subcircuito.

Figura 9 – Diagrama esquemático do modelo de Tensão na Célula por Thévenin para células de bateria.

A modelagem matemática pode ser desenvolvida a partir do mesmo raciocínio desenvolvido nas seções anteriores. Para o circuito mostrado anteriormente, portanto, expressa-se a tensão terminal v(t) como:

$$v(t) = OCV(SoC(t)) - v_{C1}(t) - i(t)R_0, \ 0 \le t$$

(17)

Analisando o circuito, pode-se reescrever a expressão (17) em função das correntes envolvidas, portanto:

$$v(t) = OCV(SoC(t)) - i_{R_1}(t)R_1 - i(t)R_0$$

(18)

A corrente que percorre o resistor  $R_1$  somada a corrente que atravessa o componente  $C_1$ , como dita a lei de Kirchhoff, deve ser igual a corrente i(t) do circuito. Logo, modela-se as correntes pelas seguintes expressões:

$$i_{C_1}(t) = \dot{v}_{C_1}(t)C_1 \tag{19}$$

$$i(t) = i_{R_1}(t)R_1 + \dot{v}_{C_1}(t)C_1 \tag{20}$$

Como a tensão em C<sub>1</sub> é igual a tensão do resistor R<sub>1</sub>, na expressão (20), tem-se:

$$i(t) = i_{R_1}(t)R_1 + \frac{di_{R_1}(t)}{dt}C_1R_1$$

(21)

Rearranjando a expressão, portanto:

$$\frac{di_{R_1}(t)}{dt} = -\frac{1}{C_1 R_1} i_{R_1}(t) + \frac{1}{C_1 R_1} i(t)$$

(22)

Discretizando a análise, pode-se deduzir a equação (21) para tempo discreto. Assumindo tempo de amostragem T, a n-ésima amostra do estado de carga em tempo discreto é dado pela expressão (9), a corrente no resistor  $R_1$  e a tensão terminal em tempo discreto são dados, respectivamente, pelas expressões a seguir:

$$i_{R_1}[n] = e^{-\frac{T}{C_1 R_1}} i_{R_1}[n-1] + (1 - e^{-\frac{T}{C_1 R_1}}) i[n-1]$$

(23)

$$\nu[n] = OCV(SoC[n]) - i_{R_1}[n]R_1 - i[n]R_0$$

(24)

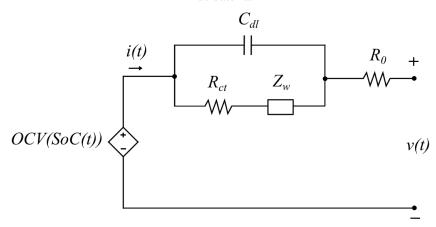

### 2.1.7 Circuito de Randles e Modelo Impedância de Warburg

Na análise do circuito equivalente da célula de bateria, pode-se adicionar o elemento de impedância de Warburg, Z<sub>w</sub>. O elemento tem como objetivo modelar o processo de difusão no dielétrico da célula de bateria.

Apesar de comum a representação em sistemas eletroquímicos, a resistência de Warburg pode ser difícil de se identificar isoladamente devido à proximidade em série com a resistência de carga do circuito de Randles.

O circuito de Randles é um modelo de circuito equivalente que representa o comportamento de fenômenos eletroquímicos (RANDLES, 1947). Pode-se aproximar o modelo da célula de bateria de acordo com a Figura 10.

Figura 10 – Diagrama esquemático do modelo de Impedância de Warburg com Circuito de Randles para células de bateria.

Onde R<sub>0</sub>, R<sub>ct</sub>, C<sub>dl</sub> e Z<sub>w</sub> representam a resistência do eletrólito, resistência de transferência de carga, isto é, modela a diferença de potencial entre eletrodo e eletrólito, capacitância de camada dupla, onde simula o efeito das cargas acumulada no eletrólito e a impedância de Warburg, respectivamente.

Segundo LIM (2011), a impedância de Warburg pode ser expressa pela equação (24), logo, varia com a frequência de oscilação:

$$Z_w = \frac{A_w}{\sqrt{jw}} \tag{24}$$

Onde A<sub>w</sub>, j e w representam o coeficiente de Warburg, unidade imaginária e frequência angular, respectivamente.

Para determinadas faixas de frequência, a impedância de Warburg aproxima-se de rede em série de capacitor-resistor em paralelo. Quanto maior a ordem da rede, isto é, mais extenso o número de módulos capacitor-resistor, melhor a aproximação com a impedância de Warburg. Dessa forma, a Figura 11 mostra o circuito equivalente

Figura 11 — Diagrama esquemático do modelo de rede em série de capacitor-resistor em paralelo para células de bateria.  $C_1 \qquad \qquad C_2$

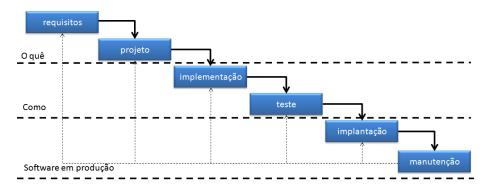

## 2.2 MÉTODO DE DESENVOLVIMENTO EM "V" E TESTE DE PRODUTOS

Em processos de desenvolvimento, o modelo em V representa um modelo conceitual no desenvolvimento de produtos que pode ser considerado como uma variante do modelo em cascata. A principal diferença entre os modelos consiste na ocorrência de testes rodando em paralelo em cada fase de desenvolvimento ao passo que o desenvolvimento em cascata prevê o sequenciamento dos processos entre as fases do projeto (PETERSEN; WOHLIN; BACA, 2009). No caso do modelo em cascata, até que a aprovação não seja aceita, não é permitido a transição de fases e, consequentemente, desacelerando e imbricando todo o desenvolvimento.

Para contextualização, o modelo em cascata é um modelo de organização de atividades no processo de desenvolvimento segmentado em fases sequenciais lineares, isto é, as atividades são repassadas entre cada tarefa dependendo dos entregáveis da atividade anterior. Esse modelo de desenvolvimento mostra-se útil quando o escopo do trabalho é claramente definido como em projetos de manufatura e construção civil ou industrial onde alterações nas estruturas físicas de construções, por exemplo, tornam-se caros desde os passos iniciais.

Conforme o avanço do projeto, o modelo em cascata torna-se cada vez menos iterativo e flexível. Formalmente, as fases desse modelo são nomeadas sequencialmente como: requerimento, projeto, implementação, teste e manutenção. Uma representação gráfica é mostrada na Figura 12. A transição entre fases nesse modelo dá-se exclusivamente quando

as ações pertinentes a atual fase for totalmente encerrada respeitando rigidamente a ordem das fases sem possibilidade de paralelismo e pulo de fases.

Figura 12 – Representação gráfica do fluxo de trabalho do modelo em cascata conforme o andamento do projeto.

Fonte: Fabri, J. A., 2013.

Pelo exposto, portanto, o modelo em cascata mostra-se um método excessivamente rígido que pode frustrar o cliente na adequação de incertezas durante as fases iniciais do projeto, principalmente. Além disso, o modelo prevê um protótipo operacional somente ao final do projeto sem possibilidade de alteração. Na realidade, dificilmente, projetos seguem o fluxo sequencial à risca, logo, no modelo em cascata, alterações podem provocar confusão e atrasos na equipe.

Nesse sentido, um modelo de desenvolvimento menos rígido e que facilite a adequação do produto às necessidades do cliente é preferível. Logo, o modelo em V supre essa necessidade e atende ao que é demandado em projetos modernos.

O principal ponto do modelo em V é garantir a qualidade e eficiência em todas as etapas do ciclo de vida de um projeto. Graficamente, o modelo é representado temporalmente ao longo do eixo horizontal registrando as atividades para a conclusão do projeto. As fases iniciais consistem no levantamento de requisitos e concepção do projeto a ser desenvolvido e as fases finais são os processos de teste e validação. No eixo vertical, representa- as atividades de validação complementares entre todas as fases do projeto.

A representação em V, mostrado na Figura 13, é baseado na simetria da forma onde as fases da esquerda e as fases da direita correspondem, respectivamente, as atividades de desenvolvimento e validação, garantindo que os requisitos são entendidos corretamente.

Operation Concept of Operations and Maintenance **Verification** and Validation Project \

Definition System Verification Requirements end Architecture and Validation Integration, Project Test and Detailed Test, and ( Verification Design Integration Time