# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Frederico Ferlini

# PLAESER - PLATAFORMA DE EMULAÇÃO DE SOFT ERRORS VISANDO A ANÁLISE EXPERIMENTAL DE TÉCNICAS DE TOLERÂNCIA A FALHAS: UMA PROTOTIPAÇÃO RÁPIDA UTILIZANDO FPGAS

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do Grau de Mestre em Engenharia Elétrica. Orientador: Prof. Dr. Eduardo Augusto Bezerra

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Áutomática da Biblioteca Universitária da UFSC.

Ferlini, Frederico

PLAESER - Plataforma de Emulação de Soft Errors Visando a Análise Experimental de Técnicas de Tolerância a Falhas [dissertação] : uma prototipação rápida utilizando FPGAs / Frederico Ferlini ; orientador, Eduardo Augusto Bezerra - Florianópolis, SC, 2012.

159 p. ; 21cm

Dissertação (mestrado) - Universidade Federal de Santa Cararina, Centro Tecnológico. Programa de Pós-Graduação em Engenharia Elétrica.

Inclui referências

1. Engenharia Elétrica. 2. Tolerância a falhas. 3. Injeção de Falhas em Hardware. 4. FPGA. 5. Reconfiguração Parcial Dinâmica. I. Bezerra, Eduardo Augusto . II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

### Frederico Ferlini

# PLAESER - PLATAFORMA DE EMULAÇÃO DE SOFT ERRORS VISANDO A ANÁLISE EXPERIMENTAL DE TÉCNICAS DE TOLERÂNCIA A FALHAS: UMA PROTOTIPAÇÃO RÁPIDA UTILIZANDO FPGAS

Esta Dissertação foi julgada adequada para obtenção do Título de Mestre em Engenharia Elétrica, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina

Florianópolis, 29 de junho de 2012.

Prof. Patrick Kuo Peng, Dr. Coordenador do Curso

#### Banca Examinadora:

Prof. Eduardo Augusto Bezerra, Dr. Presidente (Orientador)

Universidade Federal de Santa Catarina

Prof. Fernando Gehm Moraes, Dr.

Pontificia Universidade Católica do Rio Grande do Sul

Prof. Djones Vinicius Lettnin, Dr. Universidade Federal de Santa Catarina

Prof. José Luís Almada Güntzel, Dr. Universidade Federal de Santa Catarina

Este trabalho é dedicado aos meus Amigos/Colegas e principalmente aos meus extraordinários Pais/Irmãos que, assim como Deus, sempre acreditaram em mim, inquestionavelmente.

#### **AGRADECIMENTOS**

Primeiramente, gostaria de agradecer ao Prof. Dr. Eduardo Augusto Bezerra pela oportunidade de realizar o mestrado na UFSC, por prover os recursos necessários para a pesquisa e pela orientação, entusiasmo, compreensão e paciência ao longo do desenvolvimento desse trabalho.

Agradeço principalmente a minha Família que, de forma inquestionável, me apoiou em todas as decisões que tomei até então. Agradeço a minha Mãe a quem amo muito e que, mesmo sentindo muito a falta dos filhos que moram longe, procurou não transparecer a saudade e me ajudou muito com a sua compreensão, conselhos e carinho sempre que precisei. Agradeço ao meu Pai e sua esposa a quem amo muito, por sempre atenderem a qualquer pedido de ajuda de forma inquestionável e acreditarem em mim independente do que eu faça. Não menos importante, eu agradeço aos meus Irmãos a quem amo muito e que me apoiam incondicionalmente, sem nem mesmo saber direito qual a minha área de atuação. Finalmente, não menos distante, agradeço aos meus primos que completam a minha família e a quem, da mesma forma, amo muito.

Agradeço aos meus Amigos/Colegas que, além de me apoiarem, dão à minha vida motivo de viver através da alegria e pelo simples fato de estar junto deles, inclusive pelas inúmeras histórias que escrevemos juntos. Agradeço especialmente àqueles que pegaram a estrada para passarem um tempo comigo, aos que compreenderam os meus momentos de isolamento e, principalmente, àqueles que aturaram as minhas manias e teorias durante nosso convívio. Agradeço também ao Badoo por dar uma ajuda em momentos difíceis.

Agradeço a UFSC e a CAPES (Coordenação de Aperfeiçoamento de Pessoal de Nível Superior), que forneceram o suporte para o desenvolvimento deste trabalho.

Enfim, dessa vez não é para pedir, mas sim para agradecer. Muito obrigado Deus, por sempre se mostrar presente quando mais precisei e atender às minhas preces, de maneira que me encorajou a ser uma pessoa melhor.

"If a problem has no solution, it may not be a problem, but a fact - not to be solved, but to be coped with over time"

(Shimon Peres)

#### RESUMO

O constante avanço na fabricação de circuitos integrados com a miniaturização da tecnologia, o aumento da frequência de operação e a diminuição da tensão de alimentação fazem deles cada vez mais sensíveis à radiação. A preocupação com a sensibilidade de circuitos integrados não é mais restrita a projetos de aplicações espaciais onde o ambiente é mais hostil quanto à radiação. Circuitos fabricados com tecnologias em escala nanométrica são potencialmente sensíveis a partículas que se encontram na atmosfera terrestre e até no nível do mar. A importância da tolerância a falhas em semicondutores existe desde quando anomalias foram observadas no comportamento de dispositivos operando no espaco. A larga presenca de circuitos integrados em diversas áreas do nosso cotidiano faz com que técnicas de tolerância a falhas ganhem importância também para aplicações terrestres. Desse modo, formas eficientes de avaliação dessas técnicas de tolerância a falhas são essenciais para lidar com essa demanda. É importante que essa avaliação possa ser realizada em etapas iniciais do projeto de circuitos integrados tolerantes à radiação de forma a reduzir o custo com locação de instalações que utilizam equipamentos de radiação induzida para verificação. Nesse contexto, o trabalho de dissertação apresenta um estudo sobre diferentes técnicas de injeção de falhas. Além do estudo, foi desenvolvida uma plataforma de emulação de soft errors (PLAESER) visando a análise experimental de técnicas de tolerância a falhas. A plataforma PLAESER provê suporte ao fluxo proposto para avaliação de técnicas de tolerância a falhas em fase inicial do projeto de circuitos robustos através da prototipação rápida em FPGAs. Os resultados obtidos com os casos de teste utilizados procuram mostrar o emprego do fluxo proposto para análise de técnicas de tolerância a falhas.

**Palavras-chave**: Emulação de falhas. *Soft Errors*. Reconfiguração parcial. Prototipação rápida. FPGA. Circuitos reconfiguráveis. Injeção de falhas. Tolerância a falhas. Circuitos endurecidos.

#### ABSTRACT

The continuous improvements in the integrated circuits manufacture process considering the miniaturization of technology, increase of clock frequencies and limitation of power supply, make them more susceptible to radiation. The concern with circuit sensitivity is no longer restricted to space applications, in harsh environment. Integrated circuits manufactured with nanometric technologies are potentially sensitive to particles present in the atmosphere and also at the sea level. Fault tolerance strategies applied to semiconductors have been around since upsets were first experienced in space applications. The large usage of integrated circuits in several areas of everyday life makes fault tolerance techniques important also for terrestrial applications. Therefore, efficient hardness evaluation solutions are essential to deal with this demand. Such evaluation is important and should be performed earlier in hardened integrated circuit designs in order to reduce costs with rental of radiation facilities. In this context, this work presents a evaluation of different fault injection techniques. Moreover, a soft error emulation platform (PLAESER) has been developed in order to analyze fault tolerance techniques experimentally. PLEASER gives support to the flow proposed to evaluate fault tolerance techniques earlier in hardened circuit designs through rapid prototyping. The results obtained with the selected test cases show the employment of the proposed flow to analyze fault tolerance techniques.

**Keywords**: Partial reconfiguration. Soft errors. Reconfiguration circuits. Fault tolerance. Hardened circuit. FPGA. Fault emulation. Fault injection. Rapid prototyping.

# LISTA DE FIGURAS

| Figura 1 - Relação entre falha, erro e defeito                               | 21  |

|------------------------------------------------------------------------------|-----|

| Figura 2 - Ambiente radioativo espacial.                                     |     |

| Figura 3 - Relação entre as fontes de radiação e os efeitos nos componentes  | 26  |

| Figura 4 - Exemplo de um SET.                                                | 28  |

| Figura 5 - Arquitetura genérica de um FPGA                                   | 29  |

| Figura 6 - Memória de configuração do FPGA.                                  | 30  |

| Figura 7 - Cadeias de <i>scan</i> propostas em (33).                         |     |

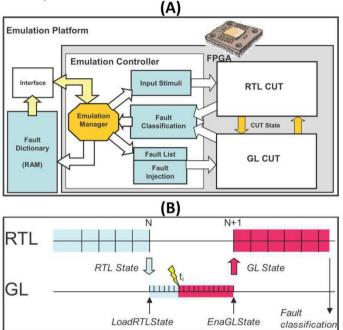

| Figura 8 - (A) Plataforma de emulação AMUSE (34) - (B) Troca de RTL par      |     |

| GL para emulação do efeito SET                                               | 40  |

| Figura 9 - Os equivalentes em GL de um elemento (A) combinacional e um (     | (B) |

| sequencial instrumenta da AMUSE.                                             | 41  |

| Figura 10 - Fluxo proposto em (35) para diminuir a intrusão da instrumentaç  |     |

|                                                                              | 42  |

| Figura 11 - Controlador de localização e o exemplo de um registrador         |     |

| instrumentado utilizado pela técnica apresentada em (36)                     |     |

| Figura 12 - Fluxo do sistema FLIPPER (37).                                   |     |

| Figura 13 - DTE da FT-UNSHADES (39).                                         |     |

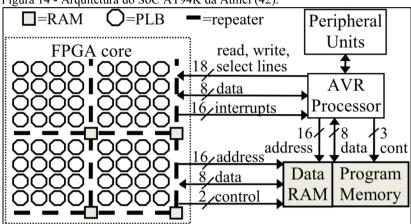

| Figura 14 - Arquitetura do SoC AT94K da Atmel (42).                          | 46  |

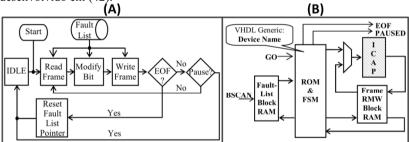

| Figura 15 - O fluxo (A) e a arquitetura (B) do bloco de injeção de falha     |     |

| desenvolvido em (42).                                                        |     |

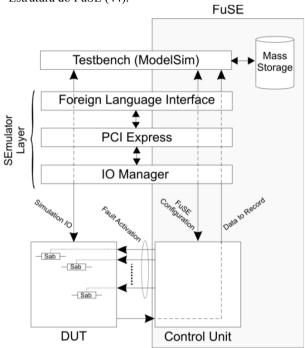

| Figura 16 - Estrutura do FuSE (44)                                           |     |

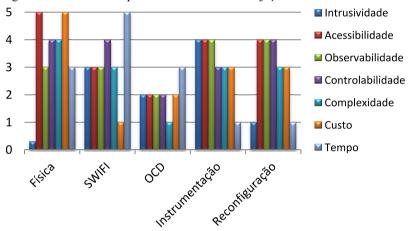

| Figura 17 - Resumo comparativo das técnicas de injeção                       | 48  |

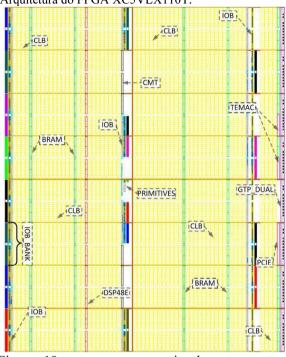

| Figura 18 - Arquitetura do FPGA XC5VLX110T.                                  | 52  |

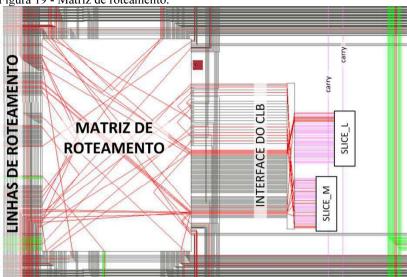

| Figura 19 - Matriz de roteamento.                                            |     |

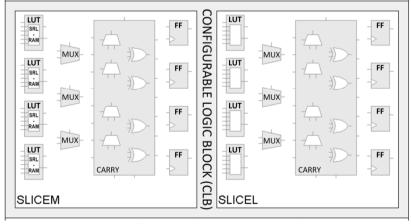

| Figura 20 - Configurable Logic Block (CLB).                                  |     |

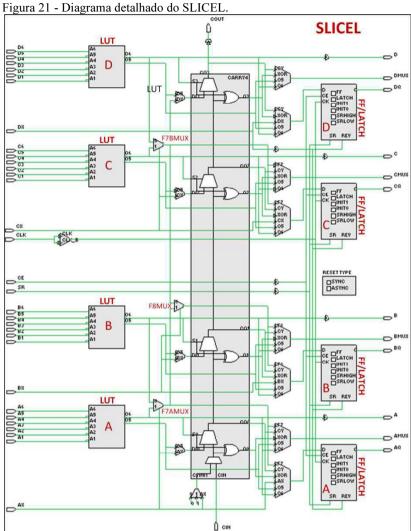

| Figura 21 - Diagrama detalhado do SLICEL.                                    |     |

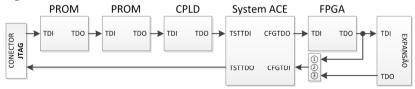

| Figura 22 - Cadeia de conexão do JTAG.                                       | 56  |

| Figura 23 - Arquitetura do JTAG encontrada nos FPGAs da Xilinx               |     |

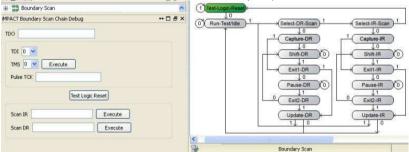

| Figura 24 - Ferramenta iMPACT em modo de depuração da cadeia JTAG            |     |

| Figura 25 - Exemplo (em hexa) do <i>bitstream</i> em formato texto           |     |

| Figura 26 - Exemplo da utilização da interface UART do V5SC                  |     |

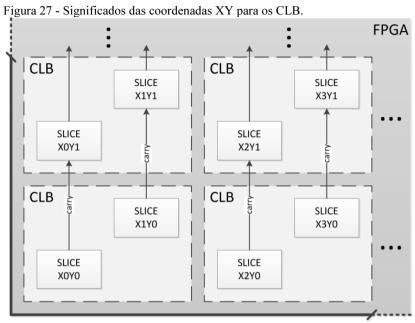

| Figura 27 - Significados das coordenadas XY para os CLB                      |     |

| Figura 28 - Campos da palavra de 32 bits de endereço                         |     |

| Figura 29 - Sistema de coordenadas X endereçamento.                          | /1  |

| Figura 30 - Visão em profundidade da metade inferior da memória de           | 72  |

| configuração do FPGA.                                                        |     |

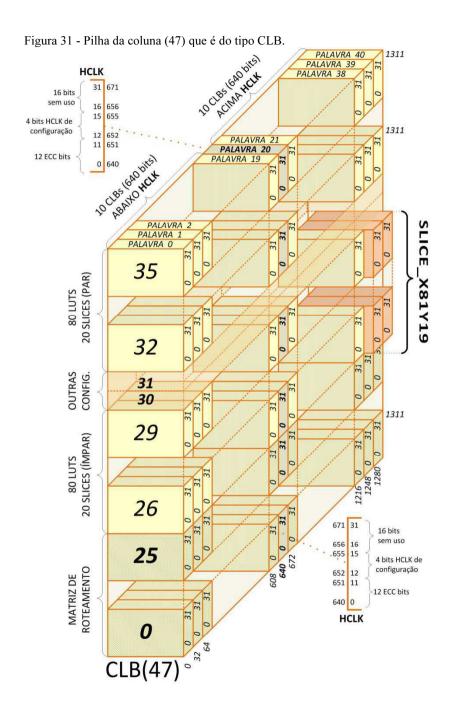

| Figura 31 - Pilha da coluna (47) que é do tipo CLB.                          |     |

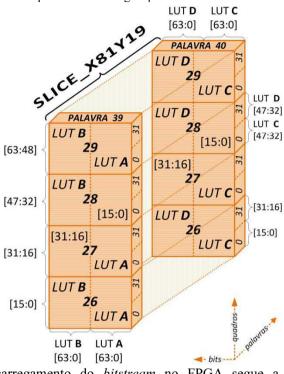

| Figura 32 - As oito palavras de configuração das LUTs do <i>slice</i> X81Y19 | /6  |

| Figura 33 - Função de conversão da coordenada XY para o endereço da          |     |

| memória de configuração do FPGA XC5VLX110T                                   |     |

| Figura 34 - Trajetória do <i>bitstream</i> de configuração do FPGA           |     |

| Figura 35 - Planos da memória do FPGA da Xilinx                              | /X  |

| Figura 36 - Função que converte as coordenadas de um slice no índice da     |       |

|-----------------------------------------------------------------------------|-------|

| palavra do bitstream com os 16 bits iniciais da configuração da LUT         |       |

| Figura 37 - Sistema Injetor de Falhas.                                      | 82    |

| Figura 38 - Estrutura de funcionamento do GLIFA (Gerador de Lista de Fall   | has). |

| Figura 39 - Estrutura de informações dos slices da Virtex5 encontrada na    | 07    |

| biblioteca do GLIFA                                                         | 88    |

| Figura 40 - Amostra dos parâmetros encontrados na biblioteca do GLIFA       | 00    |

| "FPGA MODEL.LIB"                                                            | 89    |

| Figura 41 - Arquivo com a lista de falhas gerada pelo GLIFA                 |       |

| Figura 42 - Arquitetura do SoCIF                                            |       |

| Figura 43 - Fluxo completo do software do SoCIF.                            |       |

| Figura 44 - Fluxo Básico                                                    |       |

| Figura 45 - O topo "Sistema de Injeção de Falhas" (SIF) com os blocos de    |       |

| entrada/saída dos DUTs e a instanciação dos dois DUTs FAULTY/GOLDE          | N.    |

|                                                                             |       |

| Figura 46 - Modelo do TOPO SIF.                                             |       |

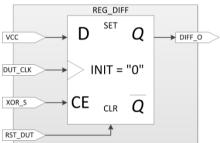

| Figura 47 - Ilustração do registrador gerador do sinal resultante do módulo |       |

| comparador.                                                                 | .106  |

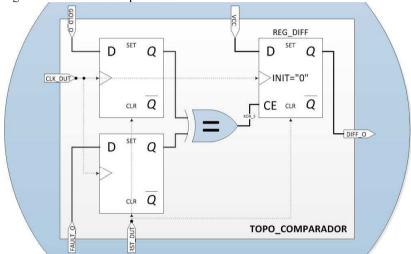

| Figura 48 - Módulo Comparador.                                              |       |

| Figura 49 - Aplicação do atributo no TOPO SIF                               | .108  |

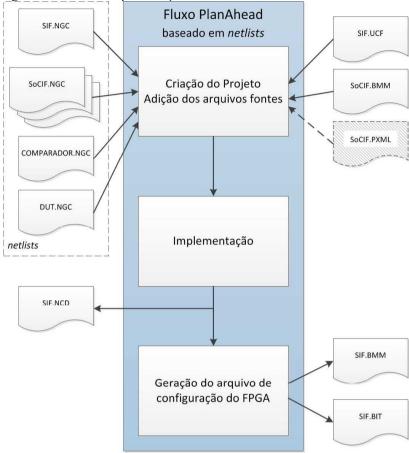

| Figura 50 - Fluxo de implementação do PlanAhead™ utilizando netlists        | .109  |

| Figura 51 - Exemplo de restrição de área utilizando a devida sintaxe do UCI | ₹.    |

|                                                                             | .110  |

| Figura 52 - Exemplo do arquivo de descrição do circuito implementado        |       |

| utilizando a linguagem XDL.                                                 | .111  |

| Figura 53 - Exemplo do relatório de resultados gerado ao final do fluxo do  |       |

| PLAESE.                                                                     |       |

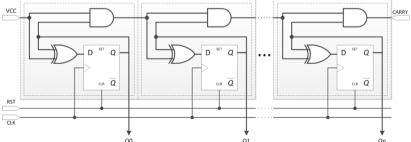

| Figura 54 - O esquemático ilustrativo do caso de teste do contador          |       |

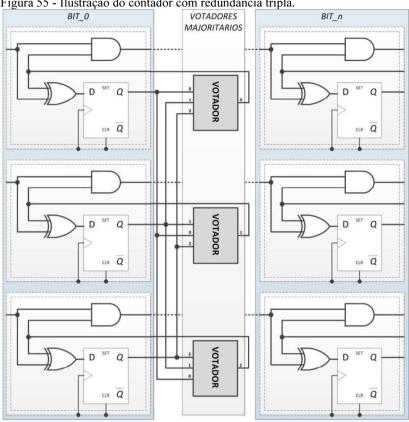

| Figura 55 - Ilustração do contador com redundância tripla.                  |       |

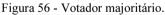

| Figura 56 - Votador majoritário.                                            |       |

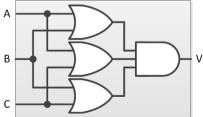

| Figura 57 - Contador TMR exemplo disponibilizado pela Xilinx                | .117  |

| Figura 58 - <i>PlanAhead</i> do contador com a área das instâncias GOLDEN e |       |

| FAULTY estabelecidas.                                                       |       |

| Figura 59 - Resultados da implementação do contador com TMR                 |       |

| Figura 60 - Utilização dos recursos do FPGA XC5VLX110T.                     |       |

| Figura 61 - Resultado da emulação de falhas no contador TMR da Xilinx       |       |

| Figura 62 - Resultado da emulação de falhas acumulada no contador TMR d     |       |

| Xilinx                                                                      |       |

| Figura 63 - PlanAhead do contador sem TMR com a lógica de carry             | .122  |

| Figura 64 - Exemplo do uso da LUT para o acesso ao controle dos             | 122   |

| multiplexadoresFigura 65 - Utilização dos recursos do FPGA XC5VLX110T       |       |

| Figura 65 - Utilização dos recursos do FPGA XC5 VLX1101                     | .124  |

| lógica de carrylógica de carry                                              | 124   |

| lugica ue carry                                                             | . 124 |

| Figura 67 - PlanAhead do contador com TMR sem a lógica de carry125          |

|-----------------------------------------------------------------------------|

| Figura 68 - Utilização dos recursos do FPGA XC5VLX110T                      |

| Figura 69 - Resultado da emulação de falhas no contador com TMR e sem a     |

| lógica de carry                                                             |

| Figura 70 - Resultado da emulação de falhas acumulada no contador com TMR   |

| sem a lógica de carry                                                       |

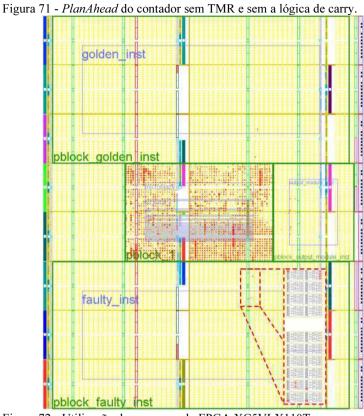

| Figura 71 - PlanAhead do contador sem TMR e sem a lógica de carry128        |

| Figura 72 - Utilização dos recursos do FPGA XC5VLX110T                      |

| Figura 73 - Resultado da emulação de falhas no contador sem TMR e sem a     |

| lógica de carry                                                             |

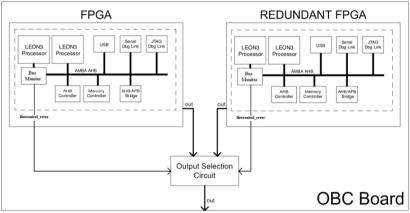

| Figura 74 - Computador de bordo com redundância externa e monitor de        |

| barramento                                                                  |

| Figura 75 - Comandos para geração da "BROM" com a imagem do programa        |

| teste para o LEON3.                                                         |

| Figura 76 - A configuração do SoC do LEON3 e espaço de endereçamento dos    |

| periféricos                                                                 |

| Figura 77 - A reinicialização da execução do software do OBC após a injeção |

| de uma falha134                                                             |

| Figura 78 - PlanAhead da implementação do SIF com a instância do            |

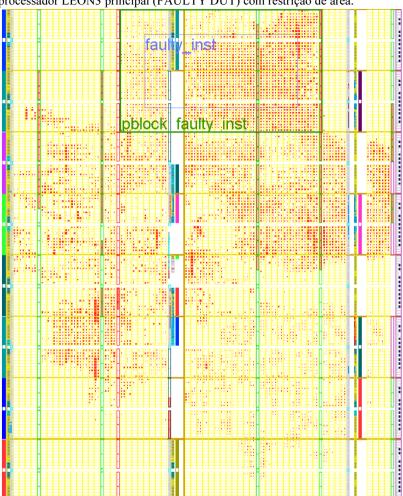

| processador LEON3 principal (FAULTY DUT) com restrição de área135           |

| Figura 79 - Percentual de ocupação do FPGA com o projeto do SIF com o       |

| LEON3                                                                       |

| Figura 80 - Quantidade de recursos do FPGA utilizados no projeto SIF com o  |

| LEON3                                                                       |

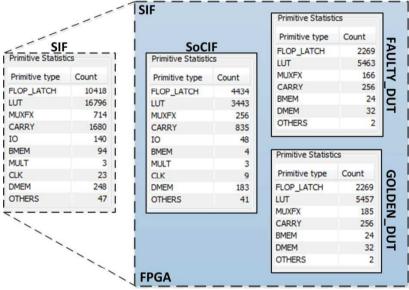

| Figura 81 – Quantidade estimada de componentes utilizados no projeto todo   |

| (SIF) e pelo SoCIF e pelas duas instâncias do DUT (FAULTY e GOLDEN).137     |

| Figura 82 - Resultado da injeção de falhas no OBC com o monitor de          |

| barramento                                                                  |

| Figura 83 - Pseudocódigo do algoritmo executado no VisuAlg                  |

| Figura 84 - A biblioteca descrita no arquivo "fpga.bib"                     |

# LISTA DE TABELAS

| Tabela 1 - Especificação das características do FPGA XC5VLX110T         | 51    |

|-------------------------------------------------------------------------|-------|

| Tabela 2 - Resumo de medidas (palavras/quadro/bitstream/FPGA)           | 61    |

| Tabela 3 - Comandos do V5SC quando em condição de controle              | 64    |

| Tabela 4 - Descrição dos campos da palavra de endereço do FPGA          | 70    |

| Tabela 5 - Tamanho da pilha de cada tipo de coluna                      | 73    |

| Tabela 6 - Resumo do número de quadros nos diferentes planos do FPGA    | 79    |

| Tabela 7 - Campos de cada linha do arquivo "FAULTS.LIST"                | 91    |

| Tabela 8 - Cálculo do intervalo de tempo de cada teste                  | 96    |

| Tabela 9 - Resumo do resultado da injeção de falhas no OBC com o monito | or de |

| barramento.                                                             | 137   |

#### LISTA DE ABREVIATURAS E SIGLAS

AMBA - Advanced Microcontroller Bus Architecture

ASCII - American Standard Code for Information Interchange

ASIC – Application Specific Integrated Circuit

AVR – Advanced Virtual RISC

AXI – Advanced eXtensible Interface

BCC – Bare-C Cross-Compiler

BIST - Built-In Self-Test

BitGen - Bitstream Generator

BMM – Block RAM Memory Map

BRAM - Block RAM

BSDL - Boundary-Scan Description Language

BSP – Board Support Package

CLB – Configurable Logic Block

COTS - Comerical-Off-The-Shelf

CRC - Cyclic Redundancy Check

DCM - Digital Clock Manager

DD - Displacement Damage

DRP - Dynamic Reconfigure Port

DSP – Digital Signal Processing

DUT - Design Under Test

EDIF - Electronic Design Interchange Format

EDK – Embedded Development Kit

ELF – Executable and Linkable Format

ESA – European Space Agency

FAT – File Allocation Table

FIT - Failure in Time

FPGA – Field-Programmable Gate Array

GLIFA – Gerador de Lista de Falhas

GCR - Galactic Cosmic Rays

GCC - GNU Compiler Collection

GPqCom - Grupo de Pesquisa em Comunicações

GSE – Grupo de Sistemas Embarcados

GTP - Gigabit Transceiver

HDL – Hardware Description Language

ICAP – Internal Configuration Access Port

IDE – Integrated Development Environment

ILA – Integrated Logic Analyzer

IOB - Input/Output Block

IP – Intellectual Property

JTAG – Joint Test Action Group

LET – Linear Energy Transfer

LUT - Look-Up Table

MBU – Multiple Bit Upset

MDM – MicroBlaze<sup>TM</sup> Debug Module

MMCM – Mixed-Mode Clock Manager

MPU – Microprocessor Unit

MUT – Module Under Test

NCD - Native Circuit Description

OBC - On-Board Computer

OCD - On-Chip Debug

PLAESER - Plataforma de Emulação de Soft Erros

PLB – Programmable Logic Blocks

PLL – Phase-Locked Loop

RAM – Random Access Memory

RISC – Reduced Instruction Set Computer

RTL – Register Transfer Level

SBE – Single Bit Error

SDK – Software Development Kit

SEE - Single Event Effect

SEL – Single Event Latchup

SEM - Soft Error Mitigation

SER – Soft Error Rate

SET - Single Event Transient

SEU – Single Event Upset

SIF – Sistema Injetor de Falhas

SoCIF – System-on-a-Chip Injetor de Falhas

SRAM – Static RAM

SRL – Shift Register LUT

TAP - Test Access Port

TID – Total Ionization Dose

TMR - Triple Modular Redundancy

UCF – User Constraints File

UFSC - Universidade Federal de Santa Catarina

VHDL – VHSIC Hardware Description Language

VHSIC – Very High Speed Integrated Circuit

V5SC - Virtex-5 SEU Controller

XDL - Xilinx® Description Language

XMD - Xilinx® Microprocessor Debugger

XPS - Xilinx® Plataform Studio

XST - Xilinx® Synthesis Technology

# SUMÁRIO

| 1 INTRODUÇAO                                             | 17 |

|----------------------------------------------------------|----|

| 1.1 MOTIVAÇÃO                                            | 18 |

| 1.2 OBJETIVOS                                            | 19 |

| 1.3 ORGANIZAÇÃO DO TEXTO                                 | 20 |

| 2 CONCEITOS BÁSICOS                                      | 21 |

| 2.1 CONFIABILIDADE                                       | 21 |

| 2.2 RADIAÇÃO E SEUS EFEITOS                              |    |

| 2.3 MODELOS DE FALHAS                                    | 27 |

| 2.4 CIRCUITOS RECONFIGURÁVEIS                            |    |

| 3 INJEÇÃO DE FALHAS (TRABALHOS RELACIONADOS)             | 31 |

| 3.1 TÉCNICAS DE INJEÇÃO FÍSICA DE FALHAS                 | 32 |

| 3.1.1 Método por Radiação                                | 32 |

| 3.1.2 Método por Raios Laser                             | 33 |

| 3.1.3 Método de Injeção por Pinos                        | 33 |

| 3.2 TÉCNICAS DE INJEÇÃO DE FALHAS NO NÍVEL LÓGICO        |    |

| 3.2.1 Software-Implemented Fault Injection (SWIFI)       | 34 |

| 3.2.2 Injeção de Falhas Baseada em Simulação             | 35 |

| 3.2.3 Injeção de Falhas Utilizando Recursos de Depuração | 36 |

| 3.2.4 Injeção de Falhas por Emulação                     | 37 |

| 3.2.4.1 Instrumentação                                   |    |

| 3.2.4.2 Reconfiguração                                   |    |

| 3.2.5 Técnicas Híbridas de Injeção de Falhas             | 46 |

| 4 INVESTIGAÇÃO DA ARQUITETURA ALVO                       |    |

| 4.1 ARQUITETURA                                          |    |

| 4.2 CONFIGURAÇÃO DO FPGA                                 | 55 |

| 4.3 INVESTIGAÇÃO DA MEMÓRIA DE CONFIGURAÇÃO              |    |

| 4.3.1 Configuration Readback                             |    |

| 4.3.2 Controlador V5SC                                   |    |

| 4.3.3 Internal Access Configuration Port (ICAP)          |    |

| 4.4 COORDENADAS X ENDEREÇO DE QUADROS DE MEMÓRIA         |    |

| 5 PLATAFORMA DE EMULAÇÃO DE SOFT ERRORS                  |    |

| 5.1 CIRCUITO RECONFIGURÁVEL – FPGA                       | 82 |

| 5.2 FERRAMENTAS DE SÍNTESE E IMPLEMENTAÇÃO               |    |

| 5.2.1 Ferramenta de Síntese Lógica                       |    |

| 5.2.2 Ferramenta de Síntese Física                       |    |

| 5.2.3 Gerador da Configuração do FPGA                    |    |

| 5.2.4 Tradutor do Descritor de Hardware                  |    |

| 5.2.5 Compilador do Software                             | 86 |

| 5.3 GLIFA – GERADOR DE LISTA DE FALHAS                   |    |

| 5.4 SOCIF – SYSTEM-ON-A-CHIP INJETOR DE FALHAS           | 92 |

| 5.4.1 Arquitetura – Hardware                             |    |

| 5.4.1.1 Controlador da SRAM                              |    |

| 5.4.1.2 Controlador do ICAP                              | 95 |

| 5.4.1.3 Controlador do CompactFlash                     | 95  |

|---------------------------------------------------------|-----|

| 5.4.1.4 Controlador do Tempo de Teste                   | 95  |

| 5.4.1.5 Controlador das Portas do SoCIF                 |     |

| 5.4.1.6 Controlador de Interrupção                      | 96  |

| 5.4.1.7 Controlador da Comunicação Serial               |     |

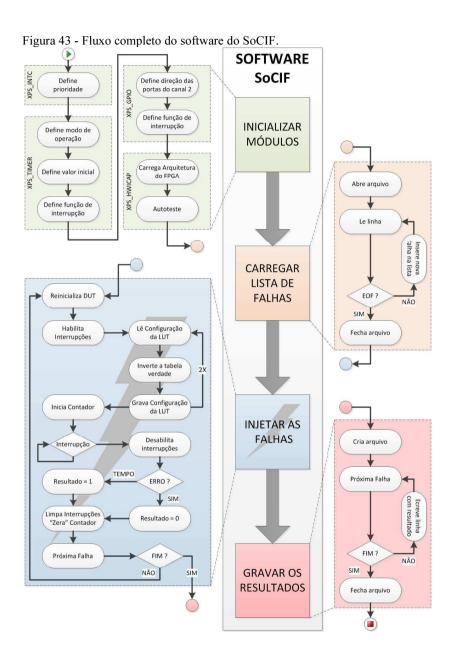

| 5.4.2 Funcionalidade – Software                         | 97  |

| 5.4.2.1 Inicializar Módulos                             | 99  |

| 5.4.2.2 Carregar Lista de falhas                        | 100 |

| 5.4.2.3 Injetar as Falhas                               |     |

| 5.4.2.4 Gravar os Resultados                            |     |

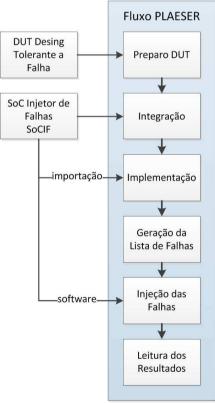

| 6 FLUXO DA PLATAFORMA DE EMULAÇÃO - PLAESER .           |     |

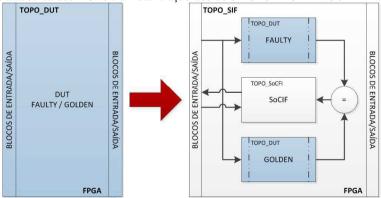

| 6.1 PREPARO DO DUT                                      | 104 |

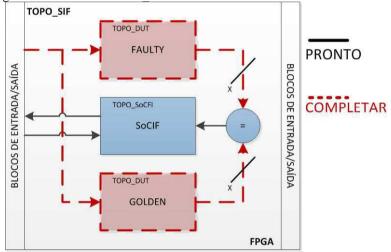

| 6.2 INTEGRAÇÃO                                          | 105 |

| 6.3 IMPLEMENTAÇÃO                                       |     |

| 6.4 GERAÇÃO DA LISTA DE FALHAS                          |     |

| 6.5 INJEÇÃO DAS FALHAS                                  |     |

| 6.6 LEITURA DOS RESULTADOS                              |     |

| 6.7 LIMITAÇÕES                                          |     |

| 7 RESULTADOS OBTIDOS                                    | 115 |

| 7.1 EXEMPLO – CONTADOR                                  | 115 |

| 7.1.1 Contador com TMR com a Lógica de Carry (Original) | 118 |

| 7.1.2 Contador sem TMR com a Lógica de Carry            |     |

| 7.1.3 Contador com TMR sem a Lógica de Carry            |     |

| 7.1.4 Contador sem TMR e sem a Lógica de Carry          | 127 |

| 7.2 PROCESSADOR LEON3 COM MONITOR DE BARRAMENTO         |     |

| 8 TRABALHOS FUTUROS                                     |     |

| 9 CONCLUSÃO                                             | 141 |

| REFERÊNCIAS                                             | 143 |

| APÊNDICE A - (PSEUDOCÓDIGO)                             |     |

| ,                                                       |     |

# 1 INTRODUÇÃO

Sistemas digitais estão presentes em todo lugar do nosso cotidiano, desde aparelhos domésticos como microondas e lavadoras de roupas até aplicações mais complexas como componentes de automóveis, sistemas de controle de aeronaves e equipamentos médicos. Esses sistemas digitais proporcionam mais produtividade e flexibilidade ao dia a dia, mas é de conhecimento comum que eles não estão livres de falhas. Algumas dessas falhas podem ser atribuídas a imperfeições durante a fabricação, enquanto outras são de natureza externa como defeitos de produção ou estresse causado pelo ambiente. Além disso, a miniaturização dos dispositivos aumenta a incidência de erros transientes (*Soft Errors*) e consequentemente diminui a confiabilidade do sistema (1). Logo, sistemas digitais utilizados em aplicações críticas ou ligados diretamente à segurança do ser humano requerem um alto grau de confiabilidade.

Tolerância a falhas em semicondutores ganhou mais importância desde que começaram a ser observadas anomalias no comportamento de aplicações espaciais (2). De lá pra cá, o constante avanço em tecnologias de fabricação fez com que os circuitos integrados (CI) atingissem a escala nanométrica. As características desses CIs, por exemplo, a dimensão de transistores e frequência de operação, os qualificam como potencialmente sensíveis a perturbações causadas por partículas encontradas na atmosfera terrestre ou até no nível do mar. A grande presença de circuitos integrados em diversas áreas faz com que a questão de tolerância a falhas transientes, que era uma preocupação restrita de aplicações críticas, principalmente espaciais, ganhe cada vez mais importância no desenvolvimento de dispositivos terrestres.

Nesse contexto, erros induzidos por radiação são uma ameaça crescente que acompanha o avanço da tecnologia de fabricação de CIs e por isso diversos esquemas de tolerância a falhas vêm sendo desenvolvidos para enfrentar esse desafio. Portanto, a avaliação dessas técnicas de tolerância a falhas diante do acontecimento de *soft errors* tem um papel fundamental. O uso de *benchmarks* ou de métodos convencionais de teste para análise de desempenho de sistemas não se aplicam para avaliação de confiabilidade. No entanto, é preciso mecanismos específicos que permitam observar o comportamento do sistema na presença de falhas (1). Contudo, esse tipo de avaliação só é viável se houver técnicas que consigam acelerar artificialmente o acontecimento dessas falhas, considerando que para dispositivos

eletrônicos os valores típicos da taxa de incidência de *soft erros* são na ordem de anos (3).

Injeção de falhas surge como uma solução viável e tem sido profundamente explorada em pesquisas e pela indústria para a análise de confiabilidade de sistemas (4). Diversas técnicas são utilizadas para prover experimentos através da injeção de falhas. Entre essas técnicas se encontra a injeção de falhas baseada em prototipação (5)(6) que utiliza um circuito reconfigurável FPGA (do inglês, *Field Programmable Gate Arrays*) para emular o acontecimento das falhas.

A pesquisa desenvolvida nesse trabalho propõe uma plataforma de emulação de *soft errors* que busca possibilitar a análise experimental de técnicas de tolerância a falhas aplicadas em projetos de circuitos críticos. A plataforma proposta, chamada PLAESER, utiliza recursos de reconfiguração específicos de FPGAs da Xilinx para permitir a injeção de falhas de forma menos intrusiva. O trabalho desenvolvido visa definir um fluxo que permita a análise experimental da técnica de tolerância a falhas ainda no início do projeto do circuito através de uma prototipação rápida. O quanto antes essa análise puder ser feita no projeto, menor será o tempo de locação de instalações para o teste com aceleradores de partículas que custam em média US\$ 100K por dia (7).

## 1.1 MOTIVAÇÃO

A inserção do Brasil no grupo de países auto-suficientes em relação à tecnologia aeroespacial, ou seja, com capacidade de desenvolvimento e do lancamento de satélites passa impreterivelmente pela formação de recursos humanos na área de efeitos causados por radiações. Essa formação é fundamental para possibilitar a fabricação nacional de circuitos robustos ao ambiente espacial e que atendam às normas já existentes como as da Agência Espacial Européia (ESA) para qualificação desses circuitos. Além disso, estudos sobre técnicas de tolerâncias aplicadas a dispositivos COTS (do inglês, Commercial Off The Shelf) são importantes para reduzir o impacto do embargo sofrido pelo Instituto Nacional de Pesquisa Espacial (INPE), e pelo Brasil em geral, na aquisição de componentes tolerantes a radiação. Esse embargo, devido à restrição governamental que regula o comércio internacional de armas (ITAR - International Traffic in Arms Regulation) faz com que a aquisição de dispositivos para área espacial seja custosa em tempo e dinheiro, e também, com tecnologias defasadas (8).

Nesse contexto, a plataforma de emulação de falhas proposta nesse trabalho pode ser empregada como uma das etapas do fluxo de

teste de projeto para o desenvolvimento nacional de circuitos eletrônicos tolerantes à radiação. Além disso, a constante miniaturização dos dispositivos concomitantemente ao aumento da frequência de operação e a diminuição da tensão de alimentação ampliam a suscetibilidade à radiação dos dispositivos. A previsão feita em (9) mostra uma barreira em que a taxa de erros devido aos efeitos da radiação inviabilizará a criação de CIs sem alguma técnica de tolerância, mesmo para aplicações operando em nível do mar. Dessa forma, a plataforma de emulação de falhas proposta nesse trabalho busca proporcionar ao desenvolvedor de CIs uma ferramenta para auxiliar na escolha de uma técnica de tolerância a falhas adequada, através de uma análise experimental guiada por um fluxo de prototipação rápida.

O uso de FPGAs tornou-se popular na verificação de circuitos de aplicação específica (3). Aliado a isso, a flexibilidade e a capacidade de reconfiguração parcial dos FPGAs motivaram o uso desse tipo de dispositivo na proposta da PLAESER para dar suporte à injeção de falhas em circuitos visando à implementação tanto para ASIC (do inglês, *Application Specific Integrated Circuit*) quanto para FPGAs.

#### 1.2 OBJETIVOS

O objetivo principal deste trabalho é realizar um estudo das técnicas de injeção de falhas existentes, além de definir uma plataforma de emulação de *soft errors*. Além disso, pretende-se que o uso da plataforma seja guiado através do fluxo proposto, que procura permitir a análise experimental de um circuito supostamente tolerante a falhas. Ainda, deseja-se que através da prototipação rápida seja possível aplicar o fluxo da plataforma PLAESER em etapas iniciais de projetos de circuitos tolerantes buscando diminuir o custo de projeto gasto com o tempo de locação de instalações para verificação através de radiação induzida.

Os objetivos específicos deste trabalho abrangem diversas áreas de conhecimento. Esses objetivos são:

- Aprender conceitos de suscetibilidade de circuito diante a radiação;

- realizar um levantamento das técnicas de injeção de falhas existentes e descobrir as suas características de forma a possibilitar a escolha de uma técnica para ser implementada;

- implementar uma plataforma de emulação de soft errors para dar suporte ao fluxo de injeção de falhas proposto;

- avaliar experimentalmente casos de teste utilizando a plataforma desenvolvida guiada pelo fluxo proposto;

- descrever o conhecimento adquirido durante o desenvolvimento do projeto com o objetivo de detalhar as adversidades encontradas devido a não documentação (proposital) de recursos existentes nos FPGAs da Xilinx.

### 1.3 ORGANIZAÇÃO DO TEXTO

O presente trabalho está organizado da seguinte forma: nas seções 2 e 3 são apresentados conceitos básicos e uma revisão das técnicas de injeção de falhas necessários para o entendimento deste trabalho; na seção 2 são abordados conceitos que caracterizam uma falha que se origina de um dos efeitos causados pela radiação. Na seção 3 são apresentadas diversas técnicas de injeção de falhas e algumas dessas são discutidas através do detalhamento de exemplos do estado da arte.

As seções 4, 5 e 6 apresentam o trabalho desenvolvido e as contribuições desse trabalho. A seção 4 mostra a investigação da arquitetura do FPGA utilizado para a emulação de falhas. Nessa seção são destacadas as dificuldades encontradas devido a não documentação de certos recursos do FPGA. O conhecimento adquirido nessa investigação é detalhado de forma a gerar uma documentação desses recursos.

A plataforma de emulação de *soft errors* (PLAESER) desenvolvida é descrita na seção 5. Cada componente que integra a plataforma PLEASER é detalhado de forma a ajudar o entendimento do fluxo de emulação de falhas proposto.

O fluxo proposto é seguido na seção 6 com o objetivo de descrever cada etapa. O mesmo fluxo é aplicado em casos de teste e seus resultados são mostrados na seção 7.

O direcionamento para trabalhos futuros e as conclusões são apresentadas nas seções 8 e 9. Na seção 8 são apresentadas diversas sugestões de melhorias a serem feitas para que a plataforma PLEASER possa se consolidar como uma ferramenta de análise experimental de técnicas de tolerância a falhas. Nessas sugestões se encontram inúmeras oportunidades de trabalhos de pesquisas que podem ser realizados.

## 2 CONCEITOS BÁSICOS

Conceitos básicos relacionados ao desenvolvimento deste trabalho são apresentados nesta seção. As definições relativas a confiabilidades utilizadas nesse trabalho estão de acordo com (10).

#### 2.1 CONFIABILIDADE

O serviço disponibilizado por um sistema se refere ao comportamento desse sistema quando utilizado pelo usuário. A especificação desse sistema define a sua função. O serviço entregue por esse sistema é dito correto quando esse serviço implementa exatamente a função para qual o sistema foi designado. O termo confiabilidade se refere à capacidade do sistema de prover um serviço de forma correta. Um defeito no sistema é o evento que ocorre quando o serviço entregue diverge do seu funcionamento correto, ou seja, um sistema é dito com defeito quando é incapaz de prover um serviço como especificado.

O sistema é regido por uma série de elementos internos que controlam os resultados gerados e a sequência desses resultados representa o serviço prestado pelo sistema. Um defeito no serviço corresponde à variação em um ou mais resultados dessa sequência. Essa variação é derivada de algum erro nos elementos que controlam o sistema. A causa do erro em um elemento do sistema é chamada de falha. Portanto, o erro é a manifestação de uma falha que provocou a interrupção na geração correta de resultados desse elemento. Esse erro conduzirá a um defeito no sistema se o elemento errôneo for requisitado durante a interrupção do seu funcionamento correto. É importante perceber que muitos erros não terão influência no resultado do sistema, ou seja, nem todos os erros acarretarão defeitos do sistema. A Figura 1 mostra a relação entre, falha, erro e defeito.

Figura 1 - Relação entre falha, erro e defeito.

Fonte: AVIZIENIS, A. et al. (2004) (10).

Com relação a sistemas que requerem uma alta confiabilidade, foram desenvolvidas diversas técnicas ao longo dos últimos cinquenta anos com o objetivo de atingir os requisitos de projeto de sistemas confiáveis. Essas técnicas podem ser divididas em quatro grandes grupos, que são:

- prevenção de falhas busca impedir a ocorrência ou a introdução de falhas através de metodologias de projeto e pela escolha de componentes com tecnologia apropriada;

- tolerância a falhas visa prover o serviço de forma correta mesmo com a presença de falhas e para isso utiliza técnicas como: mascaramento, confinamento, recuperação do sistema, tratamento da falha, entre outros;

- remoção de falhas verifica a presença de falhas com o objetivo de reduzir o número de ocorrências e a severidade das falhas;

- previsão de falhas estima o número atual e a incidência futura de falhas de forma a prever as consequências.

A especificação de sistemas que implementam diversas funções pode aceitar que o sistema permaneça operando mesmo que com defeito em algumas de suas funções. Dessa forma é mais interessante que o sistema continue operando ainda que de forma degradada, com limitações no serviço, mais lento ou em modo de emergência por exemplo. Nesses tipos de sistema, as técnicas de remoção e de previsão de falhas são mais aplicadas visando alcançar a qualidade de serviço e a disponibilidade. As técnicas de prevenção e tolerância são empregadas em sistemas críticos, onde defeitos no serviço entregue podem ser catastróficos.

Particularmente para o projeto de hardware em aplicações espaciais o aspecto de confiabilidade requer atenção especial. A confiabilidade nesses casos geralmente é relacionada à habilidade do circuito tolerar falhas induzidas pelo ambiente que podem conduzir a defeitos no sistema (11). Nesse contexto espacial, a falha é definida como um mau comportamento de um componente interno do sistema. A ativação da falha pode propagar para a saída desse componente, o resultado desse comportamento, e dessa forma, acarretar em um erro. Finalmente, um defeito ocorre se os resultados errados gerados por esse componente interrompem o correto funcionamento do serviço prestado pelo sistema.

Em aplicações espaciais críticas um defeito pode provocar um término prematuro da missão. Contudo, falhas e erros podem ser tolerados dependendo das especificações do sistema, desde que defeitos possam ser mascarados para evitar que aconteçam ou possam ser detectados de forma a colocar o sistema em um estado seguro. Nesse

contexto, diversas técnicas de tolerância se aplicam, mas antes disso é preciso analisar a origem das falhas.

As falhas podem ser classificadas de diversas formas, que dependem do critério considerado, como mostra a lista abaixo:

- momento na fase de desenvolvimento do sistema ou durante operação;

- origem interna ou externa ao sistema;

- fenômeno natural ou provocada por um ser humano;

- dimensão de hardware ou de software;

- objetivo maliciosa ou sem propósito malicioso;

- intenção deliberado a partir de uma decisão ruim ou não;

- forma acidental ou por mau uso;

- persistência transiente ou permanente.

No contexto de aplicações espaciais, as técnicas de tolerância geralmente visam falhas que ocorrem devido à radiação do ambiente em que o sistema opera. A persistência é o critério mais utilizado para classificação de falhas induzidas por radiação uma vez que basicamente todas as falhas desse tipo são externas ao hardware e acontecem de forma natural durante a operação. Os erros provenientes de falhas permanentes são chamados de *Hard Errors*, enquanto que, para falhas transientes os erros são chamados de *Soft Errors*, sendo que estes últimos geralmente são revertidos com a reinicialização do sistema.

# 2.2 RADIAÇÃO E SEUS EFEITOS

As falhas introduzidas no sistema pelo ambiente podem ser causadas não somente pela radiação, mas podem ser também de outra natureza. Por exemplo, falhas mecânicas podem ser originadas por vibrações e choques ou até alterações de temperatura ou pressão. Falhas elétricas podem ser causadas por interferência eletromagnética (EMI – *Electromagnetic Interference*) ou por descargas eletrostáticas (ESD – *Electrostatic Discharge*). Além disso, o envelhecimento do dispositivo pode também causar falhas. Contudo, a radiação é um dos aspectos naturais mais críticos para as tecnologias modernas de dispositivos eletrônicos (11). Dessa forma, será dada mais atenção à radiação.

A radiação pode ser generalizada como um grupo de partículas carregadas ou não que podem interagir com um dispositivo eletrônico através da troca de energia. No ponto de vista da presença de radiação, o espaço é o ambiente mais inóspito. Muitos tipos de radiação e de

partículas existem no espaço e são basicamente geradas por reações nucleares das estrelas. As partículas se movem facilmente no vácuo, mas quando chegam perto da Terra essas partículas se chocam com átomos e moléculas de oxigênio, nitrogênio e outros gases presentes na atmosfera. Dessa forma, as partículas perdem grande parte de sua energia e acabam dando origem a outras partículas. Logo, a atmosfera atua como um escudo natural da Terra que nos protege da radiação do espaço. Consequentemente, circuitos eletrônicos destinados a aplicações aeroespaciais estão mais expostos à radiação do que aqueles que operam em nível do mar, que estão sujeitos aos efeitos de partículas que não perderam toda sua energia.

Entre os diversos tipos de radiação presentes no espaço, as principais são os raios cósmicos, partículas subatômicas (mesons) e partículas alfa. As partículas com mais potencial para causar falhas presente nos raios cósmicos galácticos, também chamados de GCRs (do inglês, Galactic Cosmic Rays), são os núcleos de íons pesados altamente energizados. A origem desse tipo de radiação ainda não foi verdadeiramente comprovada (12). O outro tipo de radiação que pode causar o defeito de um sistema se chama meson que é produzido basicamente pela interação de partículas altamente energizadas dos raios cósmicos com a atmosfera terrestre. Por último, as partículas alfa são produzidas do decaimento de elementos radioativos, e possuem bem menos energia se comparadas com um íon pesado, e por isso. dificilmente conseguem vencer ao empacotamento de um CI a ponto de produzir uma falha. Contudo, outras partículas alfa podem ser produzidas pela interação de outras partículas, como nêutrons ou prótons, com o silício do dispositivo e dessa forma podem ser geradas dentro do próprio dispositivo e assim podendo acarretar em uma falha.

Todos esses tipos de radiação podem viajar pelo espaço e acabar sendo presas em campos magnéticos. As partículas que viajam perto do campo magnético em volta da Terra e ficam presas formam uma nuvem radioativa chamada de cinturão de Van Allen. As erupções gigantes de gases e plasma na superfície do Sol produzem uma distorção forte nos campos magnéticos em volta da Terra e com isso aumentando consideravelmente a absorção de raios cósmicos (11). A Figura 2 ilustra o cinturão de Van Allen.

As radiações que chegam ao nível do solo são geradas basicamente da interação dos raios cósmicos com a atmosfera terrestre. Existem fontes radioativas na Terra, como a crosta terrestre que emite partículas alfa, mas são insignificantes. As partículas primárias que compõem os raios cósmicos quando atingem a atmosfera perdem muito

da sua energia e produzem partículas secundárias que são divididas, principalmente, em três grupos: *hádrons*, *múons* e elementos eletromagnéticos (elétrons, pósitrons e fótons). Dependendo da sua origem essa partícula pode viajar por uma determinada distância até interagir com novos átomos ou atingir o solo. Mesmo que as partículas percam continuamente suas energias, o fato da miniaturização da tecnologia faz com que dispositivos eletrônicos sejam cada vez mais susceptíveis. Em (13) são mostrados alguns casos em que raios cósmicos causaram *soft errors* em aplicações operando na terra. Figura 2 - Ambiente radioativo espacial.

Ouando uma partícula primária incide em um material, ela percorre um caminho aleatório que é determinado pela colisão contra os núcleos do material que desviam essa partícula fazendo-a perder parte sua energia e produzir partículas secundárias. O termo frequentemente utilizado para descrever a energia transferida para o material, ou seia, a energia que a partícula perde a cada segmento da sua trajetória ao passar pelo material é representado pela sigla LET (do inglês, Linear Energy Transfered). A ionização é o mecanismo pelo qual certa carga é liberada internamente no material atravessado pela partícula. Essa ionização pode ser direta, ou seja, a partícula primária já é carregada ou indireta se a partícula primária não é carregada, mas a sua interação com esse material gera novas partículas carregadas. A ionização direta acontece principalmente devido a íons pesados, elétrons, pósitrons e partículas alfa, que quando entram no material podem arrancar elétrons de átomos neutros ou conceder elétrons para átomos ionizados, e dessa forma, provocar o movimento de carga ao longo da trajetória da partícula. A ionização indireta é derivada basicamente de nêutrons e fótons.

Quando um íon pesado atravessa um semicondutor, ele pode modificar momentaneamente a sua condutividade através da criação de pares elétron/lacuna. Isso pode ocasionar uma concentração de carga em uma determinada região. Caso essa região seja eletricamente ativa pode haver a alteração das características básicas do funcionamento do circuito.

A quantidade de energia depositada no circuito pela partícula define dois efeitos. O efeito cumulativo onde todas as partículas contribuem para uma dose ionizante total absorvida pelo circuito que é chamado de TID (do inglês, *Total Ionization Dose*). As partículas com baixo LET contribuem mais para esse efeito acumulativo uma vez que partículas com alto LET geram uma dose concentrada e causam um efeito diferente que é chamado de efeito de evento único ou SEE (do inglês, *Single Event Effect*). O SEE está relacionado ao fato de uma partícula de alto LET, por exemplo, um íon pesado, depositar grande quantidade de carga em um pequeno volume de material.

Diferentemente de TID e SEE que se referem à carga depositada no dispositivo, o dano por deslocamento DD (do inglês, *Displacement Damage*) ocorre quando uma partícula pesada adentra um semicondutor e consegue alterar o arranjo dos átomos da estrutura cristalina do silício causando um dano duradouro, afetando assim, propriedades das junções do semicondutor. Esse dano pode ser revertido através de técnicas especiais que utilizam temperaturas altas para fornecer energia suficiente para a rede cristalina se recombinar e voltar ao equilíbrio.

A Figura 3 mostra um resumo da relação entre a origem da radiação e o efeito causado nos componentes. A radiação do cinturão de Van Allen, que é composto de prótons e elétrons altamente energizados, contribui para todos os tipos de efeitos, igualmente aos prótons energizados provenientes das erupções solares. Os raios cósmicos são compostos de íons altamente energizados capazes de induzir SEE, mas que são raros e não possuem quantidade suficiente para contribuir para a degradação do componente (12).

#### 2.3 MODELOS DE FALHAS

Os efeitos físicos do impacto da radiação em materiais são fenômenos muito complexos e requerem modelos matemáticos e estatísticos específicos. As simulações desses modelos são altamente custosas em tempo devido à complexidade e à quantidade de informação envolvida. Esse quadro agrava extremamente quando consideramos circuitos construídos com as tecnologias modernas que integram bilhões de transistores. Contudo, comportamentos comuns entre os circuitos afetados podem ser percebidos. Esses comportamentos estão ligados ao funcionamento do circuito e não aos princípios físicos do fenômeno da radiação. Nesse contexto, são introduzidos os modelos de falhas que estão relacionados ao comportamento do circuito, ou melhor, à mudança de comportamento quando o circuito é afetado por radiação.

O endurecimento de CIs comerciais, em geral, perante os efeitos duradouros, tem melhorado nos últimos anos como descrito em (12). O contrário tem acontecido com a sensibilidade dos dispositivos diante aos efeitos radioativos transientes, que tem se agravado devido à miniaturização da tecnologia de dispositivos. Dessa maneira, serão apresentados os modelos de falhas do tipo SEE. Esses efeitos podem ser divididos entre *Hard Errors*, que correspondem a falhas destrutivas, e *Soft Errors*, onde o efeito temporário da falha muitas vezes desaparece, principalmente, por meio da simples reinicialização do dispositivo.

- Soft Errors

- Single Event Upset (SEU)

- o Multiple Cell Upset (MCU)

- Single Event Transient (SET)

- Single Event Functional Interrupt (SEFI)

- Hard Errors

- o Single Event Latch-up (SEL)

- Single Event Gate Rupture (SEGR)

O efeito chamado de SET é causado quando uma partícula atinge um circuito combinacional do dispositivo. Durante um período de pico/nano segundos a carga coletada pelo campo elétrico injeta elétrons ou lacunas dependendo da polarização do campo elétrico do transistor. Esse fenômeno pode causar um *glitch* na tensão de saída do transistor que é chamado de SET. A quantidade mínima de carga para induzir um SET é chamada de carga crítica. O comportamento lógico de um SET é definido como uma transição dupla  $(0 \rightarrow 1 \rightarrow 0)$  ou  $(1 \rightarrow 0 \rightarrow 1)$ . A Figura 4 apresenta um exemplo de um SET onde mostra um circuito lógico atingido por uma partícula que ocasiona um *glitch* na saída da porta lógica do centro da figura. O efeito do SET se propaga para a saída do circuito.

Figura 4 - Exemplo de um SET.

O efeito causado por uma partícula que atinge um elemento de memória e inverte o seu estado é chamado de SEU. SEUs não são considerados permanentes porque uma vez que a próxima operação de gravação for executada o valor errado será sobrescrito. Contudo, em casos que o elemento de memória é utilizado somente para leitura pelo sistema então o efeito desse SEU é permanente. Dependendo do tipo do dispositivo, SEUs também podem ser obtidos quando o efeito de um SET se propaga até o próximo elemento de memória e acaba sendo armazenado. Quando mais de um SEU ocorre em um circuito então isso é chamado de MCU e nesses casos se os múltiplos elementos de memórias afetados fazem parte de um registrador maior que armazena uma palavra então pode ser chamado de MBU (do inglês, *Multiple Bit Upset*).

O efeito SEFI acontece quando a partícula atinge um elemento de controle funcional do dispositivo de forma que o seu efeito acaba sendo global. Os SEFIs geralmente estão relacionados a erros temporários que afetam ao sinal de reinicialização ou sinal que desabilita a escrita de uma memória interrompendo a sua funcionalidade.

Os efeitos destrutivos de SEEs, que são SEL e SEGR, podem aumentar o fluxo de corrente ou até causar um curto-circuito e dessa forma gerando um sobreaquecimento no dispositivo e podendo até queimá-lo.

#### 2.4 CIRCUITOS RECONFIGURÁVEIS

Os circuitos reconfiguráveis, no caso os FPGAs, fazem parte de uma família de dispositivos utilizados para implementação de hardware personalizável. A ação de reconfigurar o FPGA significa mudar a sua funcionalidade de forma a suportar uma nova aplicação. A possibilidade de ter um hardware configurável é o que faz os FPGAs serem tão populares. Softwares que podem ser seccionados para serem executados de forma paralela fazem do FPGA uma ótima solução para implementar o algoritmo em hardware de forma a melhorar o tempo de execução. Em computação de alto desempenho, principalmente no processamento de imagens em que o paralelismo dos algoritmos pode ser explorado se implementado em hardware, os FPGAs são muito visados (14). Dada a capacidade de lógica que pode ser sintetizada pelos modelos de FPGAs atuais, um SoC (do inglês, System-on-a-Chip) inteiro pode ser implementado dentro desses dispositivos reconfiguráveis. Além disso, os maiores fabricantes de FPGAs lançaram SoCs customizáveis com processadores ARM integrados em um FPGA (15)(16)(17).

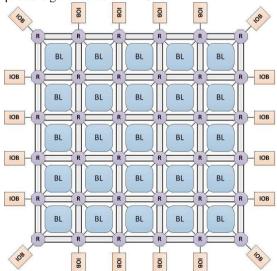

Figura 5 - Arquitetura genérica de um FPGA.

A arquitetura genérica de um FPGA é mostrada na Figura 5. Os FPGAs possuem três elementos básicos que são os Blocos Lógicos (BL), os Blocos de Entrada/Saída (IOB) e os recursos de comunicação (R). Os BLs são os blocos principais do FPGA e contém geradores de função lógica e elementos de armazenamento. Os BLs são configurados

para implementar o circuito combinacional/sequencial. O IOB (do inglês, *Input/Output Block*) tem a função de interconectar um sinal interno em um pino do encapsulamento do FPGA. Cada pino do FPGA possui um IOB correspondente que pode ser configurado para determinar o sentido da porta se é de entrada, saída ou bidirecional. Os recursos de interconexão (R) são como roteadores programáveis que permitem a conexão entre BLs e IOBs.

O arquivo de configuração do FPGA é chamado de *bitstream*. O carregamento do *bitstream* no FPGA é que define a sua funcionalidade como ilustra a Figura 6. Os tipos de FPGAs mais comuns são os *antifuse*, que são programados somente uma vez, e os baseados em memórias, que podem ser do tipo SRAM ou Flash (18). Considerando isso, os trabalhos sobre efeitos de evento único (SEE) em FPGA geralmente utilizam o termo SEU mesmo quando outros efeitos são analisados como, por exemplo, em (19). É importante ressaltar aqui que esse trabalho utiliza a reconfiguração da memória de configuração do FPGA para inverter a lógica de elementos do circuito com o objetivo de emular SETs.

Figura 6 - Memória de configuração do FPGA.

Os arquivos de configuração dos diversos fabricantes de FPGAs permanecem obscuros por motivos políticos, de segurança e principalmente, devido à propriedade intelectual dos dispositivos. Esses motivos são exaustivamente discutidos em (20).

# 3 INJEÇÃO DE FALHAS (TRABALHOS RELACIONADOS)

A injeção de falhas em hardware é peça fundamental na análise do comportamento de circuitos na presença de falhas, pois é uma abordagem amplamente aceita (3). As técnicas de injeção de falhas buscam providenciar informações sobre a confiabilidade do circuito sendo testado, aqui chamado de DUT (do inglês, *Design Under Test*). Essas informações podem ser sobre: a) validação do cumprimento dos requisitos de confiabilidade; b) detecção de pontos fracos nas técnicas de tolerância a falhas adotadas; c) previsão do comportamento do DUT na presença de falhas.

O termo hardware utilizado juntamente de injeção de falhas, como em *injeção de falhas em hardware*, está relacionado a todas as técnicas que buscam simular o efeito da variação do comportamento do dispositivo na presença de uma falha. Entre essas técnicas existem aquelas aplicadas, principalmente, a sistemas processados, em que alterações no software são feitas com o objetivo de simular uma má execução do sistema devido ao acontecimento de uma falha no hardware do dispositivo. Dessa forma, é importante haver uma distinção entre injeção de falhas para a análise do comportamento do hardware e do software, sendo que este último está fora do escopo desse trabalho.

As técnicas de injeção de falhas não se limitam a forma de injeção propriamente dita. As técnicas envolvem o processo completo necessário para a injeção das falhas. Isso engloba todo o ambiente requerido para inicialização do DUT, a seleção da carga de trabalho apropriada, a captura dos dados pertinentes ao comportamento com falha do DUT, a comparação com os dados do comportamento do DUT livre de falhas, a classificação dos efeitos sofridos pelo DUT e o monitoramento de todo o processo.

O método de injeção de falhas depende do tipo de DUT que está sendo testado. No caso de memórias, o efeito a ser analisado pela injeção de falhas será predominantemente SEUs, enquanto SoCs, por serem circuitos mais complexos, requerem uma injeção de falhas mais específica. Outro fator a ser considerado é a possibilidade de se provocar falhas reais (físicas) no dispositivo ou se somente modelos de falhas (lógicas) serão aplicados. O nível de abstração do tipo de falhas a serem injetadas está relacionado diretamente ao DUT que pode ser um COTS, um protótipo ou um modelo do projeto. A intrusão no DUT é outra questão levantada durante a escolha do método de injeção de falhas, uma vez que a análise deve ser feita com o circuito operando o mais próximo possível do que será a sua aplicação final. Finalmente, o

resultado esperado devido à técnica de injeção escolhida irá avaliar a robustez do circuito perante a presença de falhas. Tipicamente, no contexto de radiação, os resultados das campanhas de falhas são apresentados em valores de FIT (do inglês, *Failures In Time*) que representa o número de vezes que o circuito apresentou defeito em um bilhão de horas  $(10^9h)$  de operação.

Essa seção faz um apanhado das diversas técnicas de injeção de falhas existentes. As técnicas são apresentadas em dois grandes grupos, ou seja, as que trabalham com injeção física de falhas e as técnicas com abordagem no âmbito do mau comportamento funcional causado pela falha. Entre essas técnicas é dada uma atenção especial à emulação de falhas que foi utilizada para o desenvolvimento desse trabalho.

## 3.1 TÉCNICAS DE INJEÇÃO FÍSICA DE FALHAS

Os métodos de injeção física de falhas utilizam fontes externas para permitir ensaios com radiação, ruídos eletromagnéticos e envelhecimento dos CIs. O objetivo desses testes é analisar a robustez de COTS ou qualificar um protótipo como "endurecido" perante os efeitos causados pela radiação. Alguns dos métodos de injeção física de falhas são mostrados a seguir.

## 3.1.1 Método por Radiação

A radiação cósmica é a fonte principal de SEE em CIs, portanto, realizar testes com o dispositivo em elevadas altitudes ou até no espaço é a forma mais realística de avaliar a sensibilidade à SEE dos CIs. Considerando a baixa probabilidade de erros, seriam necessárias centenas de milhares de amostras do DUT para se obter uma medição válida. Portanto, o tempo e o custo dessa abordagem as tornam inviáveis, principalmente para projetos que visam o lançamento do produto no mercado. Dessa forma, aceleradores do efeito radioativo são utilizados para qualificar os produtos. Esses aceleradores se encontram em instalações específicas para esse tipo de teste e realizam testes que duram horas ou dias em poucas amostras do DUT (3). Uma lista dessas instalações é encontrada em (21).

Nesses tipos de teste são utilizados diversos tipos de partículas com valores de LET distintos visando causar efeitos diferentes. Os tipos de partículas e os valores de LET típicos utilizados para gerar SEE, TID e DD são detalhados em (12). Muitos desses valores que caracterizam o teste do circuito são padronizados de acordo com a aplicação final do

dispositivo. Essa padronização é geralmente feita por agências espaciais ou comitês como o JEDEC que criou o padrão JESD89 (21), onde define os requerimentos e procedimentos para teste da taxa de *soft errors*, chamada de SER (do inglês, *Soft Error Rate*), para CIs utilizados em aplicações terrestres, ou seja, desde aeronaves até dispositivos operando na superfície da Terra. Experimentos realizados com FPGAs da Xilinx com características descritas no padrão JESD89 são apresentados em (22).

### 3.1.2 Método por Raios Laser

A injeção de falhas através de raios laser é semelhante ao método que utiliza íons pesados no sentido em que o feixe é aplicado diretamente na superfície do silício. No entanto, o raio laser é muito mais preciso, e dessa maneira é possível injetar falhas em lugares específicos de forma muito mais controlada. A incidência do raio laser no silício pode causar efeitos semelhantes àqueles provocados por partículas dos raios cósmicos. Esse método é geralmente associado à mudança do estado de elementos do circuito, para o teste do efeito do tipo SEU. Os trabalhos (23) e (24) mostram os resultados obtidos através da análise de SEE com a injeção física de falhas por raios laser em FPGAs.

Com a ajuda de um microscópio especial, a utilização de raio laser para injeção de falhas provê alta acessibilidade no sentido de localizar elementos do circuito de forma não intrusiva. Desse modo, a injeção de falhas por raio laser utiliza equipamentos mais baratos do que instalações para ensaios de radiação. Além disso, o método por raios laser precisa de um ambiente bem mais simples para a injeção de falhas, pois, não é necessário isolar o DUT, por exemplo, para que os componentes da periferia do DUT que não estão sendo testados não sofram as perturbações causadas pela radiação, o que comprometeria o resultado da análise.

## 3.1.3 Método de Injeção por Pinos

Diferentemente das outras técnicas de injeção física de falhas apresentadas, o método por indução de valores nos pinos do DUT requer contato físico entre a plataforma de teste e o DUT. O método busca replicar o efeito de uma falha natural através da mudança forçada do valor lógico de um pino do CI. Considerando a complexidade de sistemas modernos a injeção de falhas por pinos fica muito limitada

quanto ao poder de acessibilidade do método. Dessa forma, ela é mais utilizada para analisar diversos efeitos nos terminais do circuito.

O método de injeção de falhas através dos pinos muitas vezes é empregado por ferramentas de teste em conjunto com outras técnicas com o objetivo de ampliar os resultados. Soluções como MESSALINE, MARS, FIST, RIFLE descritas em (25) empregam funcionalidades do método de injeção de falhas nos pinos do circuito.

## 3.2 TÉCNICAS DE INJEÇÃO DE FALHAS NO NÍVEL LÓGICO

Os métodos de injeção física de falhas disponibilizam valores realísticos da taxa de SER e são amplamente utilizados para qualificação de dispositivos como "endurecidos" para aplicações críticas em ambientes hostis como o espaço. Contudo, as instalações com aceleradores de nêutrons, por exemplo, cobram na faixa de trezentos até mil dólares por hora de exposição (26), ou seja, injeção física de falhas é extremamente cara e dessa forma é preciso soluções de análise que possam ser aplicadas mais cedo no projeto de circuitos robustos.

Os métodos de injeção de falhas no nível do funcionamento do circuito exploram recursos lógicos disponíveis para poder inserir o efeito que uma falha em hardware provocaria. Geralmente, esses recursos lógicos têm finalidades diferentes do que a da injeção de falhas, por exemplo, o padrão 1149.1 da IEEE que provê acesso a cadeias de scan do circuito ou sistemas processados com recursos de depuração OCD (do inglês, On-Chip Debug) que permitem a observação de elementos de memória internos do processador (contadores, registradores, etc.). No caso de dispositivos com hardware programável, os recursos reconfiguráveis que permitem o acesso e o controle de nodos do dispositivo podem ser utilizados para injeção de falhas.

### 3.2.1 Software-Implemented Fault Injection (SWIFI)

A sigla SWIFI (do inglês, Software Implemented Fault Injection) está diretamente ligada à execução de partes específicas de software que modificam elementos internos (acessíveis pelo usuário) provocando o efeito de uma falha ocorrida no hardware. O método SWIFI está relacionado principalmente a sistemas processados, onde de alguma forma o software da aplicação normal é interrompido para a execução de um código de injeção de falhas que deve alterar um elemento, como um registrador, um dado da memória, ou até uma instrução da aplicação. SWIFI aparece também na análise do comportamento do DUT na

ocorrência de problemas de comunicação ou interação com outros sistemas, como, por exemplo, mensagens repetidas/faltando ou com informações erradas, falhas na leitura da memória, entre outros.

Esse tipo de injeção de falha pode ser dividido quanto ao momento da injeção, que pode ser em tempo de compilação ou durante a execução. Em tempo de compilação, modificações na imagem do software são feitas e quando são executadas, ativam a falha que simula o efeito de uma perturbação ocorrida no hardware. Esse tipo de falha não precisa de código adicional para ser executada e é geralmente utilizada para emular falhas permanentes. No caso de falhas injetadas durante a execução, mecanismos de disparo são utilizados para avisar o momento da injeção da falha. Temporizadores ou instruções específicas (de armadilha) no código são utilizadas para a interrupção da aplicação e execução da tarefa de injeção de falha.

Uma avaliação de sistemas baseado em COTS para aplicações espaciais foi desenvolvida em (27). Nesse trabalho o COTS era a placa CETIA com dois processadores PowerPC 750 rodando LynxOS. O trabalho apresenta a utilização da ferramenta XCEPTION para emular o efeito de SEUs no sistema. A ferramenta XCEPTION explora os recursos avançados de monitoramento de desempenho e de erros presentes em processadores atuais e utiliza os mecanismos de exceção do próprio processador para o disparo das falhas. Diferentes ferramentas, como: FERRARI, que utiliza temporizadores para disparar uma rotina de injeção de falhas; FIAT, que pode corromper mensagens, atrasar tarefas ou terminá-las abruptamente; FTAPE, que adiciona drivers de injeção de falhas no sistema operacional; entre outras são apresentadas em (25) e fazem parte das que implementam falhas em hardware no nível de software.

## 3.2.2 Injeção de Falhas Baseada em Simulação

A injeção de falhas baseada em simulação utiliza um modelo do sistema a ser analisado. Os modelos de simulação utilizam descrições de hardware como VHDL e Verilog ou modelagens em mais alto nível de abstração como SystemC. No método de simulação, as falhas podem ser injetadas pela ferramenta de simulação ou pela alteração da descrição do modelo do hardware. Nesse último caso podem ser adicionados "sabotadores" no modelo, que são componentes específicos com o único propósito de injetar falhas, ou o emprego de componentes "mutantes" que contém a descrição do funcionamento livre e na presença de falha. O outro método utiliza recursos ou adapta as ferramentas de simulação

de forma a utilizar comandos para controlar sinais internos do modelo do sistema. Esse método é dependente da funcionalidade dos comandos do simulador, no entanto, não há necessidade da alteração do modelo de hardware.

Em (28), um modelo do processador LEON3 da Gaisler usado pela ESA (do inglês, *European Space Agency*) descrito em SystemC é utilizado para a simulação de falhas. Esse modelo descrito em SystemC tem seu nível de abstração elevado para o modelo TLM (do inglês, *Transaction Level Modeling*) que é baseado em transações. No modelo TLM são colocados mutantes que são utilizados para simular os efeitos de falhas em seções da memória (pilha, instruções, dados, etc.) do processador.

A ferramenta MEFISTO apresentada em (29) utiliza sabotadores, mutantes e comandos de simulação para fazer análise mais apurada do comportamento de falhas em modelos descritos em VHDL. Outras ferramentas como VERIFY que propôs uma extensão da descrição VHDL para adicionar recursos para injeção de falhas, HEARTLESS que desenvolveu sua própria ferramenta para a simulação de falhas permanentes e transientes, entre outros trabalhos que compõem o grupo de injeção de falhas baseado em simulação são apresentados em (25).

## 3.2.3 Injeção de Falhas Utilizando Recursos de Depuração

Processadores atuais possuem recursos específicos para o suporte a testes e também para depuração. Esses recursos, chamados de OCD, habilitam a injeção de falhas e a observação dos efeitos externamente ao processador de forma rápida e eficiente.

A ferramenta FIMBUL (do inglês, Fault Injection and Monitoring Using Built in Logic) desenvolvida em (30) utiliza o TAP (do inglês, Test Access Port) do OCD do processador Thor para a injeção de falhas. A TAP permite o acesso às cadeias de scan interna e da periferia do processador Thor. Dessa forma, as falhas transientes são injetadas em qualquer local em que as cadeias têm acesso. Nesse mesmo trabalho é apresentada uma comparação entre as ferramentas FIMBUL e MEFISTO onde é mostrado que a técnica por simulação (MEFISTO) tem uma cobertura de erros levemente superior. No entanto, a ferramenta FIMBUL que utiliza a técnica SCIFI (do inglês, Scan Chain Implemented Fault Injection), mostrou ser cem vezes mais rápida.

O trabalho apresentado em (31) propõe alterações na infraestrutura de depuração (OCD) com o objetivo de possibilitar a injeção de falhas para dar suporte à verificação de mecanismos de

tolerância a falhas. O OCD orientado à injeção de falha é chamado de OCD-FI (do inglês, OCD-Fault Injection) é baseado no padrão NEXUS. O OCD-FI proposto consiste em um hardware adicional que insere automaticamente falhas na ocorrência de condições de disparo, ou seja, sem a necessidade de comandos para o OCD. O endereço da instrução que disparará a injeção da falha é gerado aleatoriamente entre um dos valores presentes no espaço de endereçamento da memória de instruções. O mesmo acontece com o endereço da memória de dados que terá o valor do dado alterado quando a injeção da falha tiver sido disparada. Após as falhas terem sido injetadas os resultados são recuperados depois da conclusão de todos os experimentos.

### 3.2.4 Injeção de Falhas por Emulação

A prototipação de hardware baseada em FPGAs ficou popular na verificação de ASICs, e mais recentemente é explorada para injeção acelerada de falhas. O termo "emulação" nesse contexto está relacionado à prototipação do circuito a ser analisado em FPGAs. É importante ressaltar que muitas das técnicas que empregam o FPGA para a emulação de falhas, utilizam-no somente como meio de injeção de falhas, e depois o circuito analisado pode ser implementado em alguma outra tecnologia, como ASIC por exemplo.

A injeção de falhas requer habilidades de controle e observação elevadas. A controlabilidade é alcançada através do recurso de reconfiguração do FPGA que permite o acesso a memória de configuração do circuito. Outra forma de emulação de falhas consiste na adição de blocos de hardware, chamados de "instrumentos", no protótipo para dar suporte à injeção.

Um dos primeiros trabalhos utilizando FPGA para a emulação de falhas é apresentado em (32). Esse trabalho implementa falhas permanentes do tipo *stuck-at* conectando sinais a valores constantes. Nesse caso, para cada falha injetada o circuito era sintetizado novamente e consequentemente o *bitstream* tinha que ser recarregado no FPGA para uma nova emulação. Logo, não era muito eficiente.

Entre os métodos mais novos que utilizam FPGAs para emulação de falhas dois tipos de abordagens podem ser percebidos. A primeira, chamada de "instrumentação", insere lógica, de alguma maneira no circuito, com o objetivo de aumentar o controle e o poder de observação do DUT durante a sua execução. A segunda utiliza recursos de reconfiguração parcial existente para disponibilizar o controle e poder

de observação necessária para a emulação. Exemplos dessas duas abordagens de emulação de falhas são apresentados a seguir.

### 3.2.4.1 Instrumentação

O termo instrumentação nesse contexto significa introduzir modificações na descrição HDL (do inglês, *Hardware Design Language*) do circuito com o objetivo de dar suporte à emulação de falhas.

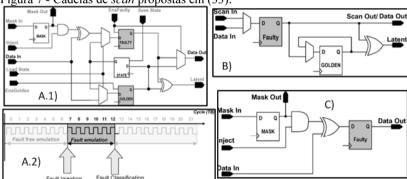

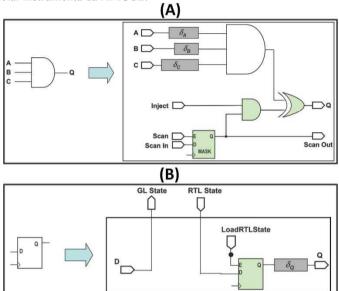

O trabalho desenvolvido em (33) apresenta um sistema de análise de SEUs totalmente autônomo, ou seja, sem a necessidade de interação com um hospedeiro para controlar a emulação. A instrumentação desenvolvida nesse trabalho se refere a cadeias de scan específicas para a injeção de falhas. No caso, a cadeia de scan é formada por todos os registradores do DUT. São apresentadas três tipos de células da cadeia de scan com características de otimização diferentes, como mostra a Figura 7. O sistema apresentado no trabalho carrega as falhas a serem injetadas através da cadeia de scan. O teste do DUT é dividido em ciclos de relógio, dessa forma, para cada falha existe um número do ciclo de relógio correspondendo ao momento em que a falha será injetada. As falhas são injetadas em todos os registradores e em todos os ciclos de relógio do total de ciclos do teste. A célula apresentada em A.1 permite armazenar o estado anterior do registrador antes da falha ser injetada. Dessa forma, o sistema de injeção pode recuperar o estado do DUT ao invés de reiniciar o DUT e esperar o número de ciclos de relógio até o momento de injeção. Quando a célula A.1 é utilizada, o DUT opera através dos registradores FAULTY e GOLDEN em ciclos de relógios alternados (multiplexado em tempo). Dessa forma, existe um DUT GOLDEN e um DUT FAULTY sem a necessidade de replicar todo o circuito. A existência desses dois DUTs permite que a emulação possa ser interrompida assim que o efeito da falha injetada desapareça e também possibilita classificar se o efeito da falha permanece latente ao final dos ciclos de relógio da emulação. A forma de onda A.2 da Figura 7 mostra o número de ciclos (5) de relógio utilizados para a emulação de uma falha que começa no ciclo sete e em 12 é possível notar que falha virou um defeito ou seu efeito desapareceu.

A cadeia de *scan* formada pelas células do tipo B da Figura 7 é utilizada para reduzir o impacto na ocupação do FPGA causada pelas células do tipo A.1. Nesse tipo de cadeia de *scan* (B) o sistema de emulação de falhas que fica no hospedeiro gera uma lista com todos estados dos registradores do DUT para cada ciclo de relógio e armazena em uma memória externa da placa com o FPGA. O estado dos

registradores é recuperado dessa memória externa, o que corresponde ao momento da injeção da falha, ou seja, isso é feito para todos os ciclos de relógio do teste e para cada registrador onde a falha será injetada. No início da campanha um teste completo é executado sem a injeção de falha para armazenar o resultado final no registrador GOLDEN. Com isso, ao final dos testes com injeção de falha os registradores FAULTY e GOLDEN são comparados para poder classificar as falhas que não causaram defeito como latente ou silenciosas.

A célula apresentada em C na Figura 7 busca otimizar ainda mais a ocupação do FPGA e ainda reduzir a necessidade de uma memória externa. Para cada injeção de falha, a cadeia dos registradores MASK é carregada com o padrão que define onde a falha será injetada. Como o estado não é armazenado o teste é executado inteiramente para cada injeção de falha. Nesse caso, somente as saídas do DUT são analisadas, o que permite classificar o efeito das falhas como as que provocaram defeito ou não.

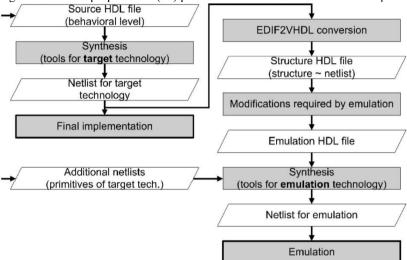

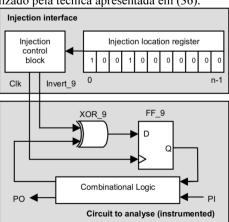

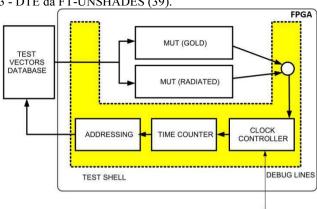

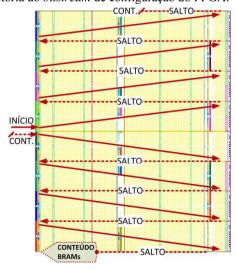

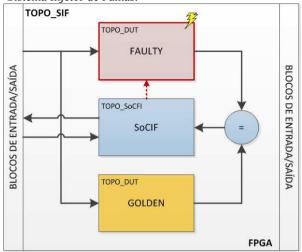

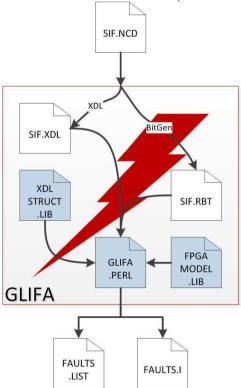

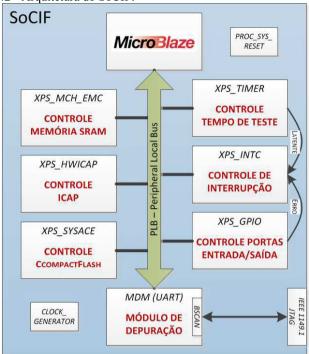

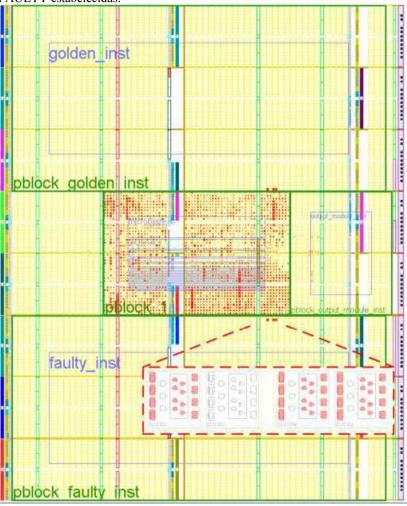

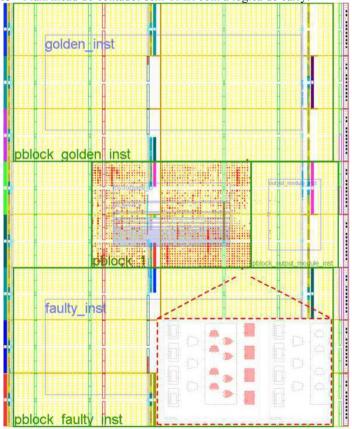

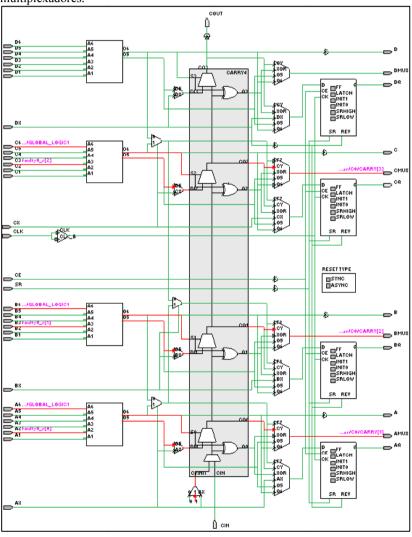

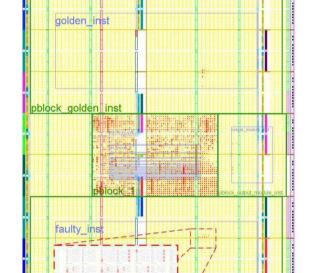

Figura 7 - Cadeias de *scan* propostas em (33).